隨著NAND Flash的製程發展與容量的進步,錯誤校正對於確保NAND Flash的資料可靠度而言,比起以往任何時候都更為重要。一般來說對於大尺寸的快閃記憶體而言,BCH(Bose, Ray-Chaudhuri, Hocquenghem)碼已被廣泛地應用,然而因為Flash單位儲存及存取容量增加的特性,使得BCH編碼長度也必須大幅度地增加。

因此,Flash控制器在設計複雜度上大幅提升,而這也意味著BCH已不敷使用。在這樣的條件下,讓許多人開始尋找其替代方法,因而選擇了LDPC(低密度奇偶校驗)。比起既有的錯誤更正碼,LDPC對於較長的編碼長度具備極佳的錯誤更正能力,使得LDPC錯誤檢查碼技術顯得越來越重要。

相信許多人對ECC(Error-correcting Code)仍相當陌生,因此我們先就ECC做些簡單的說明。當資料被寫入到NAND Flash內部時,控制器同時會產生一組校正碼與資料一起存入,資料從NAND讀出來若發生錯誤,控制器會透過校正碼更正資料。若發生的錯誤也無法透過ECC校正碼成功修正回來,這筆資料就會被當作無法修護(Uncorrectable)的資料。

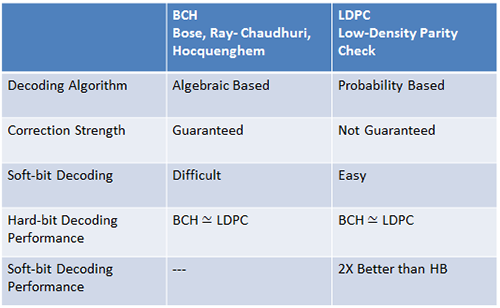

各種ECC設計都有其優勢,儘管校正能力(Correction Capability)很重要,同時也要顧慮到ECC電路設計的大小與耗電,甚至針對控制器製程的特性,研發出更具有優勢的NAND ECC架構。

LDPC錯誤更正碼可以使得快閃記憶體掃描週期大幅提升,可以在每頁中糾正更多錯誤,來維持快閃記憶體更長的壽命,這樣一來就能使快閃記憶體在耐久度使用上大幅提升。

目前的LDPC錯誤檢查碼尚無可以任意調整Parity Size的通用碼或方法,應用在NAND Flash控制器中的錯誤更正碼Parity Size必須小於NAND Flash Device所提供容許儲存Parity的空間。因此,群聯科技在PS2251-11(表1)提供一種可程式化的LDPC解碼器解決方案,並使用可依據輸入資料而選擇不同運算精度之解碼器,以達到較佳的讀取速度和電源付出。

|

| 表1 群聯電子USB控制器搭載的兩種ECC IP比較 |

一個採用LDPC錯誤更正碼的NAND Flash控制器會因為新製程的NAND Flash Device改變Parity空間大小而無法使用,必須重新設計與製造控制器,造成時間與成本增加。群聯科技PS2251-11所搭載的ECC IP則提供一個可程式化LDPC解碼器解決方案;把LDPC解碼程序儲存在NAND Flash Device中,並有BCH保護錯誤位元發生,當電源啟動時,由NAND Flash Device載入解碼程序至LDPC解碼器。

另外,在LDPC的系統當中,訊息進入系統會透過編碼器(Encoder)編出Parity,等訊息跟Parity通過通道(Channel)後,會得到受汙染的message_n跟parity_n,此時再把message_n跟parity_n送入Checker做運算,即可得到Syndrome幫助解碼,使得編碼器的運算電路在Checker中重複利用,藉此達到電路優化且有效減少電路邏輯閘數(Gate Count)之目的。

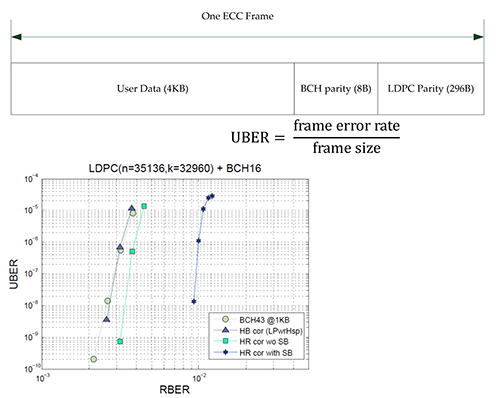

圖1為一個保護4KB為單位的LDPC錯誤更正碼其更正能力與BCH錯誤更正碼之比較。

HB cor:是一個使用較少運算精度的解碼器,雖然更正能力較低,但是可達到Low Power & High Speed。可採用演算法二實現成2-bits運算精度的硬體。

|

| 圖1 保護4KB為單位的LDPC錯誤更正碼其更正能力與BCH錯誤更正碼之比較 |

HR cor:是一個使用充足的運算精度的解碼器,更正能力接近使用浮點運算;當僅從NAND Flash讀取Hard Bit(HB)時,在UBER=10-8更正能力可優於BCH 28%;當可從NAND Flash讀取Soft Bit(SB)時,在UBER=10-8更正能力可優於BCH 368%。可採用演算法一實現成6-bits運算精度的硬體。

隨著NAND Flash容量快速地增加,錯誤檢查與更正技術也必須相對地提升,就目前趨勢觀察,LDPC在市場上的使用率日益增加,再加上USB 3.0其高速資料存取與整體效能皆為推動USB 3.0產品的重要關鍵。PS2251-11所提供的LDPC錯誤更正碼能夠符合現今市場需求,不僅改善Flash讀取速度與整體電路的電源消耗,更大幅提高了產品的資料可靠度。

(本文作者為群聯電子技術長)