隨著資料速率增加,在電氣系統中,系統元件的共模(Common Mode)性能越來越受到關注。許多論文已經分析了系統的各個部分和量化的共模性能。隨著關注的增加,共模缺陷已被量化,而訊號完整性社群對這些缺陷的了解也增加。

本文藉由將共模量化工作擴展到通道建模和系統性能中,了解共模對系統性能的影響。系統設計人員的最終目標是在給定的一組包括最大限度減低成本和複雜性的限制條件下優化系統性能,使用模擬和分析來研究系統性能並確定怎樣的共模性能是夠好的。

共模性能攸關系統表現

人們普遍認為理想的差分通道(Differential Channel)具有理想的共模性能。當然,沒有通道具備完美的共模性能。通用的簡化模型已經應用於眾多論文中,顯示共模機制會影響系統性能。這項研究將在現實通道中檢測共模缺陷對於系統性能的底線影響。

有些討論是探討何種共模性能是最理想的,對大多數共模指標有著較強的共識。通道的理想共模性能將會是零差模到共模轉換(Zero Differential to Common Mode Conversion)、整個通道具有匹配的共模阻抗、零共模串擾和零接地通路電感。

然而,理想的共模插入損耗和共模反射,取決於系統的配置。有些系統如帶有插入到盒內之電纜元件的系統,其中的共模反射表現得很像共模抑制,將所有的共模能量保留在封閉的盒子中並遠離電纜。

通常,假設能量耗散又沒有輻射,而且假若共模訊號是有害的,則共模插入損耗是良好的。因此,在大多數通道中,理想的共模損耗對比頻率曲線為高損耗(較大的dB/頻率斜率)和平滑的(線性、無擺動、無共振)。在罕見情況下,傳送共模訊號是重要的,那麼低共模損耗就是好的。

在文獻資料中,許多以前被視為近似理想並按此建模的設計結構,由於資料速率的增加,已經證實為並非理想。不斷增加的文獻知識庫已經針對各種不同的通道特性量化非理想的共模性能指標。例如差模到共模轉換、共模反射、共模阻抗、共模插入損耗、共模對共模串擾和接地通路電感等指標,已被用於分析幾何圖形。線路板幾何形狀,如過孔結構(Via Structures)已被廣泛分析,而且量化其共模影響。

由於電磁干擾(EMI)問題不在訊號完整性的討論範圍內,所以本文並不涉及。

本文使用分析和模擬,研究了取決於共模指標的系統性能。首先,使用發射器、線路板、配對的連接器、另一個線路板以及一個接收器來建立一條通道。該通道是在一系列共模配置,包括在共模阻抗下進行模擬。然後,分析一個具有近乎理想的共模性能的基線通道,並與其他配置進行比較。

然後,改變各個通道的不同部分來檢查可變的性能影響。接著,嚴密檢查發射器共模訊號的影響,因為它可能是主要的共模訊號發生器。當傳輸訊號完全差分後,共模通道的影響可能會很小。共模阻抗對於通道的各個部分是不同的。

另外,也分析模式轉換和共模對共模串擾。使用測試板和連接器分析一些測試案例,這些測試案例代表著不同的連接器配置。在連接器配置上,共模阻抗、模式轉換和共模對共模串擾是主要的差異。

這裡也檢查了通道中潛在的共模問題。通常在一個資料運作速率達到每秒數十億位元(Bit)的系統中,解決問題的方法不只一種。研究設計折衷權衡來改進這些共模問題。

例如,一個系統的位元錯誤率(BER)問題出現在接收器的共模電壓中,可能是由發射器或線路板模式轉換或連接器串擾等引起的。這些問題都可以透過更換發射器、更換線路板設計或更換連接器來解決。

另外,檢查每個解決方案的折衷權衡。詳細研究連接器的折衷權衡,包括差分性能和針對共模性能而進行優化的成本。針對每種改變帶來的系統性能改進,對各種解決方案進行排名。

使用QuickEye進行系統模擬

Ansoft設計人員使用QuickEye進行系統模擬。來自眼圖(Eye Diagram)的指標可用於比較通道配置。使用PRBS11位元模式來說明得出模擬結果,得出眼圖的合理資料,同時保持短的模擬時間。所使用的眼圖指標都是原始資料,直接來自眼圖。

兩個單端發射器設置為訊號源。分別設置幅度、上升和下降時間及斜度來實現差模和共模波形控制。可以設置參數來產生一個純淨的差分訊號,或透過設置不對稱的幅度、上升/下降時間和斜度,可以產生典型的共模波形。如本文先前所示,這些發射器設置相結合,可產生典型的共模電壓訊號。

該發射器模組(TX)設置為3前饋等化器(FFE)分接頭,由元件自動設置來補償通道,使用接收器探頭作為參考。接收器模組(RX)設置為3決策回饋等化器(DFE)分接頭,這也是自動計算的。

通道的中部是連接器元件,在連接器之前和之後是250毫米(mm)的線路板跡線。為產生用於比較的基線資料,某些通道可採用無連接器和一些不同的共模源來進行模擬。給出標稱差分源,可在通道中採用七種模擬方法來產生共模能量。

|

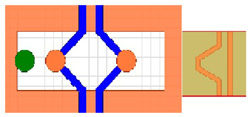

| 圖1 印刷電路板結構:左為嚴重的接地過孔不對稱,右為大的跡線凸出。 |

可以配置通道以實現可選印刷電路板(PCB)特性,它們一般可在通道中找到。雙PCB結構插入到通道中,這是一種層過渡過孔結構,並且是一種偏差補償凸出(Jog-out),如圖1所示。

所用的主要通道變數為延遲偏差(Delay Skew)、上升/下降時間、傳輸線路的共模阻抗和終端。線路板跡線長度保持不變,並且在整個通道中差分終端始終是匹配的。

連接器插入至通道中部的模型中,有四種連接器用於通道模擬。

連接器A是一種表面貼裝的直角連接器,其插配到線路板的邊緣卡(Edgecard)中。連接器B是一種壓接直角連接器,插配到線路板的側邊卡。連接器C則是一種壓接直角連接器插配對,包括插頭和插座。而連接器D是一種表面貼裝夾層連接器插配對,包括插頭和插座。更多連接器細節如表1所示。

模擬結果顯示,通過通道的參考基線是清潔簡單的。無偏差、無連接器,具有純淨的差分訊號和總共500毫米的鬆散耦合差分訊號跡線。差分阻抗(Differential Impedance)為100歐姆而共模阻抗為32歐姆。

如同所有的通道模擬,發送器FFE分接頭設置為3,而接收器DFE分接頭設置為3。圖2為來自參考基線通道的眼圖快照。

|

| 圖2 參考基線通道的眼圖 |

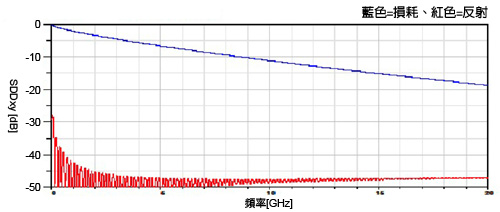

圖3所示為基線通道的頻域匯總,顯示損耗和反射。基線通道僅有一個訊號對,因而無串擾干擾源(Aggressor)。

|

| 圖3 基線通道的損耗和反射 |

在基線通道中,因為訊號是純淨差分,所以完全沒有共模能量。具有10毫微微秒(ps)偏差的通道可當作高共模示例。在接收器端的峰對峰值電壓大概為2×22毫伏特(mV)=44毫伏特,相比大約為2×350毫伏特的峰對峰值差分電壓,其產生大約6%的共模電壓比。但須注意的是,共模訊號的頻率組成與差分訊號相比有一些差異。

在基線通道中可檢測一些都沒有連接器的配置,並可調節發射器變數來建立不同等級的共模能量。此外,可調節帶狀線配置以產生不同程度的共模阻抗,同時保持相同的差分阻抗。這些通道都沒有串擾干擾源。

此外,在帶狀線配置間有一些微小的差異。基線模型具有最大的眼寬和峰對峰值抖動,而非耦合線則具有最大的眼高及最大的抖動(表2)。

下一組模擬繼續採用單一通道,增加共模終端失配或模式轉換。源端保持100歐姆差分、32歐姆共模和100/32差分帶狀線阻抗。在發送器上有10ps延遲偏差,以便注入某些共模能量到通道中。在接收器上,終端為100歐姆差分並且具有一系列共模終端,從1歐姆到75歐姆。

此外,加入線路板特性來建立某些模式轉換,可以加入三種線路板特性。

一種是使用過孔的完全對稱的訊號層過渡,另一種是非對稱訊號層過渡,第三種則是跡線凸出,通常用於偏差補償。

對於兩種PCB模式轉換通道中的每一種,標繪出直通模式轉換SDC21。完全對稱過孔結構具有可以忽略的模式轉換。

但須注意,相比跡線凸出的長度偏差,過孔不對稱要小很多。跡線凸出相當於大約5ps的延遲偏差。

單一通道、共模終端和模式變換配置的結果如表3所示。在發射器上凸出的5ps延遲加上10ps的延遲偏差,顯示的結果與在單一點上的全部15ps延遲相類似。

而且,在路徑上加入一個過孔可使眼圖有所閉合,但嚴重不對稱接地過孔僅比完全對稱的稍微差些。資料顯示,在通道中讓電氣長度匹配較具有對稱接地過孔更為重要。

完成單通道結果的測量後,加入連接器和串擾。對於每個差分對,通道採用單獨的帶狀線線路來設計,因而帶狀線串擾為零。

在模型中,任何引入的串擾都位於連接器和線路板-連接器介面處。這簡化了通道並隔離了連接器的影響。

對於A、B、C和D四種連接器,每一種連接器都可採用最近的串擾干擾源和純淨的差分訊號來模擬通道,然後採用10ps發射器偏差來引入共模能量。

連接器A是表面安裝直角配置,B是壓接直角配置,C則是壓接直角對接連接器,D是表面安裝垂直夾層連接器。為產生代表系統的串擾,所有的干擾源都改變半位週期,將其邊緣大致放置在受干擾眼圖的中部。

此外,所有的干擾源都被設為交替位元模式,因而全部的干擾來源資料模式都將隨機地不同於受干擾的資料模式。

採用零偏差和10ps偏差來運行模擬,是一種捕捉系統性能有沒有共模能量的方法。運行有或沒有干擾源的模擬,顯示了無串擾對比有串擾的系統性能。然而,即使共模能量可以完全耗散,透過差分損耗、差分反射和差分串擾,偏差仍將影響連接器性能。

模擬結果顯示,由於10ps偏差而導致的降級,在眼閉百分比上大約相同。在四種連接器中,每種都具有獨特的共模性能,而在通道性能如何隨共模能量的增加而變化方面,則沒有本質上的不同。差分性能占據主導。

藉著比較無干擾源的0ps偏差配置和多干擾源的0ps偏差配置來分離差分串擾。對於連接器A和B,在20Gbit/s上的差分串擾極小。對於連接器C和D,差分串擾也很小,大約為1毫伏特眼閉。

可透過比較0ps偏差/無干擾源和10ps偏差/無干擾源來檢查直通通路對於偏差的敏感性。

相比0ps偏差無干擾源對比多干擾源的情形,則可透過比較10ps偏差/無干擾源和10ps偏差/多干擾源,以檢測整體串擾和共模能量敏感性。

以系統設計折衷優化眼開程度

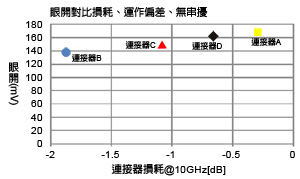

|

| 圖4 連接器損耗對比眼開程度 |

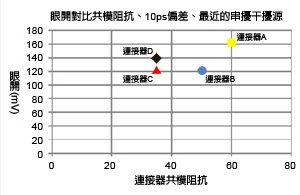

從模擬資料來看,在通道中用於眼開程度(Eye Opening)的主要指標就是插入損耗。將通過通道的基線與有連接器的0ps、無串擾通道做比較,顯示眼開程度與插入損耗密切相關(圖4)。眼圖模擬結果顯示,共模阻抗和眼開程度間無相關性。具有最高共模阻抗的連接器由於損耗最小,所以提供最大的眼開程度(圖5)。

從偏差影響中分離並提取串擾影響,可使用最小眼高比作為比對指標。假如原始眼圖為100毫伏特,而新的眼圖為80毫伏特,那麼指標就等於20%眼閉,所有干擾影響皆可採用此方式。

|

| 圖5 共模阻抗對比眼開程度 |

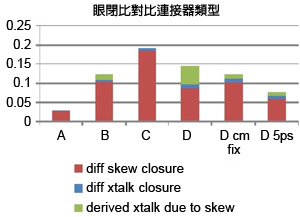

為研究具體的折衷權衡,連接器D適合於極大地減少共模對共模串擾。共模對共模串擾可減少到微不足道的數量,大約為-60dB。這個配置可標記為D cm fix。而且,標準連接器D可採用5ps發射器偏差而不是10ps來分析。這可標記為D 5ps。

由於差分串擾,所有這四種連接器都具有小的眼閉因數。可以理解在一個通道中差分串擾是重要的,因為使用典型的DFE和FFE設置,不能補償這種類型的雜訊。同樣地,圖6顯示了相對的眼閉,而不是絕對的。

|

| 圖6 眼高比 |

例如,連接器C比連接器B具有更大的眼開程度,但在圖6中可以看到連接器C比連接器B對偏差更敏感。這是有道理的,因為連接器C是一個直角連接器,在差分對的每條路徑間有長度偏差,而連接器B是一個直角連接器,在差分對中沒有長度偏差。

在圖6中值得注意的是,差分偏差控制著眼閉比率。在差分對的每邊之間的任何偏差都會直接閉合差分眼。偏差還會加劇差分串擾和共模串擾。差分串擾會隨偏差而增加,因為設計差分訊號的設計旨在抵銷接地返回電流。

有了偏差,這些接地返回電流是不對稱,並會導致差分串擾的增加。共模對共模串擾會受到偏差的影響,而存在更多的共模能量。

由於偏差導致的差分串擾和共模串擾可透過比較D和D cm fix來分離。透過減少共模對共模串擾,使其達到可忽略的數值,從而真正減少由偏差而衍生的串擾。然而,透過減少偏差至5ps,可以看到更為顯著的改進(D vs. D 5ps)。

此外,相比其他的連接器,某些連接器對偏差更為敏感。在此折衷權衡中,系統設計人員必須將減少通道偏差的成本和收益,與減少共模串擾的連接器重新設計的成本和收益進行比較。

連接器A對偏差的敏感性最小,具有非常小的串擾,即使有大的偏差也不例外。

權衡模擬結果

為根據共模指標來研究系統性能,這裡使用發射器、線路板、配對的連接器、另一塊線路板,以及一個接收器來建立一個通道。

此通道是模擬的,將一系列共模阻抗用於通道的每一部分,從無耦合到緊密耦合。眼圖以模擬方式進行檢測,重點是最小的眼高。

對於單一的長跡線通道,無串擾干擾源且無連接器,檢測結果顯示,不對稱接地過孔對眼開程度的影響很小。線路板跡線偏差被證明是至關重要的。檢測也說明了緊耦合線路與非耦合線路間的帶狀線差分跡線配置的影響較小。

模擬資料則表明,連接器和RX、TX共模阻抗對資料眼開程度的影響可以忽略。共模能量源受偏差影響的控制。

在差分對中,發射器或通道偏差提供絕大多數的共模能量與小缺陷。發射器上升/下降時間的失配通常表現為偏差,但處於非常低的程度。發射器的幅度失配必需非常顯著,以便產生明顯的共模能量值。

在採用連接器的通道中,在閉合資料眼方面,插入損耗是主要的因素,偏差也是一個重要因素。串擾只是較小的影響因素,共模阻抗對資料眼開程度的影響可以忽略。

總之,損耗是通道的君王,而偏差則是王后。任何減少損耗和偏差的通道特性將顯著地改良通道的性能。連接器對偏差的敏感性很重要,這是由差分效應控制的。

由共模效應造成的連接器性能降低,對某些連接器而言可被忽略;而連接器共模阻抗對於眼開程度的影響可以忽略。

對於通道來說,引入偏差的線路板特性是至關重要的,而僅僅引入模式轉換的線路板特性則可被忽略。系統設計人員必須仔細權衡來優化性能。

(本文作者Michael Rowlands、Patrick Casher任職於Molex;Pravin Patel為IBM STSM發明大師)