AI模型的參數規模來到百億、千億等級,對資料中心帶來運算壓力。為了高效運用有限資源,資料中心需要盡可能提高資料傳輸速度及記憶體使用效率,而PCIe和CXL身為伺服器元件互連的主要技術,其標準演進受到業界關注。

自從OpenAI在2018年推出參數(Parameter)約達1.1億的大型語言模型(LLM)GPT-1,到GPT-2參數量達到15億,GPT-3更翻了超過百倍來到1,750億。近年來,大型語言模型規模以倍數成長,如今具有數十億、百億參數的大型語言模型比比皆是。除了OpenAI和Google等先行者,也看到Meta、Amazon陸續針對各種應用推出大型語言模型,顯示LLM無論在參數規模還是模型數量皆快速增加。

龐大的參數量將為資料中心帶來運算及儲存挑戰,為了提高運算效率,伺服器內部的周邊元件需要能夠快速傳遞資料,並改善整體記憶體存取效率。為此,PCI Express(PCIe)和Compute Express Link(CXL)互連技術持續以標準換代突破傳輸極限。

資料中心迎接AI挑戰

專攻資料中心的顧問工程公司i3 Solutions Group共同創辦人Ed Ansett在近期文章中表示,由於ChatGPT等大型語言模型多半以Common Crawl作為主要的訓練語料庫,訓練資料並非資料中心面臨壓力的主因,為了提高精確度而增加的參數量才是造成運算需求水漲船高的主要因素之一。

以GPT-3為例,Common Crawl表示,其提供了82%用於訓練GPT-3模型的原始Token,代表大半的訓練資料實際上並未對其他資料中心帶來負擔,GPT-3達到1,750億的參數量才是真正的挑戰所在。隨著Switch Transformer、悟道預訓練模型將資料規模飛越式提升至「兆」級別,AI模型所帶來的資料量和運算需求將是資料中心迫切需要應對的課題。

為了應對上述挑戰,伺服器的GPU、CPU產品不斷推陳出新。不過,處理器的效能提升終究只是滿足運算需求的其中一環,各元件之間還需要能夠有效傳輸資料、高效運用記憶體資源,才能夠真正以最高效率面對AI挑戰。

2025年PCIe 7.0邁入128GTps

PCI-SIG副總裁Richard Solomon(圖1)表示,資料中心、高效能運算(HPC)通常是PCIe新世代標準率先獲得採用的應用場域,為PCIe標準的關鍵市場。面對AI帶來的傳輸需求,Solomon認為,儘管某些應用可能希望獲得更多頻寬,但考量標準制定過程,目前PCIe不容易突破三年換代一次的發展速度;不過,他也提到,若未來相關AI應用誕生,也有機會加速晶片設計流程,加快標準推進速度。

圖1 PCI-SIG副總裁Richard Solomon表示,資料中心、高效能運算(HPC)通常是PCIe新世代標準率先獲得採用的應用場域。

圖1 PCI-SIG副總裁Richard Solomon表示,資料中心、高效能運算(HPC)通常是PCIe新世代標準率先獲得採用的應用場域。

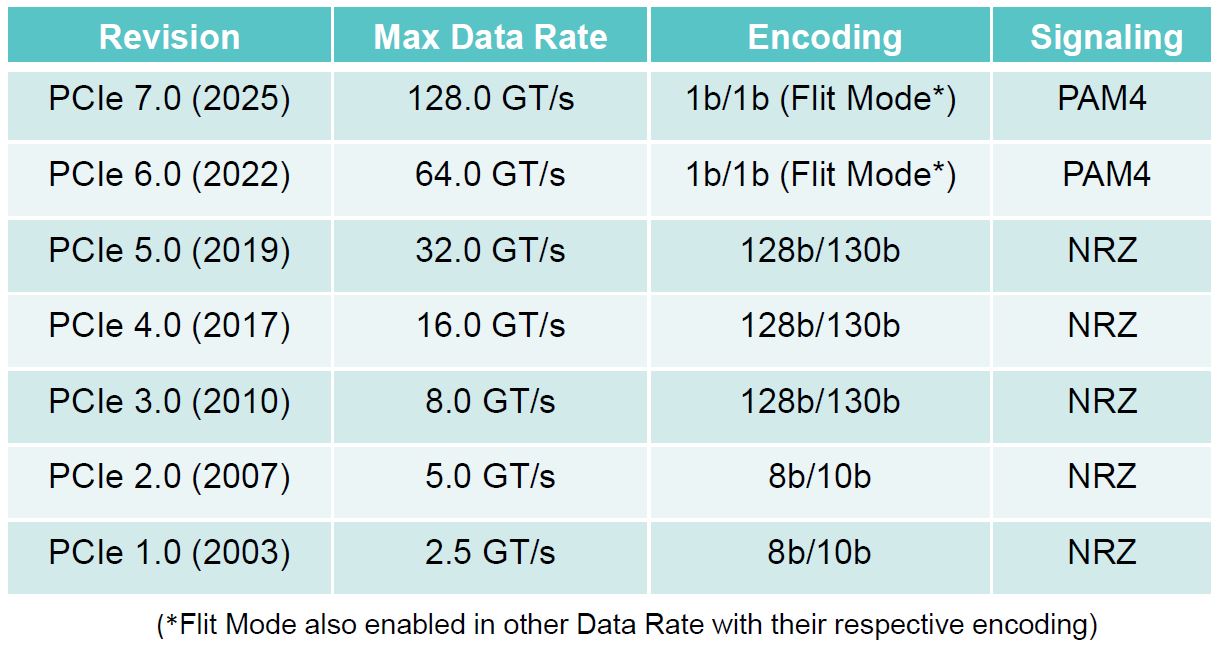

目前,市場上已經可以看到PCIe 5.0產品,而近日於台北舉辦的PCI-SIG開發者大會展出安立知(Anritsu)、Teledyne LeCroy、VIAVI等廠商的PCIe 6.0測試設備,PCI-SIG也規畫於2024年6月進行初步相容性測試(Preliminary FYI Testing),可期待在PCI-SIG正式推出相容性測試流程後,2025年看到更多6.0認證產品進入市場。PCIe 7.0則預計將於2025年發布,由於關鍵技術已於6.0換代時完成,7.0將沿用PAM4調變技術及Flit Mode編碼,主要革新仍為資料速度翻倍,參考過往時程,估計2028年可完成相容性測試流程(表1)。

表1 PCIe歷代標準 (圖片來源:PCI-SIG)

表1 PCIe歷代標準 (圖片來源:PCI-SIG)

6.0/7.0速度翻倍 測試同步演進

為了協助業者取得標準認證,PCI-SIG在2023年10月宣布開放測試服務供應商成為PCIe認證實驗室(Authorized Test Lab),可提供晚一個版本的PCIe認證服務。Granite River Labs(GRL)為首個取得PCIe認證實驗室資格的廠商,目前可提供PCIe 4.0認證服務。

GRL表示,位元錯誤(Bit Error)是PCIe邁入6.0和7.0需要關注的測試重點之一。PCIe 6.0/7.0開始採用PAM4調變,單一訊號能夠承載四種編碼,因此相較於5.0以前的NRZ(Non-return-to-zero)編碼,更容易出現位元錯誤。GRL說明,Gen5基本上可以將位元錯誤率(BER)控制在10E-12以下,而Gen6及往後標準需要以前向糾錯(FEC)技術確保BER在合理範圍內。因此,從Gen6開始,接收端(RX)測試應使用FEC編碼模式(FEC Encoding Pattern)。

儘管目前PCIe 7.0標準尚未制定完成,但測試設備廠和IP業者已經開始提前考慮將資料速度提升至128GTps可能遭遇的挑戰。是德科技技術部門技術專案經理劉宗琪(圖2)表示,是德科技於DesignCon 2024討論PCIe 7.0走到128GTps,進行發射端(TX)測試的示波器頻寬需求。劉宗琪說明,PCIe 6.0會在50GHz TX頻寬採用33GHz頻寬的Bessel Thomson(BT)濾波器,而根據是德科技研究推測,PCIe 7.0的示波器頻寬可能需要提升至70GHz,並採用46.6GHz的BT濾波器。

圖2 是德科技技術部門技術專案經理劉宗琪(右)及是德科技行銷處資深專案經理吳哲樂(左)

圖2 是德科技技術部門技術專案經理劉宗琪(右)及是德科技行銷處資深專案經理吳哲樂(左)

是德科技也於DesignCon展示PCIe 7.0 TX/RX測試解決方案及測試自動化軟體,協助半導體產業加速Gen7產品開發。例如,是德科技M8050A誤碼儀(BERT)便可用以進行PCIe 7.0的RX測試。是德科技行銷處資深專案經理吳哲樂(圖2)表示,通過PCIe認證只是表示產品及格,如果要提升性能水準,需要增加其他測試項目,如抖動(Jitter)干擾測試,而是德科技的測試設備提供高度調整彈性,有助業者進一步針對產品性能進行測試。

AI巨量資料湧進資料中心 PCIe/CXL分進突破傳輸極限(1)

AI巨量資料湧進資料中心 PCIe/CXL分進突破傳輸極限(2)