市場對小型化的追捧,迫使當今手機都採用超緊湊設計,因此要求高度敏感的電子元件不僅尺寸必須非常小,且元件之間的空隙也相當緊密;既不得影響設備工作,也不得破壞鄰近的元件。另一方面,還必須正確無誤地接收基地台發送的微弱訊號。通常,手機的訊號強度可低至-110dBm,這意味著對手機內部元件的工作雜訊要求更嚴苛。

大多數手機都要在基頻和顯示器之間透過16位元微控制器介面、或8位元/16位元RGB介面,以3M~15MHz的速率傳送大量資料。此外,大多數手機現在都配有一個或兩個相機,相機採用8位元RGB介面,在15MHz的介面資料速率下支援互補式金屬氧化物半導體(CMOS)或電荷耦合元件(CCD)影像感測器。通常,這類匯流排介面都可以游走於10公分的軟性電路;基頻部分會多走幾公分,而翻蓋或滑動機制也須再多上幾公分。這個軟性電路必須能承受幾十萬次的彎折,成本要低,並可容許基頻和翻蓋或滑動機制之間的傳輸,從而實現所須連接的許多訊號。這些軟性線纜加在一起的長度較大,加上其阻抗難以控制,會產生嚴重的輻射。

這類輻射是由較高的電壓變化率(dv/dt)和訊號尾端的大電壓幅度引起。訊號邊沿的變化速率越大,電壓幅度越高,輻射強度因而也越大。現有許多模擬工具可估算這類輻射。時脈源的訊號強度往往達到-60dBm以上,遠大於手機接收器內的訊號強度。

諧波導致基地台接收器靈敏度下降

當手機內的訊號強度超過基地台的訊號強度,接收器內較大的內部雜訊就會掩蓋微弱的基地台訊號,導致電話斷線;一旦手機內部的雜訊變大,通常會使手機內的數十個通道受阻,使手機無法使用。為了盡可能減少這種現象,手機設計人員運用了許多技術,包括對線纜內的所有傳輸線進行遮罩,以及對每條資料線進行低通濾波(串聯電阻和並聯電容)。這些措施都會增加成本和尺寸,且會延誤新產品的推出。

基頻到滑蓋機制之間的液晶顯示器(LCD)介面通常可用工作頻率為5MHz的16位元微控制器介面來實現。從電磁輻射的角度看,5MHz的介面將有一些諧波,其分布涵蓋所有奇次諧波。這些諧波隨頻率增加,強度會越來越低;且頻率高過某一臨界值時,其影響就可以被忽略。然而,在CDMA或GSM頻帶內的奇次諧波強度,可能大到足以造成接收器的靈敏度下降,使通道嚴重受阻。

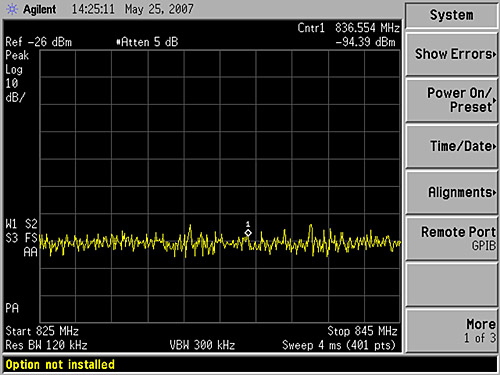

圖1顯示的是CDMA頻帶及未經對外過濾處理的手機所產生的諧波頻譜分析圖。這個特定的手機中已拿掉濾波電路,軟性線纜電路的遮罩也被移除。

|

資料來源:作者整理

圖1 採用平行介面的CDMA頻帶的頻譜 |

可透過設計減少諧波強度

現有一種技術適用於手機設計--高速匯流排序列化,利用此技術可透過速度相對較高的低壓差分介面,在基座和滑蓋或翻蓋機制之間傳送16位元資料和控制訊號。通常,可由19.2MHz的基頻時脈來支援5MHz的CDMA 16位元資料,外加控制介面匯流排。典型的SerDes解決方案包括一個鎖相迴路(PLL),用於加快並行資料傳輸以及把並行資料同步成只需要幾根線就能傳輸高速的串列資料。

線纜數量較少的高速序列介面須穿過印刷電路板(PCB)及軟性線纜電路,因此會有奇次諧波從基本的高速序列介面輻射出來;最初的並行訊號傳輸走線距離(從基頻到串列器及從解串器到顯示器)很短。

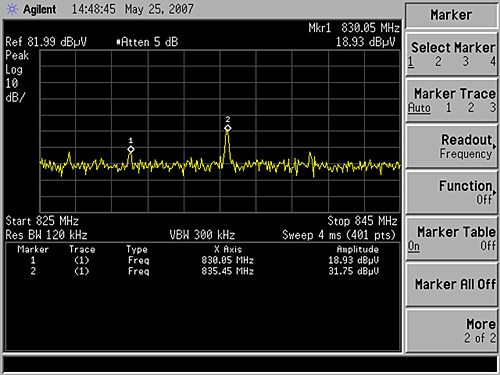

典型的SerDes一般以十三倍倍頻後的19.2MHz CDMA基頻時脈為其參考,如此就可實現頻率為249.6MHz的基本低壓差分序列介面。依照這個常用頻率推算,三次和五次諧波分別為748.8MHz和1,248MHz;這完全在CDMA頻帶之外。此外,這些諧波的強度也較小,因為採用較低的電壓擺幅和能夠抵銷輻射磁場效應的差分訊號技術。圖2為針對CDMA頻帶序列化解決方案的頻譜分析。

|

資料來源:作者整理

圖2 序列化解決方案的諧波內容 |

正確選擇串化器產品是關鍵所在

由於串列資料流程的基本頻率主要由設計人員來選擇,所選擇串化器中的倍頻器最好倍數足夠大,從而使諧波間的頻率間隔增大,同時還不要讓諧波落在應用頻帶的中間。如果設計人員選了一個六倍或七倍的PLL倍頻器,並採用19.2MHz的時脈為參考源,那麼第七次諧波的頻率就會出現在可能引起麻煩的806.4MHz或940.8MHz頻帶的中間。

數位相機介面產生的諧波問題會比LCD的諧波問題更嚴重。大多數微控制器介面都會使用非週期性訊號,比如位址、晶片選擇指令、允許寫操作指令,而相機則有一個週期性的畫素時脈訊號。這種高度週期性的單端LVCMOS電平訊號會發出特徵明顯的訊號,常常會干擾手機的正常接收工作。由於相機畫素時脈很容易達到40MHz,將造成更明顯的干擾。為維持這種較高的畫素時脈速率,邊沿變化速率也必須提高,如此產生的輻射強度甚至會更大。因此,控制好序列化產生的諧波對相機介面尤其受益匪淺。過去,人們一直都把序列化產品的價值歸納於能大幅減少軟性線纜電路中的傳輸線數、減少連接器數目、改善可靠性,以及省去電壓變換器和靜電放電(ESD)元件。直到最近,手機設計人員才發現序列化技術也可改善手機內的電磁相容性(EMC),並省去在PCB上考慮容納濾波電路和遮罩裝置的設計工作,進而設計出尺寸更小的手機,同時加快產品的開發速度。

(本文作者為快捷半導體訊號路徑部資深應用工程經理)