在高速通訊應用中,系統設計人員須要在平衡效能和成本預算間取得最佳化時脈效能。當選擇最佳時脈時,開發人員必須考慮多種影響因素,例如效能、成本、尺寸和輸出邏輯等,其中從事頻域(Frequency Domain)工作的人員更關注相位雜訊;而從事時域(Time Domain)工作的人員則更關注抖動效能。例如在個人電腦(PC)主機板設計中,最佳的時脈訊號通常須要分發到多個邏輯輸入或位置,大量工作被用於最佳化時脈效能。

當判定系統總體效能時,時脈緩衝器將成為等式中的組成部分,同時相位雜訊和抖動的影響因素也將成為等式中的組成部分。工程師為滿足設計規格要求,重要的是透過製造商發布的資料手冊比較和選擇各種時脈特性,進而了解如何測量時脈緩衝器的相位雜訊,以及影響時脈緩衝器效能的因素,並知道應特別注意哪些細節。

相位雜訊測量

時脈分發積體電路(IC)不直接生成時脈訊號,而是再生並提供多個時脈拷貝。因此,時脈分發IC的相位雜訊只能在有輸入訊號時進行測量。衡量時脈分發IC品質最常用的方式是「附加相位雜訊」,而經常不被提及的是附加相位抖動的標準測量方法。在此,本文將採用芯科實驗室(Silicon Laboratories)的Si53311時脈緩衝器,呈現附加相位抖動的一種推薦方法,以及影響緩衝器效能的各種因素。相同的原則和測試方法能夠用於分析大多數緩衝器、分頻器和其他分發IC的效能。重要的是了解附加抖動效能與下列可變因素的相關性,包括在給定幅度下的輸入訊號上升和下降時間或轉換速率、輸出格式、輸出頻率、電源電壓。

事實上,輸入訊號上升和下降時間顯著影響附加相位抖動。雖然乍看之下是真的,但是使等式更完整是考慮輸入訊號上升和下降時間以及幅度,或是幅度與上升下降時間的比率,可表示為V/ns或轉換速率。大多數工程師僅將轉換速率與類比元件產生連結,例如運算放大器,其在數位元件資料手冊中轉換速率並不常見。即便轉換速率並不常見,但它是描述附加相位雜訊改善或衰減更準確的方式,如果轉換速率值沒有提出,那麼可根據資料手冊中的技術參數計算出來。舉例來說,假設有一個低電壓差動訊號(LVDS),其具有350毫伏特(mV)的單邊振幅和400微微秒(ps)的上升和下降時間。測量點在20%、80%時,差動轉換速率將是(2×350毫伏特×0.6)/(400微微秒)或1.05V/ns。(出於本文論述目的,以下使用差動轉換速率)。

同樣,相位雜訊只能在有輸入訊號的情況下進行測量,而且應該測量總體抖動。時脈緩衝器的影響被稱為「附加相位抖動」,表1顯示一個附加相位抖動規格範例,須要注意的是測試條件包括轉換速率、輸出頻率、邏輯位準格式和工作電壓,這些條件都會影響附加抖動。當進行附加抖動效能比較時,為使對比有意義,必須使用相同的測量條件;如果沒有使用相同的測量條件,那麼可能得到不正確的結果,在最壞的情況下,如果系統設計者期望滿足一個規格,但時脈緩衝器的工作條件不佳,將不能達到要求。

|

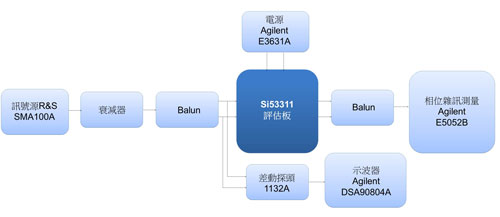

| 圖1 附加抖動的測試元件 |

圖1顯示一種用於表示附加相位雜訊並生成後續圖表的測試設置。訊號源雜訊必須低於被測試設備(DUT),理想情況是低3-10dB相位雜訊。測試使用一台低雜訊、正弦波輸出的羅德史瓦茲(R&S)SMA100A,其具有較寬的輸出頻率範圍。然而,出於資料收集的目的,將調整轉換速率並採集相位雜訊資料,雖然轉換速率可輕易透過SMA100A輸出幅度進行調整,但缺點是相位雜訊會在不同輸出位準下改變。

為此,替代方法是SMA100A輸出保持在一個恆定位準,搭配使用的衰減器,用於調節轉換速率。轉換速率可使用一個高阻抗差動探頭在20%、80%位準時進行測量。安捷倫(Agilent)E5052B則用來測量相位雜訊,在12kHz~20MHz、1.875MHz~20MHz和10kHz~1MHz頻段分別進行資料擷取,以便進行比較。

時脈效能分析參數

在分析任何時序元件的效能時,相位雜訊是一個關鍵參數,其為抖動的頻域測量值,也可依據此值計算其等效的時域值或相位抖動(如果給定偏移頻寬)。使用這種方法出於許多原因,首先它是快速且可重複的,僅需很少的設備進行最佳化調整,因此允許工程師去分析感興趣的特定頻寬,以識別和減少雜散訊號。其次,大多數時域測量不能提供足夠的解析度、不能進行目前高效能時序元件所提供的精準毫微微秒(Femtosecond)等級測量。

時脈緩衝器的相位雜訊只能在有輸入訊號的情況下進行測量,而且須要測量總體抖動。時脈緩衝器的影響被稱為附加相位抖動,為表示因緩衝器引起的相位抖動影響,首先要進行訊號源測量,接著進行訊號源加DUT的測量,最後透過使用等式3計算出相位抖動,通常設計者進行的合理假設是訊號源和緩衝器雜訊是不相關的,而且完全是隨機抖動組成的。不過,當給定時脈緩衝器的附加抖動值和訊號源抖動值時(它們通常以均方根值的形式提供),須用和的平方根(如等式1)計算總體抖動。

等式1:J2Total=J2Source+J2

buffer

等式2:J2buffer=J2Total–J2Source

等式3:Jbuffer=√(J2Total–J2Source)

另一方面,為精準呈現緩衝器,參考時脈的相位雜訊必須比DUT低3~10dB。直覺上來說,當測量更低相位雜訊元件時,裕量要求更低。通常用恆溫晶體振盪器(OCXO)做為訊號源,但這會帶來不確定性,或者至少帶來高成本(在較高頻率下),並在近端仍然受到限制,例如在10Hz、100Hz時,許多有單端輸出的低相位雜訊號源可能須要轉換成差動訊號。在這些情況下,平衡-不平衡轉換器(Balun)能夠提供一個很好的低成本解決方案,而且不須要太關心它的雜訊影響。

相位雜訊效能比較

表2比較相同緩衝器在三種不同訊號源相位雜訊等級條件下的附加相位雜訊效能。在第一個例子中,訊號源相位雜訊比DUT好3?10dB,使用等式3獲得97fs的緩衝器附加相位雜訊,這是一個精準的結果。然而,當訊號源具有與DUT類似的相位雜訊時,則得到一個非常好的附加相位抖動數值。在第二個例子中,相同緩衝器的相位雜訊效能在具有相似相位雜訊效能的訊號源驅動時得到34fs的附加抖動,這是一個很好的結果。

展現附加抖動如何依賴測試設備的極端範例顯示在最後的例子中,這裡訊號源有334fs的相位雜訊,訊號源加緩衝器顯示出改善的284fs相位抖動。顯然,這不是一個有效的呈現附加抖動的方法,當透過使用附加抖動比較元件時必須要注意這一點,另外一種可選方法是檢查緩衝器規定的相位雜訊效能。

影響抖動效能因素

增加緩衝器到時脈樹時,重要的是要知道哪些因素會影響抖動效能,因此當查看資料手冊時,這也是非常重要的注意事項。資料手冊中供應商如何說明緩衝器的抖動效能會極大影響該參數,例如,如果一個供應商使用比另一個更快的轉換速率,那麼兩個具有相似效能的緩衝器可能展現出差異很大的附加抖動效能。

|

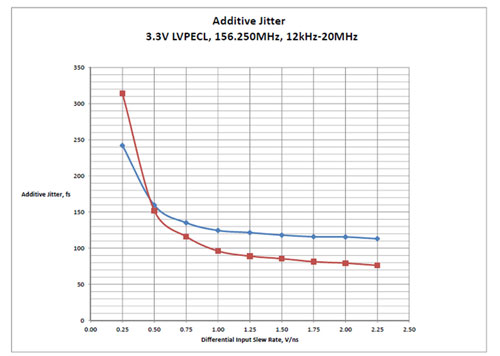

| 圖2 兩個不同緩衝器產品的附加抖動與轉換速率的對比圖 |

圖2顯示兩個不同的時脈緩衝器的附加相位抖動與輸入轉換速率的對比,其也強調在比較附加相位抖動時採用相同轉換速率的重要性,並且應用中也要使用相同的值。在兩個案例中,附加抖動會隨著轉換速率變化而減小或增加。值得注意的是,以正方形接點折線顯示的結果可能被做為較低附加相位抖動的解決方案,然而實際上它是更敏感的,在較低的轉換速率下會快速衰減,例如低頻率正弦波或互補式金屬氧化物半導體(CMOS)時脈。以下就影響附加相位抖動的因素分別做論述,包括積分頻寬、輸出頻率、邏輯種類、電源電壓等。

| ‧ |

|

| 用於抖動計算的積分頻寬對測量抖動效能也有非常大的影響,使用何種積分頻寬取決於應用。如果有疑問,在進行對比時確保使用相同的頻寬,而在數位通訊中最常用的頻寬是12kHz?20MHz,但對於大多數濾波器來說,使用更窄的頻寬將會獲得更低和更好的抖動值。 |

|

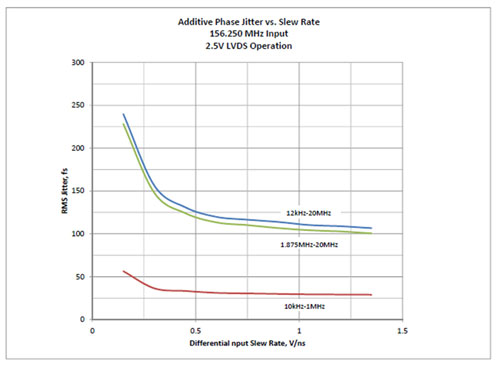

| 圖3 附加相位抖動與轉換斜率的對比圖 |

圖3顯示圖1中元件的測試結果,其使用156.250MHz輸入頻率,以及三個積分頻寬,包括12kHz~20MHz、1.875MHz~20MHz和10kHz~1MHz。圖中顯示最佳結果出現在0.6V/ns或更快轉換速率時,說明給定的附加抖動值會隨頻寬改變的程度。

| ‧ |

|

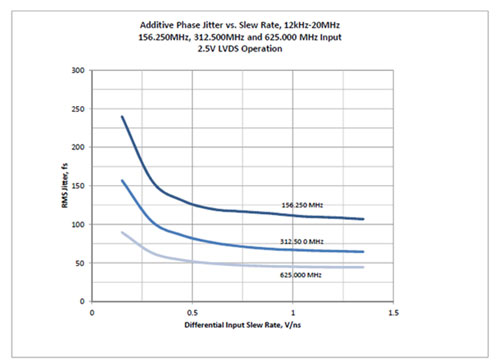

| 輸出頻率也對附加抖動有顯著的影響,更高頻率通常得到更好的附加抖動效能。如果使用者知道將使用何種頻率,那麼將有助於查看資料手冊中接近其感興趣的頻率資料。圖4顯示在三個不同輸出頻率下,相同時脈緩衝器的附加相位抖動,附加抖動在更高輸出頻率下通常更低,相差20log(f1/f2)或6dB(兩倍頻率)。當積分的相位雜訊功率是常量時,相位抖動就會更低,這是因為它是由積分相位雜訊的1/f倍得到的。此外,使用資料手冊規格比較元件效能時,也要關注輸出頻率。 |

| ‧ |

|

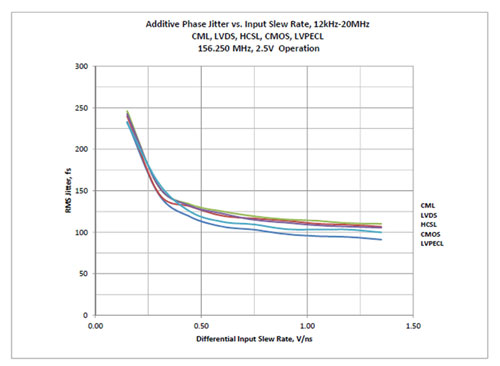

| 輸出邏輯格式也能影響附加相位抖動效能。芯科實驗室的Si533xx系列產品是通用緩衝器,可使用接腳設定輸出邏輯格式,包括LVDS、LVPECL、HCSL、CML和CMOS。圖5顯示各種輸出邏輯種類的附加相位雜訊,和相位雜訊對轉換速率的敏感度。這些結果證明,須要針對應用中使用的輸出邏輯和資料手冊中列出的條件進行對比檢查,而LVPECL對於需要最低附加相位雜訊效能的應用來說是最好的選擇。由於這些潛在的差異,因此最好針對使用的輸出邏輯格式檢查附加抖動相位雜訊。 |

| ‧ |

|

| 工作電壓也能影響附加抖動效能,這是一個重要的考慮因素,因為許多時脈緩衝器可以工作在1.8伏特、2.5伏特和3.3伏特。本文中,緩衝器產品間效能差異很小,然而對於其他緩衝器產品,附件抖動效能可能不同;不過對於系統設計和緩衝器選擇來說這是一個重要的考慮因素,最好是能夠聯繫緩衝器產品製造商,或如果有設備和時間,直接去呈現它們的效能。 |

|

| 圖4 附加抖動與輸出頻率的對比圖 |

|

| 圖5 附加抖動與輸出邏輯的對比圖 |

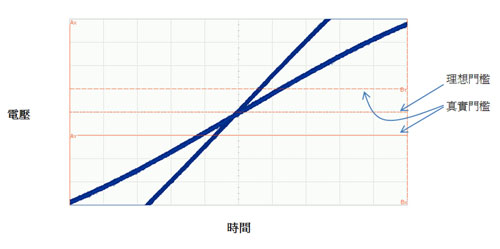

從圖2到圖5顯示如何透過增加輸入訊號的轉換速率來最佳化相位雜訊效能。時脈緩衝器的輸入是根據電壓切換的,理想情況下電壓是不變的。實際上,它會有一個狹窄的變化視窗,因此門檻變化會引起邊緣時序改變,導致抖動變差。更快的輸入轉換斜率會使處於變動視窗中的時間更少,因而可以將對系統的影響降到最小。圖6顯示一個誇大的轉換電壓視窗,其中有兩次轉換速率變化,更快的邊緣在定義的視窗上占用更少的時間,效能更好。

|

| 圖6 轉換門檻中轉換速率變動範例 |

評估時脈分發IC效能

時脈緩衝器的附加相位雜訊與轉換速率能夠透過邏輯種類、輸入轉換率、輸出頻率和電源電壓進行呈現。這種方法說明設計人員有效評估系統的總體抖動預算需求,簡化元件的選擇,提高對工作條件相關性的意識。雖然相對於輸入轉換速率變化來說,時脈緩衝器對其它因素的變化不太敏感,但是在轉換速率大於0.6V/ns時取得最佳結果,對於大多數差動時脈源來說,這不是一個嚴格的要求。例如,一個差動LVDS訊號,在20%和80%的振幅時具有至少250毫伏特的單邊幅度和最大400微微秒的上升和下降時間,那麼差動轉換率將是(2×250毫伏特×0.6)/(400微微秒)或者0.75V/ns。

為大幅提高時脈緩衝器的附加相位雜訊效能,應使用最佳的轉換速率(0.6V/ns或更高的輸入訊號轉換速率),但透過使用高成本和高功耗的超快邏輯不會帶來顯著改善。而大多數差動時脈(甚至是低輸出頻率)有足夠的轉換速率。

另一方面,低頻正弦波或者CMOS時脈有轉換速率限制,如果邊緣不陡峭將導致總體相位雜訊變差,否則設計人員得花不必要的時間去追蹤可疑的電源雜訊、布局布線問題和其他可能的原因。若要取得最大的輸入訊號轉換速率,最好盡可能將時脈緩衝器放置靠近輸入訊號源,使用差動輸入有效的加倍轉換速率,並具備共模雜訊抑制、保持全位準輸入擺幅(除非超過最大位準,否則不要衰減輸入)、最佳化阻抗匹配(因為反射也會使輸入訊號轉換速率變差)等好處。當設計分發緩衝器進入時脈樹時,花費時間最佳化輸入訊號轉換速率是非常值得的。

最後,當根據資料手冊規範評估時脈分發IC效能,以及當在電路中增加緩衝器時,因為輸入訊號轉換速率、輸出頻率、輸出邏輯、積分頻寬、電源電壓和測試方法的不同會導致大幅的效能差異,因此設計人員必須高度重視這些影響因素。

(本文作者任職於芯科實驗室)