本文將討論如何透過嵌入在現場可編程閘陣列(FPGA)中的光纖介面技術,來克服銅線互聯相關的傳輸距離、功率消耗、埠密度、成本及複雜的電路板等難題。晶片至晶片、晶片至模組、機架至機架,以及系統至系統介面等各種傳輸距離資料速率已經超過10Gbit/s,設計人員利用這種技術能夠克服這些難題,與傳統的獨立電光技術相比,具有很大的優勢。

面對當今的高頻寬、低延時裝置,以及智慧型手機、平板裝置、高畫質電視(HDTV)和三維(3D)電視等相關應用,電腦和網路系統供應商致力於實現不會顯著增加網路或網際網路資料流程壅塞和延時的系統。輸入/輸出(I/O)資料速率和密度之所以不斷提高,是因為伺服器、區域網路(LAN)路由器和交換器、儲存區域網路(SAN)交換器和磁碟陣列(RAID)、廣域網路(WAN)光交換器,以及傳送系統的廣泛應用。例如,PCI Express(PCIe)介面每個通路的資料速率從Gen 1.0的2.5Gbit/s增加到當前Gen 3.0的8.0Gbit/s,之後的Gen 4.0則將增加到16Gbit/s。圖1顯示網際網路和網際網路通訊協定(IP)資料流程的需求發展趨勢。

|

資料來源:Cisco VNI(2010)

圖1 2009~2014年網際網路頻寬和IP資料流程發展趨勢 |

FPGA在當今的網路、電腦、資料中心和通訊輔助系統中扮演重要角色。Altera的FPGA光纖介面在FPGA封裝中整合最新的FPGA,以及最先進的雷射和光探測器,進而克服銅線互聯的限制。光纖FPGA介面在傳輸距離、功率消耗、成本、密度和外形封裝等方面有很大的優勢,遠遠超過傳統的電訊號和互聯,以及獨立電光訊號和互聯。

銅線互聯受限頻率耗損

在實現新系統時,與前幾代系統相比,網路和資料中心工作人員希望能夠避免功率消耗和成本代價。其需求是應逐步減小每一代系統與pJ/bit指標相關的功率消耗和資料傳送參數。圖2顯示每個通路資料速率的發展趨勢,資料來自國際半導體技術藍圖(ITRS)2009版。

|

| 圖2 ITRS預測的高速I/O資料率發展趨勢 |

設計人員在印刷電路板(PCB)上,對晶片至晶片、晶片至模組介面廣泛使用銅線互聯進行走線,以及在背板晶片至晶片和晶片至晶片介面上採用銅線組件。在10Gbit/s時,晶片至晶片以及晶片至模組介面的傳輸距離大約是0.3米(m),背板晶片至晶片傳輸距離是1米,銅線組件的晶片至晶片傳輸距離是7米。

銅線互聯遇到的難題是,由於頻率相關損耗問題,使其無法適應資料速率的變化。例如,應用最廣泛的FR-4銅走線材料在5GHz時的損耗是0.5~1.5dB/in(10Gbit/s速率奈奎斯特定律),而在12.5GHz時損耗增加到2.0~3.0dB/in(25Gbit/s速率奈奎斯特定律)。反射損失和串擾也隨著頻率的變大而增加。

|

| 圖3 PCI Express伺服器通道的介入損失、反射損失和串擾 |

圖3顯示PCI Express伺服器通道的介入損失、反射損失及串擾。這個實例表明介入損失和反射損失也會隨著資料速率的增大而增加。在8GHz(16Gbit/s)時,介入損失大約是-60dB,遠遠超出非歸零(NRZ)訊號的等化動態範圍(~40dB)。此實例說明,目前的技術除非縮短通道長度,否則不能適應16Gbit/s速率,這將限制實際應用,不具有靈活性。而且,這種方法需要其他零組件如中繼器等,將會增大功率消耗、成本和複雜度。

在這些採用銅線的系統中,設計人員一般必須補償訊號介入損失,例如符際干擾(ISI),或資料相關抖動(DDJ)、反射損失和串擾等。設計人員透過使用各種等化器來處理這些訊號損失,例如前饋等化器(FFE)、連續時間線性等化器(CTLE)或決策回饋等化器(DFE)等,在銅材料構成的通道上實現這些發射器或接收器,以保證能夠滿足鏈路性能,即誤碼率(BER)<10-12。

但是,等化器增大功率消耗,須要付出代價,特別是DFE。隨著資料速率的提高,介入損失、反射損失和串擾也隨之增大,需要更強的等化器,亦即更多的抽頭或更大的直流電(DC)/交流電(AC)增益,來補償最終的訊號損失,以保證性能不變,這種方法同樣增加功率消耗。

在目前的互聯輔助系統內,設計人員在10米以內主要使用銅材料傳輸電訊號,在10米以上使用光纖傳輸光訊號,這是由銅材料電子零組件及光纖零組件的特性和成本結構所決定。設計人員希望在10米以內也採用光纖來傳輸訊號,進而克服銅材料電訊號的損耗、訊號完整性及功率消耗等難題。隨著資料速率的提高,獨立的電子零組件和光學零組件,以及相關的成本和功率消耗,導致很難實現這個願望。

光纖介面幾無耗損問題

與銅介面相比,光纖幾乎沒有損耗。多模光纖(MMF)在850奈米(nm)和1,300奈米波長的損耗大約分別為3dB/km和1dB/km。單模光纖(SMF)在1,300奈米和1,550奈米波長的損耗大約分別為0.4dB/km及0.25dB/km。MFF的芯徑較大,約50微米(μm),頻寬大約為2GHz/公里(km),因此成本較低;而SMF芯徑較小,約9微米,實際頻寬達到100THz,成本相對要高一些。

透過MMF驅動光訊號的雷射元件一般是發光二極體(LED)或垂直共振腔表面放射雷射(VCSEL)。MMF通常用在1公里以內,而SMF的傳輸距離在1公里至幾千公里。10Gbit/s時,MMF的傳輸距離大約是300米。與銅材料的電路鏈結不同,光鏈路的功率消耗和代價幾乎與傳輸距離無關。而且,光訊號與電訊號不同,它不受電磁干擾(EMI)的影響,沒有振幅串擾,具有更好的訊號完整性。透過分波多工(WDM)技術,同一根光纖能夠支援多個通道,進而節省通道材料。

FPGA在當今的網路、電腦、資料中心和通訊輔助系統中扮演重要角色。FPGA提供關鍵重新配置和系統單晶片(SoC)功能,以支援資料處理和傳送,實現運算、數位訊號處理(DSP)、資料封包處理、圖幀處理、路由、交換及橋接媒體存取控制(MAC)/前向錯誤校正(FEC)等功能。圖4顯示Altera FPGA和高階收發器電路提供的晶片至晶片、晶片至模組以及系統至系統的網路輔助系統I/O鏈路和資料處理功能。

|

| 圖4 Altera FPGA應用於網際網路/網路輔助系統 |

高階收發器整合多種元件

|

| 圖5 Altera FPGA收發器技術發展路徑 |

10餘年來,Altera的收發器技術發展非常迅速,提供電訊號傳輸和接收功能,目前28奈米製程節點的資料速率高達28Gbit/s。這些收發器還支援高階時脈產生、時脈恢復及等化功能(即FFE、CTLE和DFE)。圖5顯示FPGA收發器、資料速率和製程節點的發展。高階收發器技術無縫整合FPGA以及光學雷射和接收器。

圖6顯示Altera高階收發器特性和性能。在發射(TX)端,由於使用高階LC振盪器,因此28Gbit/s時的抖動產生非常低,低於300fs。TX FFE等化器能夠提供四個可編程抽頭。在接收(RX)側,有多級CTLE,提供12dB DC增益和20dB AC增益,可調峰值頻率,及可選自動等化係數發現等功能。

|

| 圖6 Altera高階FPGA收發器特性和性能 |

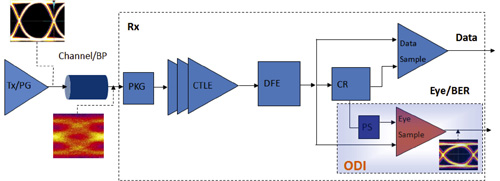

RX DFE提供五個抽頭,能夠補償大部分不相關抖動和雜訊。在可以鎖定至資料或參考時脈之混合架構的基礎上,每一個抽頭權重針對時脈恢復(CR)進行功率消耗最佳化。這些條件產生很好的到達資料鎖定時間/範圍,支援較大的抖動容忍度。收發器具有較好的運行長度處理(約幾百UI)、頻寬(約幾百MHz)及抖動餘域斜率(優於-40dB/十倍頻程)。收發器具有內置晶片內儀器(ODI)功能,可測量BER曲線和眼框圖。

高階ODI支援TX自適應等化、RX最佳取樣點發現等功能,降低相關的BER。而且,收發器支援電路板和系統快速開發、除錯、非置入式鏈路特性及資料流程性能監控等,這些功能都能以低成本高功效的方式實現。如圖6所示,RX CTLE或DFE很容易打開已經閉合的訊號完整性眼框圖,然後由ODI進行驗證。在28奈米時,此收發器可實現個位數約8pJ/bit的功效。

光纖結合FPGA 效果加乘

|

| 圖7 具有光纖介面的FPGA |

採用高階收發器技術,將可容易地整合Altera FPGA和光纖元件。圖7所示的例子是一顆具有光纖介面的FPGA,此FPGA整合光纖介面,如發射器光學次組裝模組(TOSA)和接收器光學次組裝模組(ROSA)等,無需獨立的光模組,便能夠支援光訊號傳輸和接收。

設計人員可採用光纖介面FPGA來替代晶片至模組鏈路系統,大幅度降低功率消耗和成本,減少對資源的占用,同時提高埠密度(圖8)。之所以能夠實現這些功能,是因為此高功效收發器具有同類最好的時脈產生和時脈恢復、訊號調理和等化等功能,並且透過ODI內置測試和測量功能。

|

| 圖8 一顆具有光纖介面的FPGA替代了晶片至模組鏈路。 |

在圖9所示的一般應用中含有FPGA光纖介面。設計人員可以在光纖背板、電路板至電路板、機架至機架,以及系統至系統互聯上使用具有光纖介面的FPGA,10Gbit/s線路速率時傳輸距離達到100米。通道最大資料速率取決於FPGA收發器資料速率,目前28奈米製程節點達到28Gbit/s。

|

| 圖9 光纖FPGA應用 |

資料中心(DC)使用具有光纖介面FPGA的一個具體實例顯示在圖10中。圖中畫出內部聯網電路板背板線路卡、電路板至電路板、機架至機架以及系統至系統互聯,LAN交換器、路由器、SAN交換器和磁碟陣列,以及伺服器陣列使用這種新FPGA。

|

| 圖10 資料中心具有光纖介面的FPGA |

具有光纖介面的FPGA支援0.3~100米的訊號處理和光纖互聯,非常適合應用於所有DC互聯。與傳統技術相比,這具有明顯的功率消耗、密度和成本優勢。在採用該技術前,這些功能無法實現,特別是傳輸距離在10米以上的情況。

光纖介面FPGA前景看好

銅材料晶片至晶片介面面臨的主要難題包括傳輸距離、功率消耗、成本、電路板材料及複雜的電路板等。同樣地,成本、埠密度、功率消耗、外形封裝和電路板材料,也是目前所使用主控晶片和獨立光模組解決方案遇到的主要挑戰。資料速率達到10Gbit/s以上時,Altera的光纖介面技術整合最新的FPGA,以及最先進的雷射光源和光探測器,克服各種情況所遇到的難題。

與傳統的電訊號和互聯,以及電光訊號和互聯技術相比,具有光纖介面的FPGA在傳輸距離、功率消耗、成本、密度、外形封裝和重量等方面有很大的優勢。設計人員可以在背板短距離晶片至晶片(或者大於1米)、電路板至電路板,以及傳輸距離在100米的機架至機架、系統至系統互聯上使用FPGA光纖介面。

不難想像,採用光纖介面技術的FPGA具有傳輸距離、功率消耗、成本、密度、外形封裝、重量、EMI及能夠克服串擾等優勢,將廣泛應用於未來的資料通訊和電信系統、資料中心、資料傳送和軍事網路系統內,還可以用在測試測量、醫療和廣播等系統內。這種技術將永久性地改變未來網際網路、網路、資料中心、測試測量、醫療和廣播輔助系統的設計和開發。

(本文作者為Altera首席設計師)