本文將討論各種設計10Gbit/s高速串列差動式電氣通道訊號的方法,電氣介面應用使用HSpice軟體進行模擬,展示了訊號品質如何受到使用微帶線(Microstripe)或帶狀線(Stripline)走線的影響以及討論各自的優缺點,此外並使用模擬結果進行範例XFI通道的組裝來展現應用的可行性。

之所以要詳盡討論10Gbit/s串列資料傳輸應用在印刷電路板(PCB)設計的主要考量,是協助PCB設計工程師發展出搭配適合的差動式串列收發器,以及連接到串列解串列晶片(SerDes)的電氣通道(XFI通道)主控電路板的布局設計,主要焦點放在電氣通道中各種零組件的頻率相關特性,此外也探討了可插式連接器的參數問題。

高速連接訊號追求完整性 影響因素所在多有

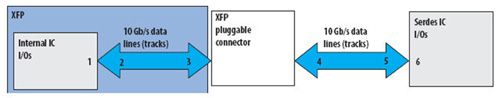

圖1為典型電氣通道的功能方塊圖,這是光學收發器XFP應用中的簡化電氣通道,細節如表1。在此先假設資料的電氣特性符合XFI標準,而關於XFI介面的進一步詳細資料,請參考XFP MSA(www.xfpmsa.org)網站。

|

| 圖1 XFI電器通道功能方塊圖 |

| 表1 XFP資料通道細節 |

| 數字 |

位置 |

| 1-2 |

由晶片底座到晶片輸出入接腳的通道 |

| 2-3 |

包含貫孔的10Gbit/s資料通道 |

| 3-4 |

通過可插式連接器的資料通道 |

| 4-5 |

包含貫孔的10Gbit/s資料通道 |

| 5-6 |

由晶片輸出入接腳到晶片底座的通道 |

在XFP MSA標準中,其中一個選擇是使用開眼晶片(Eye Opener IC),這可以降低XFI通道雙向訊號的抖動量(Jitter),不過在此的重點是探討因通道所造成的訊號品質劣化,因此必須進行實際的測試才能取得通道的實際驗證。在尚未取得測量資料前,先對XFI通道內元素的參數值以及寄生效應進行估計。

影響高速資料連接的訊號完整性有許多原因,分別包括走線的尺寸大小、PCB介電物質的特性、可插式連接器的實體設計與實施效應、走線與零組件接點間的不連續性(反射)、使用的走線形式與長度,微帶線或帶狀線、貫孔的實際製作組態、訊號品質的資料樣式相關性--抖動與溫度相關性等。

以下將依序討論上述因素,並分析其對數位資料串流訊號傳輸的影響。

走線尺寸/PCB材料影響耗損

走線的尺寸大小以及PCB材料特性隨著頻率的增加而有更多的限制,例如,PCB材料的介電常數(Dielectric Constant)控制了圍繞傳輸線的有效電容量,並與頻率相關,而流經介電質的電磁波速度則會隨著介電常數Er的開根號值比例下降。

例如對於固定的電磁波,如果介電常數提高,那麼速度就會下降;另一方面,隨著電磁波頻率的上升,許多用來製作PCB的介電材料有效介電常數將會下滑。因此,電氣訊號的群體速度會受到頻率的影響,稱為分散效應(Dispersion),不過這個效應通常相當小,可以忽略。

PCB的介電材料通常由玻璃纖維以及樹脂組成,介電常數會受到用來製作層壓板的玻璃纖維相對樹脂比率的影響,高速資料傳輸應用中最常使用的介電材料為FR4。這個材料擁有低介電常數,標準的樹脂相對玻璃纖維比率大約55%左右,在5GHz的速度下,介電常數約為4.2。

傳輸線的耗損由導體的表面效應(Skin Effect)以及介電質對電氣能量的吸收能力決定,表面效應限制電流流經傳導材料,通常是銅的表面,加大表面積,例如增加傳輸線的寬度就可以減輕表面效應。電氣能量在介電質內的耗損由介電質耗損因數(d)代表,由於表面效應,在大部分速度達1GHz的數位式應用中介電質耗損只占整體耗損的小部分,不過比起表面效應耗損,由於介電質耗損會隨著頻率上升增加得更快,因此在超高資料率的系統上就可能成為主要的耗損來源。

當以大約5GHz或更高的頻率傳輸資料時,走線尺寸大小與PCB材料的組合進而尋求低通道耗損,例如低衰減以維持訊號位準高於決定數位數值的臨界值,以及透過對不必要反射的適當衰減,以便將抖動或停駐波效應降到最低的權衡選擇上非常重要。對於5GHz下較短的走線長度,使用寬鬆的組合來加入少數量的額外衰減可能可以真正改善整體XFI通道的回返耗損。

可插式連接器限制資料通道使用

在使用可插式連接器時,必須注意連接器的實體特性不會限制它在目標資料通道的使用。連接器的電氣寄生如電感,必須在評估時加以考慮。寄生值的大小通常可以由連接器的製造商取得,並應用到資料通道訊號完整性評估的電氣模擬上。

評估PCB布局/走線方式

在評估資料走線的不連續性時,可以使用時間領域的反射計(Time Domain Reflectometry, TDR)。當傳輸資料時,必須避免反射以確保只接受具備良好定義邊緣與電壓位準的乾淨訊號,以大約5GHz速度傳輸XFI通道的短走線長度為例,可以使用具備較高耗損因數的PCB材料來協助吸收反射,改善訊號的品質,另一方面,對於高速資料傳輸應用,使用微帶線或帶狀線等不同走線形式則各有優缺點(表2)。

| 表2 帶狀線與微帶線的優缺點比較 |

| |

優點 |

缺點 |

| 帶狀線 |

埋入式走線可以避免表面EMI發射並改善EMI抵抗能力 |

必須使用貫孔﹔

(1)可能因造成反射而影響訊號的品質

(2)音較窄走線寬度以及較大介電質耗損而限制走線長度 |

| 微帶線 |

可以使用較長的走線長度,不需貫孔,因此影響訊號完整性的阻抗不連續性較少,可預測性較高 |

會造成訊號傳輸元件以及周邊零組件的EMI發射與抵抗EMI能力降低、開放空間發射 |

使用貫孔造成多重電氣反射

在高速電氣設計中加入貫孔會帶來因資料線路阻抗不連續所造成的多重電氣反射,此外,要在高於1GHz的頻率下達到所需的訊號品質,製造程序較為麻煩,其他的考量還包括簡化電氣設計以及訊號完整性的最佳化。

訊號樣式左右訊號品質

測試訊號樣式(Test Pattern)的頻率內容以及典型使用情況下的流量將決定訊號如何受到資料格式的影響,同步光纖網路(Synchronous Optical Network, SONET)的資料格式通常在較低頻率時擁有比乙太網路(Ethernet)訊號更多的內容,並經過正規化來移除位元率的差異,主要原因來自於SONET格式中允許冗長序列的0或1訊號,因此對於不同的網路通訊協定,PCB必須處理的頻率範圍有相當大的不同,可能會因諧振效應以及資料通道的整體頻率相關性而大幅影響通道訊號的品質。因此相當重要的是,除了檢查資料通道是否能夠在最高頻率運作外,也必須注意不能濾除可能出現在SONET通訊協定中的低頻內容。

可能具備更低頻率內容的測試樣式,例如223-1 PRBS會帶來更糟的結果,不過使用這個訊號樣式會因為須要進行波形解析而造成較長的模擬時間,因此在模擬中不使用較長的測試訊號樣式。

溫度影響可忽略 不計

明顯地,用來製造PCB的材料會擁有不同的溫度擴展係數,不過典型資料應用的溫度範圍通常不會超出-40~+85℃的限制,在這個溫度範圍內,PCB材料的尺寸相對變化低於1%,同時對於差動式的走線設計,兩個走線所受到影響的幅度應該相同,對走線長度如此微小的影響對XFI資料通道的訊號完整性而言相對地也不重要。同樣地,走線寬度也和長度一樣會隨著溫度變化,但是它所產生的影響相對於標準製造過程中對走線寬度控制的實際限制來說基本上可以被忽略。

受到銅以及FR4材料溫度擴展係數差異的影響,貫孔可能會受到擴張介電質的壓力,這可能會威脅到PCB機構的完整性,甚至造成超薄電路板上的貫孔發生破裂,引發本身發生斷續失效,其中最關鍵的製程步驟為焊接動作,它會將PCB的溫度提高到+185℃,不過除非破裂問題發生在PCB的生產過程,否則溫度的改變並不會影響到XFI資料通道的高頻特性,因此將不再對溫度進行進一步討論。

善用工具 XFI通道模擬有助拿捏訊號品質

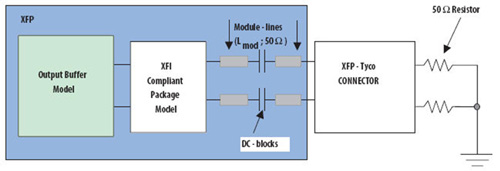

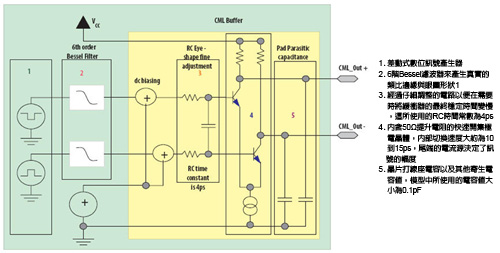

XFI通道經過模擬以便找出以上所討論的各種特性如何影響到訊號的形式與品質,在這裏,XFI通道被分割成由多個元素組成的模型。圖2中的圖形顯示XFP模組的接收部分經過模型化以帶來XFI相容通道的模擬,其他有關XFP接收器輸出緩衝器模型的詳細資料可以參考圖3,由圖中可以看到電流模式邏輯(Current Mode Logic, CML)緩衝器模型以符合XFP MSA的輸出入緩衝器規格。

|

| 圖2 XFI通道模型的構成元素 |

|

| 圖3 針對XFI模擬所架構的CML輸出緩衝器量化器圖 |

慎選XFP模型構成元素

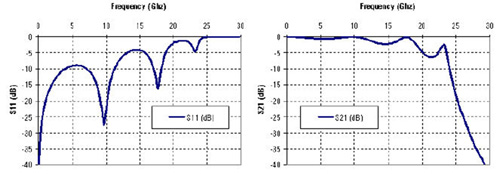

在進入XFP模組中的傳輸線之前,訊號必須由晶片座流經晶片包裝,圖4顯示了用來代表矽晶片與量化器表面黏著技術(SMT)接腳間包裝所產生的寄生內容,初步量化器晶片包裝模型的散射參數S11與S21,在這裡可以說包裝模型已經符合XFI資料通道的效能要求,所使用的初步模型採用RLC階梯方式。

|

| 圖4 量化器晶片包裝模型的S11與S21參數圖,這個模型採用RLC階梯方式。 |

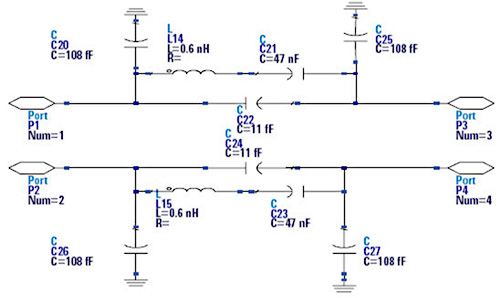

採用表面黏著方式的直流遮蔽可以將XFP模組電源電壓與主控電路板上SerDes的電壓進行去耦合,圖5顯示模擬中所使用直流遮蔽電容寄生效應的等效電路。 在XFI通道模型中插入可插式連接器Spice模型,相對於RD+/-訊號的接腳使用了兩個50Ω電阻進行終端。

|

| 圖5 直流遮蔽電容的寄生圖形 |

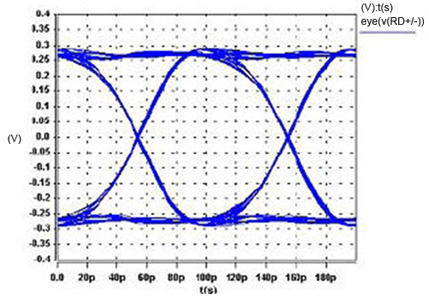

其他所有連接器接腳都進行接地,並在XFP接收器模型使用10Gbit/s 27-1 PRBS位元串流訊號樣式進行激勵時執行模擬動作,差動式波形由主控端XFP模組連接器的兩個接腳RD+與RD-間取得,圖6為最後的眼圖(Eye-plot)結果。

|

| 圖6 使用完整連接器模型的XFI通道模擬結果 |

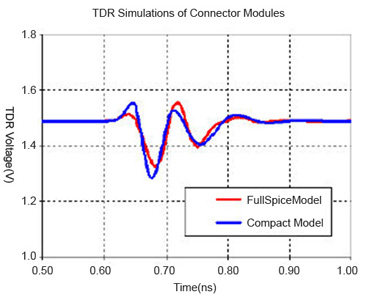

由於XFP連接器模型的複雜度相當高,因此模擬的時間也相對較長,為了節省處理時間,在此架構了這個模型的精簡版本。精簡模型是一個忽略接腳間耦合效應的等效單線式模型,因此不能用來進行連接器感應串音干擾的分析,不過它還是能夠精確地描述由連接器所造成的阻抗不連續性。

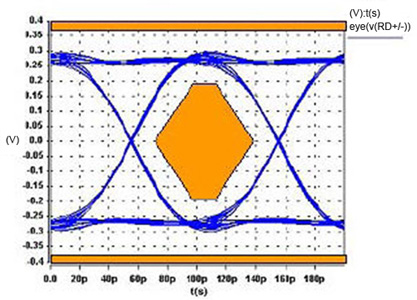

從圖7可以看出兩個不同連接器模型的時間領域反射計響應模擬結果,其中兩個模型的相似性並不差,同時也可以由XFI通道模擬結果,如圖8中加入符合XFI眼圖遮罩的結果眼圖證實,可以看出,精簡模型的眼圖相當接近使用完整連接器模型的結果。此外,圖8中的眼圖將以XFI連接設計參數函數的方式做為眼圖關閉的量化評估參考。

|

| 圖7 完整Spice連接器模型與精簡連接器模型的TDR模擬結果 |

|

| 圖8 使用精簡連接器模擬結合符合XFI眼圖遮罩的模擬圖 |

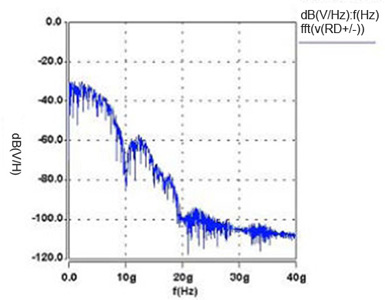

圖9為模擬訊號樣式的頻率內容,是由XFP接收器所發出27-1 PBRS模擬訊號的傅立葉轉換,可以看出,高於20GHz的頻率對接收器模型輸出訊號的影響並不大,如前面所討論,對於某些資料格式,檢查頻譜的低頻範圍與驗證高頻效能一樣重要。

|

| 圖9 由XFP接收器所發出27-1 PRBS位元串流的頻率內容 |

對SONET資料格式來說,可以允許長達72個位元的連續1或0,因此通過通道的最低頻率可以使用方程式f_low=BitRate/(2×N)來加以預測,其中N為最大可能相同連續位元數,因此,對於OC-192 SONET資料樣式,就大約等於69MHz。

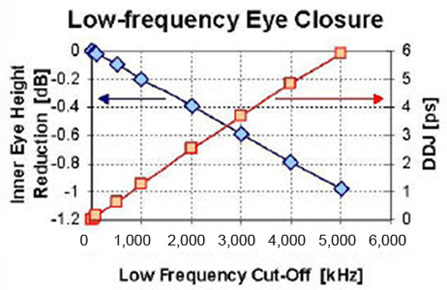

XFI通道的低頻截止處必須要遠低於69MHz,以便讓連線能夠在SONET的資料格式下使用,不過就算截止頻率相當低,還是會對資料相關抖動(Data Dependent Jitter, DDJ)以及眼圖封閉造成影響,其中最大影響會發生在連續長序列的1或0,若進行資料相關抖動的分析並降低內部眼高,可達到允許最長72個相同位元的連續序列成果,這些最糟情況的計算結果以10Gbit/s SONET資料樣式截止頻率的函數表示,請參考圖10。

|

| 圖10 低頻截止頻率對DDJ資料相關抖動以及內部眼高的影響 |

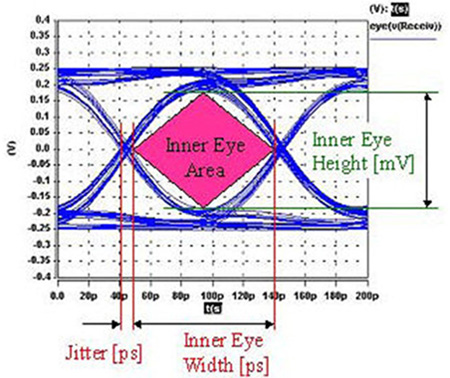

接下來把焦點放在XFI通道設計的高頻部分,在開發出適合的基礎模型後,進行模擬以便對照應用到實際設計上,為了能夠將以上所提各種不同參數對電氣眼圖的影響加以量化,測量在瞬間變化模擬執行時的眼圖上進行,並與圖8中的參考眼圖進行比較,圖11中的眼圖顯示了測量的進行方式。

|

| 圖11 顯示測量參數的模擬電氣眼圖 |

從上文可以看出,各種設計10Gbit/s高速串列差動式電氣通道訊號的方法各有利弊,而微帶線、帶狀線也各自會帶來不同影響。若搭配適當之差動式串列收發器與串列解串列晶片,將可強化電氣通道之布局設計,並提高高速傳輸之運作效能。 簡言之,隨著市場需求漸起,高速串列訊號傳輸的技術瓶頸也隨之逐漸克服。在各界戮力以對下,相關訊號傳輸效能勢必可望不斷倍增。

在探究完影響高速資料連接的訊號完整性的諸多因素後,下期將繼續針對微帶線或帶狀線走線的優缺點進行剖析,並進行範例實作,盼能對讀者帶來更多幫助。

(本文作者任職於安華高科技)

| 參考資料 |

[1]XFP多重來源協議1.0版.

[2] 電子電路設計藝術(The Art of Electronics)第二版第五章:"主動式濾波器與震盪器",Paul Horowitz與Winfield Hill合著,牛津大學出版社.

|