電視機的發展在過去15年來進步神速。諸如液晶顯示器(LCD)和電漿顯示器(Plasma)等平面面板技術的出現,讓冷陰極管(CRT)和背投影產品逐漸消失。螢幕尺寸快速增加而厚度卻越來越薄,讓電視機變成可以掛在牆上欣賞的藝術品。然而,不只是從外觀上可以觀察到的螢幕構造產生變化,內部的影像介面也不斷地在改變。類比已經被數位所取代,為使用者帶來一種無與倫比的觀賞經驗。

其實,就跟每種新興技術一樣,消費者的需求遲早會超過系統能達到的性能。當影像格式和螢幕尺寸變大時,用來支援它們的頻寬也必須隨之增加。這就在現有的設計上增加了新的需求,一種越來越難滿足的需求。

電視技術不斷演進

約翰洛吉貝爾德(John Logie Baird)在1925年首次展示行動影像的傳輸,這個突破性的進展被公認為是電視的首次真正展示。後續的幾十年間,這個系統無疑地有許多更精細的改進,包括廣播方式的進步,但電視的基礎仍然相同:接收一個類比訊號然後顯示在玻璃螢幕上。彩色取代黑白、背投影產品補足冷陰極管的不足、纜線和衛星變成傳輸的媒介,但是最終電視還是一台類比的顯示器。

所有的一切在1990年代中期全世界第一台高解析度平面電視出現後發生了變化。使用電漿技術的新電視,厚度只有CRT的一小部分。緊接著很快出現新的介面技術,例如數位影像介面(DVI)和高畫質多媒體介面(HDMI),這些都預告了類比電視轉變成數位電視的趨勢。

然而,這只是個開端。HDMI讓播放格式尺寸不斷增加的高解析度影像可以在家用娛樂系統上顯示。對頻寬的要求開始增加,現有電視構造的限制開始越加明顯。

平面電視由四部分構成

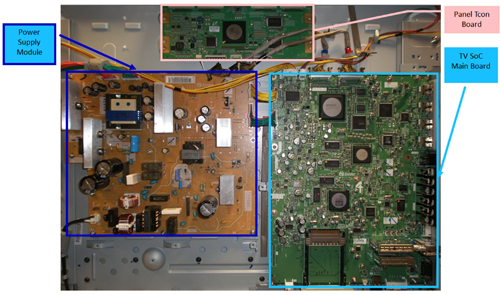

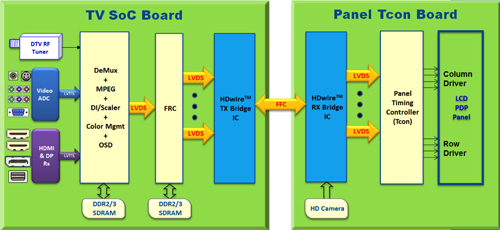

如果簡單檢視平面電視的主要零件,將會發現顯示面板、時序控制器(Tcon)板、影像處理器板和電源供應模組這四部分(圖1)。顯示面板包括電漿、液晶顯示器、有機發光二極體等顯示技術;時序控制器板用來驅動面板;而影像處理器板上有系統單晶片(SoC),負責把自訊號源接收進來的資訊流轉換成Tcon的正確格式。

|

| 圖1 一般平面電視拆解圖 |

當平面電視的尺寸還很小的時候,SoC和Tcon可以固定在同一塊印刷電路板(PCB)上。不過,當螢幕尺寸增加後,繼續用一塊大型的PCB就變得太昂貴也太重,因而逐漸形成兩塊板子的解決方案。

當SoC和Tcon放在不同的PCB後,就需要一種相互連接的技術來傳輸它們之間的訊號,在1990年代中期,電視製造商採用低電壓差動訊號(LVDS)介面技術做為實際上的標準。

高解析電視風行 LVDS限制漸浮現

LVDS是由美國國家半導體(NS,現已併入德州儀器)在1990年代初所研發的,於1996年首次使用在電視機中。16年後,它仍然是此項應用的主導技術。這項技術的真實名稱實際上是平面顯示器連結(FPD-Link),但因為它是LVDS的第一個大型應用,因此很多工程師將FPD-Link和LVDS當作同義詞使用。

LVDS被定義在ANSI/TIA/EIA-644-A標準中,這是由資料傳輸介面委員會TR30.2於1995年發展的標準。它是低電壓、低功率的差分技術,主要使用在點對點和多點連接的接線驅動應用。此標準建議最大數據率655Mbit/s,但最近推出的高速LVDS速率已增加到約1.2Gbit/s。

LVDS是設計為每個時脈可驅動七個資料位元。每五條資料通道就需要一條單獨的時脈通道,而這就表示要增加大約16%的纜線固定成本。

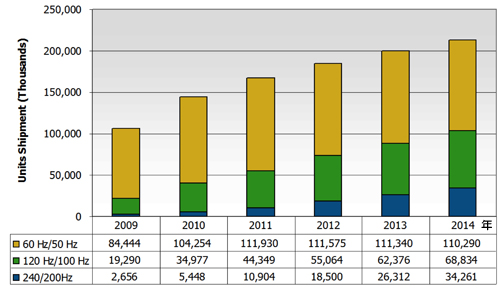

LVDS已經在業界盛行多年,近來電視解析度和播放格式的進展已經導致頻寬需求大幅增加。具有60Hz和120Hz更新頻率的電視已經在商店內販售(圖2),2012年的國際消費性電子展(CES)甚至還陳列了4K×2K的電視。因此,用來支援這些頻寬的LVDS線路的數目大增,導致電視製造商須負擔更多生產上的成本和複雜性(表1)。

|

| 圖2 60/120/240Hz電視出貨預估 |

隨著市場預估有較高更新頻率的電視出貨數目會穩定成長,LVDS的限制將變得更加明顯。成本壓力和工程限制將會迫使電視製造商尋求替代的解決方案。

替代方案爭出頭 HDWire露鋒芒

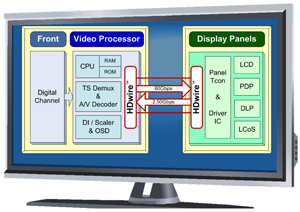

為因應即將到來的成本壓力和工程限制,許多廠商開始尋找可替代LVDS的方案,例如傳威(TranSwitch)所研發的HDwire。HDwire使用進階的訊號技術,可以用低價且簡單的扁平電纜取代多條LVDS纜線。這項技術預計能以少量線材和更簡易的系統設計簡化面板的相互連接方式。

|

| 圖3 HDwire系統應用 |

HDwire介面可包含多達十二條、每一條可支援5Gbit/s的順向資訊通道,和可支援1.25/2.5Gbit/s的可選用的反向資料通道。這個介面可以支援每個色彩12位元、解析度4K×2K、更新頻率120Hz(53.5Gbit/s),以及每個色彩12位元、解析度8K×4K、更新頻率30Hz(53.5Gbit/s)的顯示面板。HDwire提供更低的電磁干擾(EMI),因此不只簡化系統設計還能降低成本。此外,HDwire被設計為可透過FR4 FPCB、FFC軟排線和現有的標準纜線,在使用最低功耗、低位元錯誤率(BER)的情況下即可讓超高速影像運作(圖3)。

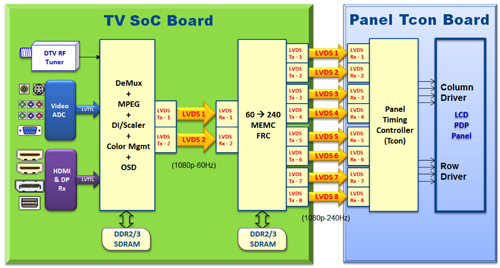

和LVDS解決方案相比,要實現1,080p、240Hz、12位元色彩產出與26.7Gbit/s的顯示規格,HDwire只需要一半頻寬,顯見其簡單及具成本效益的優勢(圖4)。

|

| 圖4 針對1,080p/240Hz電視(SoC板附畫面頻率變頻器)的LVDS解決方案 |

HDwire有一項比LVDS更佳的優勢,其連結包括一條高速反向通道,可以自Tcon板將數據傳送到SoC板。一般這個功能是透過使用I2C執行,但是這個通訊協定的頻寬量有限,每秒只有數個百萬位元。HDwire採用的反向通道是以與順向資訊通道相同的技術為基礎,資料傳輸速率可達到1.25/2.5Gbit/s。這個高速反向連結有許多用處,例如可以用來將電視前框上的照相機連接到應用處理器,可以讓整體視訊會議的流程更順暢。觸控面板的資料也可以透過反向通道傳送,讓使用這種新興功能變得更簡單。

使用更便宜纜線

HDwire技術的關鍵優勢之一就是可以透過低成本的纜線完成高速的訊號傳輸。排除對高成本LVDS排線的需求,使得該解決方案省下不少成本。TranSwitch的技術展示是使用軟排線(FFC)作為高速媒介,HDwire的設計可以透過這種最長達1米(m)的簡單線材運作。FFC和線材端子的相加成本,比具備相同效用的LVDS成本要低很多,不須要降低任何最新款螢幕必備的高解析度畫質,就能輕易省下這些成本。

維持低功耗

隨著消費者的環保意識日漸增加,電視的消耗功率現在也變成前所未見的熱門話題。螢幕尺寸的增加,加上實際的顯示技術,意味著現在購買新電視時,螢幕的消耗功率變成一個重要的考量因素。

能源之星(Energy Star)在最近2012年5月發表的規格(版本5.0)中,將32吋電視的開機時最大功率限制為55瓦(W),而50吋電視則是108瓦。相較之下,3.0版本的數字高達120瓦和353瓦。這表示在分配系統的功率限額時,電視中的每個電路都會受到嚴密的檢查。

幸好,HDwire技術的功率消耗本來就很低。此設計使用預驅動器,以比不歸零編碼(NRZ)還低的頻率運作,可減少訊號源的功率消耗,幫助減少二重像和纜線輻射。此外,其訊號傳輸方法是使用多重訊號層,多數訊號是在低於完全電壓的層產生,這也更加降低系統的功率消耗。

具備EMI優勢

HDwire除了單純功能上的優點外,這項技術在EMI方面也大幅地改善。EMI是雙絞線發射出來的輻射電場。它是因為生產纜線時的小瑕疵所造成的,卻會對電視設計者造成大問題。發射出的干擾會造成電視機內部的電路及鄰近的電器受到干涉。因此,降低EMI成為消費性電子(CE)產品的關鍵要求也就不令人意外。一條雙絞線共用訊號發射出的輻射電場強度可以下列公式表示:

E=從距離線材R的位置測出的電場強度(V/m)

f=共用電流零件的正弦波頻率(Hz)

Icomm=共用電流(A)

Len=散發輻射的雙絞線長度(m)

R=從線材到電場量測位置的距離(m)

因為線材不是完美的(如差分對內延遲差),差動發射訊號造成共用訊號(SCD11)。差動發射漏電至到共用訊號,可以透過散射參數SCD11、SCD22、SCD21和SCD12量測出來。根據前述公式,共模訊號輻射成為共模訊號的EMI。共模訊號的EMI比差模訊號的EMI更強,在EMI量測中更加重要。

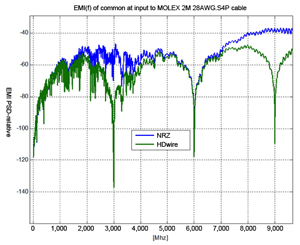

|

| 圖5 HDwire EMI表現與NRZ EMI表現之比較 |

HDwire使用先進的訊號傳輸技術,與其他技術使用的NRZ相比,EMI可大幅降低。分析顯示,與NRZ相比,EMI輻射可降低約5.5dB,降低對抑制EMI技術的需求,也能夠幫助簡化電視設計。EMI輻射和發射器頻譜和頻寬具有等比例的關係,HDwire的EMI表現改善,可以歸因為以下幾項重要因素:訊號傳輸頻寬比NRZ少、功率強度比NRZ低及升/降時間比NRZ慢。圖5說明了EMI的改善成果。

為了判定EMI成果,首先必須要使用網路分析儀量測一般雙絞線的S參數。這個S參數會使用在Matlab的模擬中,以決定產生共模EMI的差模-共模訊號的效用。從圖5中可看出,結果顯示HDwire訊號傳輸在關鍵的2.5G3.5GHz頻率產生非常少的EMI。

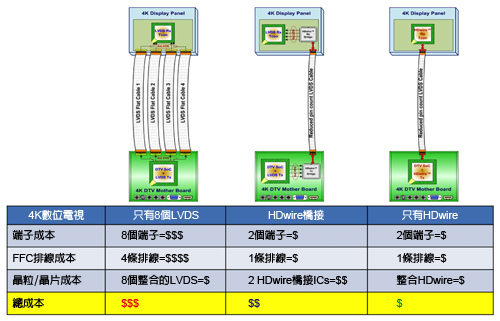

成本優勢顯著

HDwire優於LVDS的技術優勢已經在前述文章中詳加討論過。不過,許多電視製造商感興趣的是轉換到這項新技術可省下的成本。圖6顯示一台4K×2K電視的HDwire和LVDS的一般生產成本的比較。

|

| 圖6 使用HDwire的4K電視系統的節省成本 |

|

| 圖7 HDwire電路圖 |

確切減少的成本無疑地是取決於許多變數(例如數量),但是上述圖示可用來說明哪些部分可省下成本。使用HDwire橋接IC結合現有的SoC和Tcon晶片可以減少多達一半的零件成本。不過,當個別整合HDwire發射器和接收器IP(矽智財)核心在SoC和Tcon時,可能省下的成本會大大地增加。

圖7是HDwire橋接IC的電路圖,其具幾項關鍵特色,如整合六條順向資訊通道(可擴充至十二條),每條通道傳輸率5Gbit/s,以及一條反向資訊通道;支援最大達100公分的FPCB,BER低於10-12;符合顯示面板的大範圍畫素時脈;支援60Hz、120Hz和240Hz的面板更新頻率;非同步HDwire輸入和4通道LVDS輸出;虛擬隨機模式產生電路(PRBS);支援低擺幅LVDS以降低EMI和功耗;整合8051微控制器(MCU)和隨機存取記憶體(RAM)和唯讀存取記憶體(ROM);具備功率下降模式。

圖8則說明如何將HDwire橋接IC整合到現有的板子設計中以支援此新介面。

|

| 圖8 一般使用橋接IC的HDwire系統 |

HDwire也可透過IP核心的方式提供,讓SoC和Tcon廠商可以將此新技術整合到他們的IC中,代表這些裝置可以供應給內含HDwire的電視/面板製造商。如此的整合方式帶來的成本優勢及附加價值對生產商將會非常有益。

各種替代技術逐一問世

既然已知LVDS的限制,那麼出現其他與LVDS競爭的技術也就不足為奇。以下是目前所知的可替代LVDS的技術,包括HDwire、V-by-One/V-by-One HS、eDP、iDP。

| ‧ |

|

| |

V-by-One是由Thine電子公司研發的技術,用以取代LVDS。雖然目前V-by-One的市場占有率還很小,但是已經有一些電視製造商轉換到這個相對新的技術。樂金(LG)是其中一個製造商,他們在2011年宣布改用V-by-One。Thine意識到顯示器格式需要更大的頻寬,在2011年12月發表V-by-One的1.4版V-by-One HS。此規格的HS版本支援最高4Gbit/s資料傳輸率(有效傳輸率3.2Gbit/s)。這項技術的關鍵特色包括:可擴充順向資料和時脈的串列/解串列器(SerDes)組數量,目前IC支援二條順向通道;支援最高4K×2K、更新頻率240Hz、每個色彩12位元(使用於多個IC上的三十二條通道);嵌入式時脈,接收器不再需要參考時脈。 |

| ‧ |

|

| |

嵌入式DisplayPort(eDP)是視訊標準協會(VESA)推出以DisplayPort標準為基礎的技術,用以取代LVDS。1.0版本於2008年12月推出,2011年2月發表1.3版本。eDP似乎是在筆電市場較有進展,在電視領域目前則能見度不高。這項技術的關鍵特色包括:支援最高順向通道的四組SerDes及時脈,每組傳輸速率5.4Gbit/s(有效資料傳輸率為每組4.3Gbit/s);有一條做為控制功能使用的1Mbit/s的回傳通道;目前支援的最大面板解析度為8位元4K×2K@60Hz。 |

| ‧ |

|

| |

iDP(內部DisplayPort)是另一個VESA標準,此規格的版本1於2010年4月發表,用以取代LVDS。此技術是以簡化的DP通訊協定為基礎。iDP的關鍵特色包括:每條通道資料傳輸率固定為3.24Gbit/s;沒有AUX通道;嵌入式時脈(8B10B編碼);彈性頻寬(每資料庫最多16組,可超過1個資料庫);根據VESA網站資料顯示,iDP是以大型螢幕顯示器內的連接為目標,而eDP則是針對筆記型電腦的GFx和面板間的連接。 |

自從iDP標準在2010年第一次發表後,就沒有其他新版本繼續發表。而且意法半導體(ST)網站上和iDP有關的最新新聞發布是2010年11月(LVDS-iDP Bridge ICs)。因此,這項技術看來似乎已經暫停了。表2為和LVDS相關的每項技術的比較表。

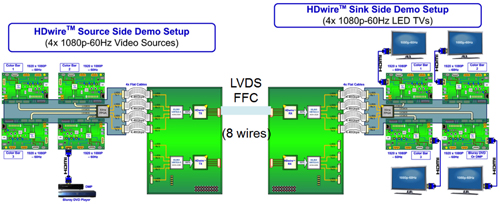

HDwire的每個IC總計有30Gbit/s的原始頻寬(多晶片結構可擴充至60Gbit/s),提供比其他任何競爭者更多的產量。在同類型技術中,反向影像資料通道是一個獨特的特色,讓HDwire增添更多產品價值。使用嵌入式時脈,毋須在接收器中使用振盪器,所有纜線中的排線都用來傳輸資料,因此可減低傳輸的固定成本並簡化接收器時脈結構(圖9)。

|

| 圖9 HDwire實作4K×2K、60Hz畫面更新率顯示器的展示 |

降低生產成本才是贏家

隨著更高解析度的電視和播放格式的推出,對於可取代LVDS的需求已明顯增加。這些播放格式所需的頻寬表示需要多條LVDS排線,因而增加電視的生產成本。目前市場上有不少互連技術,而結合了具附加價值的特色和傑出EMI表現,並可以透過單一低價纜線運作的技術,將會是未來取代LVDS的最佳解決方案。

(本文作者為TranSwitch技術市場部門經理)