不斷改良的製程帶動半導體的整合,傳統上被視為是驅動電子產業前進的關鍵力量。對晶片設計師而言,提供更多的功能、更快的執行速度、更小的體積、更低的成本以及更低的功耗以滿足客戶的需求是通行已久的準則。

SoC已無法一體適用各種設計

不過,該規則已有所改變。雖然晶片架構已採用90奈米以下的製程,並朝著65和45奈米邁進,但是越來越多具備影音媒體性質的消費性及專業性產品,特別是可攜式裝置,需要設計師賦予更多樣的功能,利用最先進的數位互補式金屬氧化物半導體(CMOS)製程將這些功能全部整合進單一晶片中已不適合。

為提供終端消費者所需要的功能,設計師必須要能在符合成本效益的條件下執行高效能的類比和混合訊號功能。因此,如何有效地分割系統則成為設計師最重要的課題。根據各應用需求的不同,採用的作法也會不同,例如系統單晶片(SoC)整合、多晶片解決方案,或是多晶片系統級封裝(SiP)等。而選擇的依據則是如何在成本、上市時間、功能彈性、功耗以及設計的複雜度之間達到最佳的平衡。

乍看之下,似乎只要將所有技術整合在單晶片上問題就解決了。然而,現在已有越來越多的理由說明為何情況已有所不同。首先是市場的驅動力量更勝於技術上的改良,現今市場上有眾多的可攜式產品,產品差異化相當重要。每種產品都有不同的設定或要求,於是一視同仁的整合方案不再適用。

從使用者的觀點來看,產品差異化更是關鍵所在。一項可攜式產品要在市場上引起注意,終端消費者的使用經驗相當重要,而產品的多媒體功能、效能及電池壽命都會影響消費者的觀感。系統分割不僅能提供多樣的產品特性,而且當市場的需求有所變化時,還能提供最佳的解決方案。

事實上,缺乏設計彈性不僅不利於產品的差異化,而且會阻礙設計團隊面臨挑戰及問題時的能力發展。大型SoC的研發費用現在都是以數千萬美元來估計,因此,針對不同需求所做的改變幾乎成為不可能的事,這對於設計團隊針對問題還有相關功能的改善能力是負面影響。

先進製程對混合訊號設計助益有限

第二個問題則是SoC整合並不能讓混合訊號功能從先進的製程上獲得太多的好處。過去的許多例子證明,要將新功能整合在單晶片中,通常都相當具有挑戰性,且成本也相當昂貴。然而隨著時間的演進及製程的改良,每個功能的成本、功耗及所需空間都有顯著的減少。

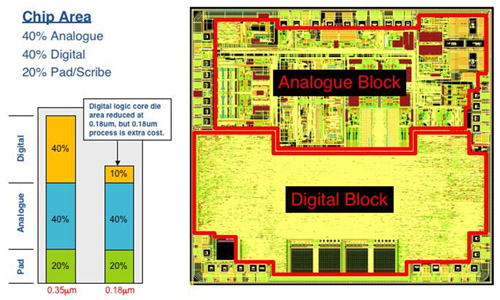

先進製程並沒有為混合訊號功能帶來太多好處。歐勝(Wolfson)最近進行一項研究,將一個現有設計的製程由0.35微米改良至0.18微米會產生哪些改變。

就面積而言,原始晶片的數位電路與類比電路各占40%,而點孔/切割道(Pad-and-scribe)電路占20%,此為典型的混合訊號晶片(圖1)。

|

| 圖1 對於類比電路而言,先進製程並不會帶來太多好處。 |

當製程改良至0.18微米時,數位電路的面積大約縮減75%。然而在未經最佳化的情況下,其他部分的電路面積依然沒有太大改善,因此整體面積大約減少30%左右。所以就晶片成本來看,如果採用0.18微米所增加的費用低於30%,則製程改良才有意義。

不同電壓需求增加整合難度

至於第三個整合的障礙則是要將各種不同的電路功能整合進一個多媒體裝置,例如一台可攜式媒體播放器(PMP)。數位核心的電壓低至0.6伏特,雖然還是須執行額外的1.8伏特和3.3伏特電路。從電源管理的觀點出發,該系統要能處理鋰電池所產生的2.7~4.2伏特的電壓水準。

周邊的附加功能讓狀況更加複雜。USB連接需要4.2~5.5伏特,而TFT驅動元件通常需要12伏特。

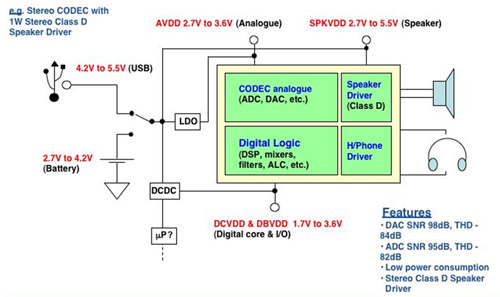

若要達到高品質音訊所需的訊噪比,則2.7~3.6伏特的電源供應是絕對必要的;然而要產生每聲道1瓦的揚聲器力道則須使用高達5.5伏特的電壓(圖2)。

|

| 圖2 SoC設計必須支援多種電壓和電晶體節點。 |

不同的電壓需求不僅讓SoC設計師面臨高度複雜的工作,也增加晶片製造難度。這樣的裝置在同一片晶圓上需要多達四個電晶體節點,但卻會增加製造和測試的難度,且晶圓成本也會增加,除此之外,良率還會下降,風險也會跟著增加。

複雜度的提升不僅會影響上市時間及成本,更會影響到產品的效能。採用SoC方式的設計團隊必須默默承擔產品品質不良的後果,而這可藉由噪音分貝和串音干擾(Cross-talk)測量出來。

姑且不論SoC所面臨的諸多挑戰,至少對數位設計師而言,產品必須利用最先進的技術去完成,而更快、更小、更低功耗及更多功能的電路發展,並不能因為混合訊號功能的日漸重要而有所停滯。

系統分割有助效能最佳化

若要解決上述問題,可藉由系統分割的方式來獲得電池壽命、體積、功能和效能的最佳組合,將這些技術適當分配以實現整個系統的最佳效能。

例如將PMP之類產品分割為多個子系統,基礎的數位控制和訊號處理功能,最好是採用最先進的製程技術,並且以0.6伏特的核心電壓運作。一般而言,行動裝置的DDR是在1.8伏特運作,至於記憶體技術,則須選擇適合其需求的最佳化製程技術。

在周邊部分,射頻(RF)電路一般會有其特定需求,可採用RF CMOS製程或是更專門的砷化鎵(GaAs)與矽鍺(SiGe)技術來滿足。此外,比較特別的是顯示裝置的驅動元件,其所需的電壓高達12伏特,多半是採用覆晶玻璃覆晶(Chip-on-glass, CoG)技術加以實現。

數位製程/混合訊號技術雙管齊下

針對這四種特定功能,必須要再加上混合訊號技術,才能將USB和乙太網路、觸控螢幕介面、音訊編解碼器、揚聲器/耳機驅動器、高傳真編解碼器及電源管理等眾多功能結合起來。將這些功能整合於單一晶片中,採用的可能是某種產業標準連接介面,例如行動產業處理器介面(MIPI)協會的串列低功耗晶片間媒介匯流排(SLIMbus)。

當然,這五個部分並非不能變通,一個只需要核心處理和USB介面的系統,最好還是採用單晶片整合的作法,而不是採用一個核心處理器加上混合訊號輔助晶片的方式。另外,混合訊號晶片的供應業者必須確保能在晶片上提供客戶所需的功能,讓他們能針對消費者的需求設計出適合的產品。

在某些情況下,並非只是簡單地選擇採用SoC方案或是組合元件方案。利用SiP技術也能提供必要的彈性和實現最佳化,即使在功耗或晶片面積上,其效率並不如SoC,然而許多設計團隊認為就算是將增加的封裝和處理成本考慮在內,SiP仍不失為一個有效的解決方案。

因此,未來所採行的方法依然會存在分歧,針對此五種基本功能,設計師會根據應用所需來進行切割,數位製程仍將會持續的改良,而混合訊號設計師還是會根據客戶的需求來組合和搭配各種特性,以創造出消費者心中的產品差異性。

(本文作者為歐勝AudioPlus電源管理產品線經理)