近年來,多功能手機的發展蔚為風潮,手機製造廠商為了在市場上搶占先機,提高占有率莫不使出渾身解數,開發出各種豐富多樣的功能,以明顯區隔對手的產品。可是隨著搭載元件數量的急遽增加,靜電釋放(Electrostatic Discharge, ESD)所帶來的後遺症正悄悄地浮現出來,所以如何有效因應就成了當務之急。

手機平台有兩個顯性的進展處於現在進行式。其一是手機的多功能化越來越明顯。有MP3、照相功能、全球衛星定位系統(GPS)、觀看行動電視已經不是什麼大新聞。

再來,另一個特徵就是大型積體電路(Large Scale Integration, LSI)的驅動電壓,有越來越往下的趨勢。這一點就更容易理解了,功能越多,電池的續航力卻沒有呈現相同比例的上升速度。唯一可行之道,當然就是省電化。地球暖化,環保當道,綠色電子將是必須走的道路。

在如此的背景之下,ESD引起的麻煩可能性大增。不難想像,ESD元件的使用機會必然大幅增加,而且又有電磁干擾(Electro Magnetic Interference, EMI)問題待克服,因此兩者組合的解決方案也逐漸成形。這一點可以從手機的各個部分清楚看出,如顯示器,有ESD保護和EMI濾波器,記憶卡有ESD保護、EMI濾波器以及拉高電阻,按鍵部分和底部連接器、USB介面、用戶識別模組(Subscriber Identity Module, SIM)卡、耳機線路、相機模組都有ESD保護和EMI濾波器,天線也有ESD的保護問題。

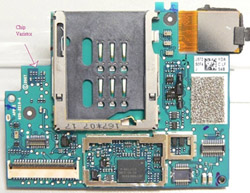

|

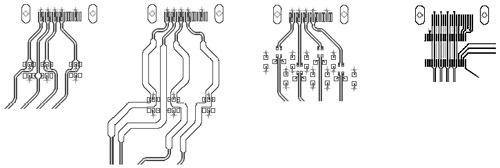

| 圖1 iPhone採用分散式元件設計方式降低ESD |

再來看諾基亞(Nokia)的E65。液晶顯示面板與訊號線連接器周邊,共用了三個覆晶(Flip Chip)的元件,相機模組的連接器周邊用了一個,記憶體暨SIM卡子板與主板連接器周邊各用一個,而USB資料線和電源接續連接器也使用覆晶的保護元件。而iPhone,卻是活用個別的被動元件,採用典型的突波吸收器(Varistor)與二極體(圖1)。從這兩個案例可以得知,廠商的設計思想決定了元件的採用方式。

以摺疊式手機的案例來說明。液晶的顯示部分都是以軟板(Flexible Cable)來連接,而上下蓋的鉸鏈(Hinge)的空隙有機會放電而對軟板施以高壓,畫面顯示可能會出問題,對於背光用途的白光LED,也有機會被破壞。

ESD麻煩可能性增加的另一個理由是,與外部資訊存取的輸出入介面增多。記憶卡的插拔,資料傳送連接器的使用頻繁度高,這些都會增大ESD的危險性。因為插拔時,人體電荷高電壓有在連接器放電的可能性。

當機器在朝向薄型化時,一切以工業設計為優先的框體設計,對於ESD的耐性也可能減低,導致ESD對策元件大量電荷放電所利用接地電位的不安定性。ESD的解決對策向來是以齊納二極體、突波吸收器為主,而同時也必須面對EMI的問題。因此,使用ESD與EMI濾波器一體化的覆晶零件也不少,使用上以歐商為主。簡單來說,作為ESD保護元件的突波吸收器和二極體,在開發進展上有封裝面積的減少以及多機能化、ESD保護機能的提升、高速訊號的對應、降低成本、天線的ESD對策六大方向。

減少封裝面積以及多機能化

就封裝面積的減少以及多機能化來說,含括了突波吸收器和二極體共同方式、保護多數的訊號線,或是與EMI部品一體化。一個元件所能夠保護的訊號線數量,一般使用矽(Si)二極體的方式較多。突波吸收器採用到四個的程度,而二極體方式約八至十二條訊號線的元件也見得到。這是歐系廠商的手機經常使用的方式。

EMI濾波器與ESD對策元件一樣,都是各個介面不可或缺的。尤其是一體化對於封裝面積的減少有相當的貢獻。

此外,超薄型的攜帶式終端裝置,都會使用軟板,卻也往往產生天線效應,成為放射雜訊源。想要消除這個雜音,就是利用低通濾波器,亦即EMI濾波器。而從外部訊號輸入配置ESD,也是同樣的情況,所以兩者一體化的想法就此誕生了。

二極體的方式是,可以在矽基板上擺放二極體、阻抗與電容器,可對應四至八條訊號線,這往往是採用覆晶的封裝方式。依據元件提供商的說法,如此一來出貨量年年攀升。

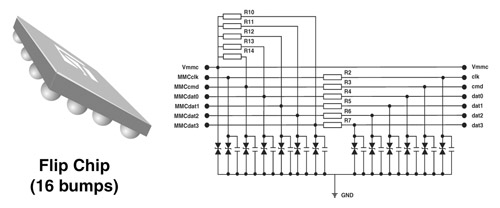

舉意法半導體(STMicroelectronics)的EMIF06-HMC01F2為例,在十六個接點的覆晶封裝內,不僅整合訊號線的二極體與EMI濾波器,還追加了記憶卡用的拉高電阻。晶片大小為1.92毫米×1.92毫米,配置了直徑0.315毫米的接點球狀體,間距則是0.5毫米(圖2)。

|

| 圖2 意法半導體所推出整合ESD的EMI濾波器晶片實品(左)及其內部等效電路(右) |

這些多功能化覆晶接點球狀體(Bump)的間距,往往就決定封裝面積的大小。現在的標準間距是0.5毫米,有些則有0.4毫米的製品。元件的封裝含接點球的高度是0.65毫米,根據廠商的藍圖來看,將進一步朝向0.4毫米、0.3毫米發展,最終將0.1毫米部分埋入基板。

採用覆晶方案的另一個優點是元件與基板之間的寄生電感非常小。如果系統晶片化的趨勢依然持續,未來還會將周邊共通性高的電路收納進來,例如電壓調節器回路等。以上所言乃是在矽上面整合多數功能的具體實例。

在突波吸收器方面,也是朝整合EMI濾波器方向發展。突波吸收器乃是在陶瓷上積層而形成,在積層的同時燒成電感或電容複合元件是其特徵。二極體方式的多機能製品,多是由阻抗與電容所構成。而阻抗在突波吸收器聚集的場合,若插入將損失頗大。同時,電容與電阻的濾波器特性,很難達成急遽的衰減特性,因而利用電感L來替代電阻。

另外一方面,液晶面板或相機模組與基板的連接軟線,須設法抑制800M~2.5GHz通訊頻帶所產生的放射。加上手機電視若內建調諧器(Tuner),在通過影像訊號的同時,必須抑制接收所造成的影響,例如日本的1-Segment就必須確保470M~770MHz有足夠的衰減量。

|

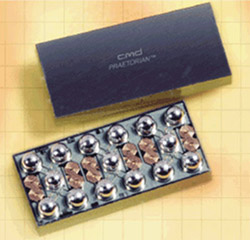

| 圖3 矽上面所形成的電感 |

在產品競爭進化之下,顯示的高精細度化,影像訊號的頻寬更廣,在這個情況之下,由於一體化電感較不會產生電容,且頻率衰減特性更急遽,因此較有利。所以,將介電體相關的電容器與磁性體的電感燒成得到EMI濾波器,並與ESD對策元件組合。在這一方面,日商松下(Panasonic)、京瓷(Kyocera)、TDK等公司都有產品面市。

實際使用時,方法的選擇依個別廠商而定。而二極體的方式,也有產品整合電感的案例,例如美商CMD即有產品在矽上形成電感,插入損失較小,同時具有較高的截止頻率(Cut Off Frequency),並且以卷狀導體的樣式來形成電感(圖3)。

提升ESD保護機能

以保護機能的啟動電壓來說,突波吸收器就比二極體高。有的廠商開始研發下降突波電壓的產品。以TDK的產品為例,將以往的8伏特降至6.8伏特,可以抑制ESD的誤動作。一般來說,減少ZnO的粒子數量可以降低突波電壓,但是流經接地的漏電流會增加是個問題。該公司的對策是改變突波吸收器陶瓷材料用ZnO的添加物來降低突波電壓,而且還能抑制漏電流的增大(圖4和表1)。

|

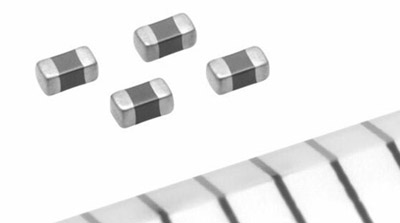

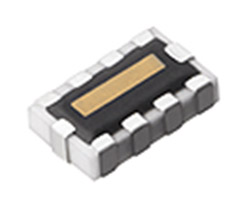

| 圖4 突波電壓6.8伏特的積層突波吸收器 |

|

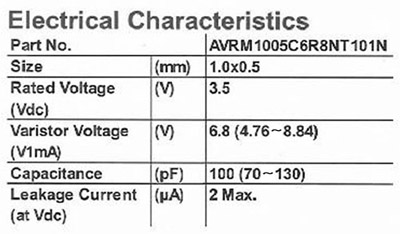

| 表1 6.8伏特的積層突波吸收器的電氣規範 |

因應高速訊號

無論是二極體的方案,還是突波吸收器的方式,兩者的目的都在於降低ESD保護元件的靜電容量。原因很簡單,就是維持插入的高速訊號線如USB等不會產生失真。未來,手機納入高畫質的HDMI介面後將會更加重視這方面的問題。例如,美商晶鐌(Silicon Image)所開發的行動高畫質連結(Mobile High-definition Link, MHL)僅有五端子可以傳送HD影像視訊與音頻訊號,並維持HDMI的相容性。

|

| 圖5 靜電放電抑制器 |

即使,HDMI Licensing, LLC所制定的Type C連接器就是針對可攜式產品而來,但是十九端子數量對於手機而言還是太多。邁入HD時代,高速傳輸乃是必然。僅就靜電容量場合來說,突波吸收器低於1pF的產品已經看得到了。除此之外,降低成本必定是電子資訊產品遵循的定律。

針對天線的ESD對策

|

| 圖6 靜電放電抑制器陣列 |

放眼望去,多數CMOS積體電路(IC)的耐壓在200伏特以上,而直接連接到天線的開關積體電路,多是採用砷化鉀(GaAs)等化合物半導體,耐壓低於100伏特的場合不少。由此可知,天線的ESD對策也是很重要。

收發頻率超過800MHz時,靜電容量過大的話會引起接收波形的失真。通常,不採用二極體或突波吸收器,而改採用電感。但是,市面上也有開發0.8pF的二極體元件,被運用於100MHz以下FM送收天線的ESD對策。

市面上使用電感來實現ESD的原因有二,其一,阻抗的整合性若是沒有處理好,插入損失會變大。如今,多頻手機處處可見,天線的阻抗整合就變得有其必要。若能滿足最適當的條件,即能獲致ESD對策的預期效果。另一個課題是,靜電所施加的電壓變大,對於保護對象的元件或是電路也會跟著變大,一旦峰值電壓(Peak Voltage)過高,將會讓積體電路發生誤動作甚至可能發生破壞。

|

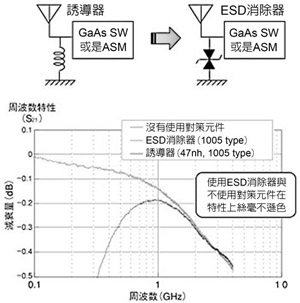

| 圖7 使用電感與靜電放電抑制器在天線對策的比較 |

|

| 圖8 使用ESD元件與否在配置上可能會有差異 |

針對這些問題,松下元件開發出靜電放電抑制器(ESD Suppressor)的產品,容量0.1pF非常小。在氧化鋁(Alumina)的基板上利用金屬作成空隙,然後再上面印刷分散金屬粒子的樹脂。當電壓超過門檻值時,僅有在金屬粒子之間可以導通(圖5~7)。除此之外,採用不同的ESD元件,對於繞線的布局也會有所差異(圖8)。