單一事件效應(Single-even Effect, SEE)對於印刷電路板上的IC元件影響,將導致包含航太各種應用系統的故障問題。因此FPGA業者利用在FPGA中加入數位訊號處理器(DSP)累加方塊,即可有效緩解SEE造成的元件錯誤。

當太空中的高能量離子撞擊IC基板時,衝擊會造成IC電路的瞬間電流/電壓脈衝。若脈衝大到足以改變電路上的數據時,此現象便被統稱為SEE。有兩類SEE是RTAX-DSP設計人員會特別關注,第一類為單一事件干擾(SEU),第二類為單一事件暫態(SET)。

SEU大概是最為人所了解的一種SEE。SEU是指當有足夠的電荷聚集在靜態記憶體單元中,包括暫存器、靜態隨機存取記憶體(SRAM)單元等時,產生的電壓會使記憶體狀態改變(位元翻轉)。這些錯誤或干擾會一直持續,直到下一次新數據被寫入記憶體單元為止。而當衝擊離子在元件的組合電路中誘發電壓脈衝時,此效應便稱為SET。如果誘發電壓超過切換閾值,並具有足夠的脈衝寬度,錯誤數據就會在電路上傳送。由它名稱可知,這些錯誤只是暫時發生,脈衝寬度大約為500毫微微秒(ps)。

常用ECC緩解SEE

有好幾種技巧可用來消除數位邏輯中的SEE。SRAM區塊上的SEU效應能透過採用記憶體的錯誤偵測和修正(EDAC)方法來緩解。最常用的是錯誤修正碼(ECC),它是將冗餘記憶體位元與使用者數據一起儲存,以偵測和修正任何的記憶體錯誤或干擾。依照採用的ECC類型,特定數據字的單和雙位元錯誤能夠被修正,EDAC解決方案現已發展完備,設計人員能輕鬆地建置這項技巧。

要消除暫存器單元中的錯誤,會比SRAM複雜。因為SEE僅發生在局部位置,也就是說衝擊離子只會影響到單個p-n接面,因此可利用平行電路來修正暫存器SEU。此技巧最常見的建置方式,是採用一種稱為三重模組冗餘(Triple-module Redundancy, TMR)的冗餘形式。在TMR中,將三個暫存器(或正反器)平行配置,並將結果饋送至多數決(Majority-voting)電路,若一個正反器發生SEU,另外兩個還保有正確資料,多數決電路便會將正確資料傳送出去。

因為SET錯誤的暫態特性,因此修正方式更為複雜。根據電路設計和延遲容許程度的不同,有兩種技術可以採用。其中一種稱為三重驅動(Triple-drive),將閂鎖器(Latch)的輸出緩衝重複三次,如果其中一個緩衝發生SET,另外兩個便可抑制此事件並保持正確訊號。

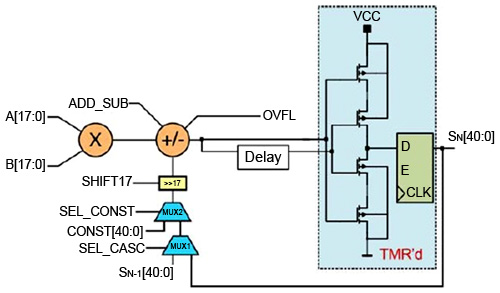

第二種SET緩解技巧,是採用具有安全閘(Guard Gate)的過濾器電路(圖1)。此過濾器首先將原始訊號路徑分開為兩個路徑,一個直接饋送至安全閘,另一個則是透過反相器串(Inverter String)在原始訊號中引進延遲。當兩個輸入相同時,安全閘的作用與AND閘一樣,或是當輸入訊號不同時,安全閘就做為先前狀態的閂鎖器,目的就是要以小於反相器串延遲的脈衝寬度過濾暫態錯誤。

|

| 圖1 採用安全閘的過濾器電路 |

RTAX-S加入DSP累加方塊 FPGA具備抗輻射能力

RTAX-DSP元件與RTAX-S/SL FPGA一樣,都是採用0.15微米互補式金屬氧化物半導體(CMOS)製程製造,具有相同的基本架構。這是美高森美(Microsemi)抗輻射現場可編程閘陣列(FPGA)產品的最新成員,在既有成功的RTAX-S架構中增加了嵌入式抗輻射乘法--數位訊號處理器累加方塊(DSP Mathblock)。除增加DSP功能性外,新產品還更改SEU保護正反器設計,相較於RTAX-S/SL可進一步強化FPGA架構的SEE效能。

RTAX-S R-Cell緩解與RTAX-DSP增強

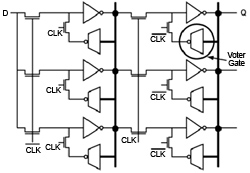

在FPGA核心中,RTAX架構有兩種邏輯模組,R-Cell和C-Cell。C-Cell能建置超過最多有五個輸入的四千個組合;R-Cell能以非同步清除、非同步預設、主動低使能控制訊號、再加上可程式時脈極性建置單個D類型正反器(Flip-flop)。

|

| 圖2 利用表決閘邏輯,以R-Cell建置D類正反器。 |

為強化R-Cell以對抗SEU,閂鎖器係以TMR建置。每個RTAX R-Cell是利用三個主從(Master-slave)閂鎖對建置,每對都有非同步自我修正回饋路徑。每個閂鎖器的輸出會與另兩個閂鎖器的輸出比對,如果三個閂鎖器中的一個受離子衝擊並準備更改狀態時,在與另兩個閂鎖器「表決」(Voting)後,便能預防此變更值會反饋並造成永久閂鎖(圖2)。不過,在布局設計時須特別小心,不能讓單一離子的衝擊會影響一個以上的閂鎖器。

雖然RTAX-S R-Cell已經過強化,可對抗SEU,但還是有可能會受到SET的影響。FPGA業者輻射團隊進行的重離子束測試顯示,RTAX-S/SL FPGA出現的大部分SET錯誤,實際上是因為離子衝擊R-Cell所致,此結果也已獲得航太公司輻射部門的確認。進一步分析發現,R-Cell的輸出緩衝器是主要因素。

為提升RTAX-DSP的抗輻射性能,FPGA廠商在R-Cell的輸出緩衝器端增加SET緩解設計。透過採用稱為三重驅動的解決方案,此輸出緩衝器會被重複三次,再將其輸出一起連接到單一輸出節點。若其中一個重複緩衝器出現SET,另外兩個將會抑制此暫態效應,並維持正確的訊號。因此,RTAX-DSP R-Cell將能充分發揮緩解SEE的性能。

DSP累加方塊以125MHz運作

嵌入式抗輻射DSP累加方塊為18位元×18位元的乘法累加方塊,有助於有效建置DSP建構方塊,例如有限脈衝響應(FIR)和無限脈衝響應(IIR)數位濾波器、快速傅立葉轉換(FFT)和反傅立葉轉換(IFT)、離散餘弦轉換(DCT),以及Reed-Solomon編碼演算法。每個DSP累加方塊都能以125MHz運作,每秒共執行一百五十億次乘法累加運算(15GMACS)。

DSP累加方塊的SET緩解設計為,將一個安全閘SET過濾器插入在乘法器輸出的每個位元和其輸出暫存器之間。為進一步強化過濾器的強韌性,每個安全閘也會被重複三次。

為了給安全閘電路選用適當的過濾強度(或延遲),業者開發特殊的RTAX4000D原型,並施以重離子束測試。此特殊原型與RTAX4000D的量產版本相同,但在SET過濾器中加入了不同數量的延遲。

RTAX4000D包含一個6×5的核心陣列,因此可產生五列的二十四個DSP累加方塊。SET過濾器延遲數量在每一列都不相同,依序為第一列0ps、第二列250ps、第三列500ps、第四列750ps、第五列1,000ps重離子束測試顯示,大部分SET的脈衝寬度介於250750ps間,而750ps過濾在SEE剖面(Cross-section)呈現出顯著的改善。因此,選用750ps的延遲量作為RTAX-DSP的量產版本。

SEE特徵化結果

為量化RTAX-DSP R-Cell的解緩改善有效性,在Lawrence Berkeley國家實驗室中進行全面性的重離子束測試,並採用先前RTAX-S測試設置的更新版本。此測試設置主要包含三個部分,一塊主機板,其中包含一顆負責In-beam監控和控制待測物(DUT)的「主」FPGA;一塊安裝DUT的RTAX-DSP子板;一塊介面板,其中包含一顆可透過兩個通用序列匯流排(USB)埠在中控個人電腦(PC)和主機板間進行通訊的「從」FPGA,DUT上的輸入/輸出(I/O)高數值能用來建構多個平行式的無干擾測試架構,能實現更完整的特徵化作業。此外,這個方法能確保每個測試架構都能在相同條件下進行測試。針對RTAX-DSP SEE的特徵化作業,設計的重點主要在元件的兩個區域:FPGA核心與DSP累加方塊。

RTAX-DSP FPGA核心特徵化

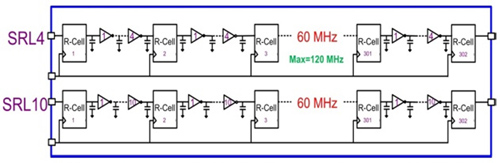

FPGA核心的SEE特徵化作業採用在R-Cell間插入C-Cell串的測試架構(圖3)。第一個架構(SLR4)包含三百零二個R-Cell的移位暫存器,每階之間都有一個由四個C-Cell組成的串(被配置為反相器),所有元件都由單一時脈驅動。第二個架構(SLR 10)同樣也是移位暫存器,但每階之間有十個C-Cell反相器。這些架構的基本形式與RTAX-S特徵化作業中所採用的相同,因此能直接比較RTAX-S DSP R-Cell中增強緩解電路的有效性。

|

| 圖3 RTAX-DSP FPGA核心的測試示意圖 |

這些架構可顯示出SEE剖面對時脈頻率和兩個R-Cell間插入C-Cell數量的相依程度。雖然SLR4的最高頻率為120MHz;SLR 10為60MHz,兩個架構都是以15和30MHz進行測試。

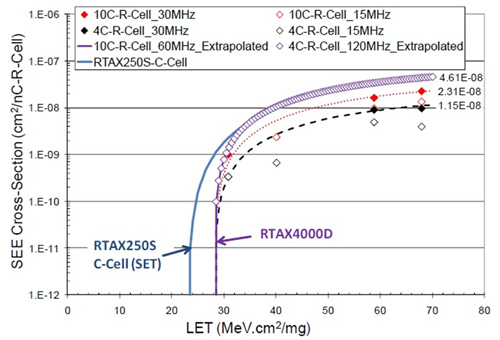

在測試期間,以15和30MHz執行時,兩個架構都出現幾次干擾現象。在30MHz下,這些架構的SEE剖面是15MHz數值的兩倍。此時脈頻率的線性相依性意味著,大部分的錯誤是由SET事件所造成。同時,在相同頻率(15或30MHz),數據顯示10C-R-Cell的SEE剖面是4C-R-Cell的兩倍,更是代表說,此增加是因為測試中C-Cell數量的作用。

圖4所示為,以15和30MHz頻率測試,以及線性外插至最大頻率的結果。此圖也顯示了單一RTAX-S C-Cell的結果,以供比較之用。兩個最差狀況的SEE剖面結果一致,但並沒有超過RTAX-S的C-Cell SET剖面(4.61×10-8cm2/nC-R-Cells)。此外,在所有頻率下,RTAX-DSP中建置的nC-R-Cell的剖面都比RTAX-S低了許多。此數據也顯示出,閾值LET(LETth)已改善到28MeV cm2/mg。此改善應該是由於RTAX-DSP中增加的繞線電容作為過濾器的效果。

|

| 圖4 RTAX4000D nC-R-Cell的SEE剖面 |

圖4也清楚顯示,RTAX-DSP R-Cell對SEE剖面最多有一小部分的貢獻,證明三重驅動緩解技巧的有效性。在RTAX2000S和RTAX4000D中建置nC-R-Cell,所產生的Weibull參數和預測性對地同步(Geosynchronous)衛星錯誤率,均列在表1中。數據顯示,RTAX-DSP與RTAX-S相比,nC-R-Cell的軌道錯誤率幾乎減少了一個數量級。

DSP累加方塊SEE特徵化

DSP累加方塊的複雜特性需要更縝密的測試方法。首先,三種累加方塊配置中的每一種都須進行測試;其次,須採用開銷(Overhead)較少的方法論。針對DSP累加方塊的三種配置,有兩種是以平行方式運作,其中一個是作為黃金(Golden)參考標準,而另一個則是DUT。所有三種配置都被編程在單一元件,以進行同步測試。因為兩個DSP累加方塊放置的距離很遠(超過10μm),因此兩個方塊在單一時脈週期中(120MHz為8.5ns)同時發生干擾的可能性非常低。

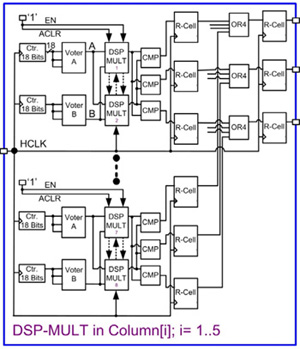

DSP累加方塊以乘法器模式執行測試

|

| 圖5 以乘法器模式測試DSP累加方塊測試示意圖 |

為了要以乘法器模式測試DSP累加方塊(圖5),黃金和DUT方塊的A和B輸入是由相同的計數器和單一外部時脈所驅動。兩個方塊的輸出會在每個時脈週期進行比較。

為達到可靠的錯誤偵測,比較電路(XOR閘、R-Cell等)會重複三次,然後,相同的子電路(兩個方塊組和它們關連的比較電路)會在單列中垂直重複四次。四個錯誤旗號的三重邏輯總和會被傳送到主FPGA,若三個輸出暫存器從0變為1時,此FPGA便會發出錯誤訊號。

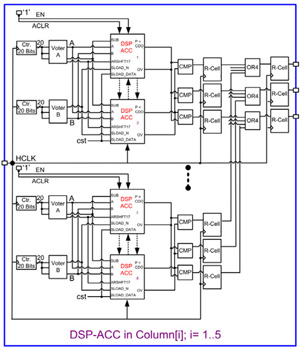

DSP累加方塊以累加器模式執行測試

DSP累加方塊累加器模式的測試設置與乘法器類似。計數器輸出在方塊輸入(A和B)以及其他控制訊號(SUB、SLOAD_N、和ARSHFT17)間週期循環。

SLOAD_N的啟動能讓兩個方塊隨時重新同步作業。同時,兩個區塊的輸出會在每個時脈週期進行比較。

|

| 圖6 DSP-ACC的測試示意圖 |

與DSP累加方塊作為乘法器的測試配置類似,子電路的測試會在單列中垂直重複四次,四個錯誤旗號的三重邏輯總和會被傳送到主FPGA(圖6)。

為初始化累加器(載入模式),SLOAD_N訊號必須啟動,才能讓資料(SLOAD_DATA)被下載到區塊的輸出暫存器。在測試中,SLOAD_DATA是被設定為由0或1邏輯狀態組成的常數值。

當SLOAD_N失效後,每個區塊會回饋結果資料,然後以累加器模式執行。SUB和ARSHIFT17訊號會被用來在減法、加法或載入/累加資料移位之間作選擇,若在執行累加模式時發生SEE,此事件會被鎖定,只有切換SLOAD_N或ACLR訊號才能清除這個錯誤,一旦區塊切換到載入模式,錯誤計數器就會停止增加。

將DSP累加方塊作為累加器進行測試時,會產生兩種錯誤型態,第一種為當以載入模式執行時,會出現單一錯誤;第二種是在累加器模式期間,由於鎖定錯誤,因而出現許多錯誤。

由於這兩種模式間的切換是透過計數器,由切換SLOAD_N自動進行,不須手動重置或在偵測到多重錯誤時才切換模式。

這樣的安排可加速測試,並將第二類型錯誤的剖面低於預估情況降至最低,同時也能在兩種錯誤間建立清楚的區別。

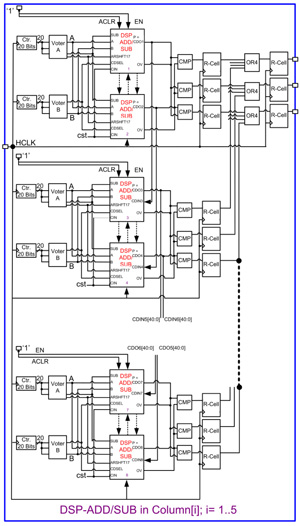

DSP累加方塊以加法/減法器模式執行測試

|

| 圖7 DSP累加方塊作為加法器/減法器的測試示意圖 |

在此配置中(圖7),四個DSP累加方塊被鏈接在一起,將輸出(CDO)饋送給比較器和鏈結中下一個區塊的CDIN。這兩個鏈會相互交錯,所以每階都有一對區塊,與其他配置相同,其中一個是黃金和一個是DUT。

在加法器/減法器模式中,當CDSEL啟動時,區塊以CIN值進行初始化,若CDSEL失效,DSP輸出暫存器會被饋入鏈中前一個DSP區塊的CDIN。第一個DSP區塊的CDIN是由Libero整合式設計環境(IDE)設計軟體自動設為「0」邏輯狀態。

每對DSP區塊的輸出會跟溢出訊號比較,同樣地,錯誤旗號的總和也會被傳送到主FPGA。在此情況下,只有當SEE出現在鏈中的第一、第二,或第三個DSP才會有多重錯誤產生。

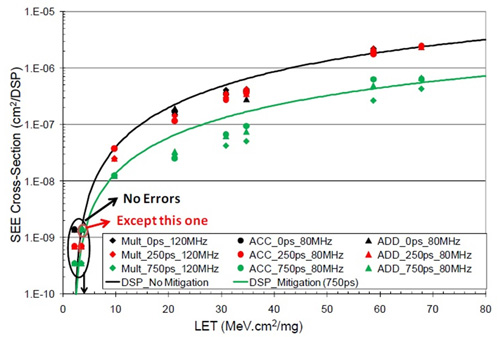

緩解設計可顯著改善SEE

為評估SET過濾的有效性,針對三種不同DSP累加方塊配置的無緩解和緩解版均進行測試。三種配置都顯示,SET靈敏度會明顯與頻率相關(圖8)。事實上,SEE剖面幾乎是與頻率呈線性增加的趨勢。在相同頻率下,三種配置的剖面都非常類似,只是累加器或加法/減法器模式高於乘法器模式。加法/減法器和乘法器之間的剖面差異,最有可能是因為回饋路徑中增加的組合邏輯所造成。另一方面,加法/減法器和累加器模式間的相似性,有可能是因為兩種模式都具相同數量的敏感節點。這些數據清楚顯示,相較於無緩解版本,緩解設計顯著改善SEE剖面。表2列出兩種版本的預估GEO軌道錯誤率。

|

| 圖8 緩解與無緩解DSP累加方塊SEE剖面比較 |

RTAX-DSP FPGA是目前抗輻射FPGA黃金標準RTAX-S/SL FPGA的最新變異版本。FPGA業者最新抗輻射FPGA在既有成功的RTAX-S架構中增加嵌入式抗輻射乘法--DSP累加方塊,這是業界首創在FPGA中加入輻射強化DSP方塊的設計。

除加入DSP功能性之外,新FPGA元件還採用增強的硬化正反器,相較於RTAX-S/SL可提供進一步的單一事件效應保護。在RTAX系列產品中增加這兩項新特性,可帶來高密度、高效能的抗輻射解決方案,並具有非常低的軌道錯誤率。

(本文作者任職於美高森美)