任何能在射頻範圍內產生訊號頻率的元件,都可能是電磁干擾(EMI)的潛在來源。這些訊號會造成干擾,讓無線電、電視、手機以及其他設備無法正常運作。就大多數系統而言,電磁干擾的主要來源是時脈產生以及分布電路。

造成干擾的電磁波,是由帶電荷粒子在電場中移動所造成。每當存在電子訊號時,就會發生這種情況。各地主管機關要求會產生電磁干擾的裝置必須遵循相關的規範與條例限制。這些規範要求輻射來源在固定的頻率範圍內,於規定的距離下,強度不得超過規定的上限值。

了解電磁干擾成因 有效提升訊號效益

時脈來源會透過兩種途徑來產生電磁干擾:同步時脈的重複特性,以及沒有做好設定的終端電路。時脈輻射出的能量會透過天線形成一個電場。天線的形態可能是印刷電路板(PCB)電路、PCB重工線路、遮蔽不足的元件、連結器、纜線(遮蔽或無遮蔽)或接地不良的設備。

在高速數位元件方面,固定頻率時脈是電磁干擾的主要來源,因為它們總是在一個固定的頻率下運作,讓能量增加至更高的水準。非重複性或非同步的訊號,則不會產生這麼多的電磁干擾。

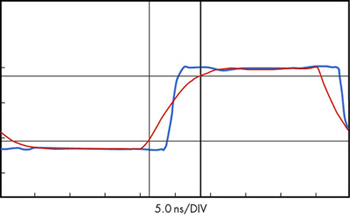

由於更高流量的需求帶動更快的時脈頻率,訊號傳輸率亦須提高。但更快的上升與下落時間,亦讓輻射訊號的能量向上提高。圖1顯示兩個頻率、振輻、占空係數以及相位都相同的訊號,但兩個訊號的傳輸率不同。上升時間較快的時脈,其輻射能量明顯超過傳輸較慢的訊號。

|

| 圖1 兩個頻率、振幅、占空係數及相位都相同的訊號,但其訊號傳輸率不同。 |

導致電磁干擾的第二種因素,是未做好設定的終端電路。當出現阻抗不匹配的狀況時,就會有過擊或下衝的電路。發生這種情況時,輻射的能量就會增加。根據過擊與下衝的嚴重程度,在特定訊號或電磁干擾的節點上會出現3~4dB強度的電磁干擾。電路會有均方根值。若有十至二十個節點出現嚴重的過擊情況,就難以通過美國聯邦通訊委員會(FCC)的相容測試。

降低電磁干擾 方法多元助益大

有許多方法可解決數位系統中的電磁干擾問題。研發業者可選擇採用遮蔽、訊號濾波或從源頭處移除能量。這些方法可單獨運用或混合併用。

不過,遮蔽並不是一種電子解決方案,而是一種機械式的建置方法。遮蔽是採用含金屬的外層,藉以阻絕電磁干擾。這種方法以往經常被使用,但有時它也是一個成本昂貴的解決方案。在產品上市不久後發現電磁干擾問題時,遮蔽並不是一種簡單的補救辦法。

其他方法包括濾波、移除能量以及隔離會產生電磁干擾訊號的電路。想要找出哪個(或哪些)電路是問題的根源,應在無回聲反應室進行測試,或執行EMI模擬。透過這類測試,根據放射報告就能找出哪些頻率超過特定的上限。這些頻率通常稱為「熱點」。得知頻率(包括諧波)後,就能找出時脈電路。

由於沒有做好設定的終端訊號可能產生熱點,因此第一種解決方法是確保所有訊號都做好終端設定。產生電磁干擾的訊號應加以模擬,並分析電路的過擊與下衝。若出現超出正常的狀況,則應調整終端值來產生更好的波形。

若所有訊號都做好終端設定,過擊的程度也很輕微甚至完全沒有,接著就可檢驗時脈的傳輸率。替換一個較慢的緩衝器,可能會解決問題。許多時脈緩衝器可選擇高速或低速輸出。這些元件通常具有接腳相容的可更換性,或元件可設定迴轉率。若系統可接受較慢的驅動,這會是最佳的解決方案。這種方法直接解決造成問題的時脈電路,且通常不須付出額外的成本。

若沒有較慢的元件,常用的方法是濾波,藉以放慢訊號的邊緣速度。這通常涉及到一個電容器加入至訊號中,根據電容時間常數(RC)固定的時間來減緩邊緣速度。電容值通常介於5~15皮法(pF)。採用這些電容器的研發業者,通常須要將其置放在靠近訊號來源處,除非發現電磁干擾的問題,否則不須在其他處增加擺放電容器。若時脈電路採用串列式終端,電容器可置於電阻的任何一端,藉以降低電磁干擾。然而,為達到最佳的終端效果與訊號完整性,電容器必須被置放在驅動器與電阻器之間。

雖然這種方法能降低電磁干擾,但它會降低時脈的訊號完整性,且其波形不適合高速時脈的銳利邊緣,而是變成較為圓滑。此外,必須針對設計中的每個時脈來擴增電容器。

時脈調變具高效率/低成本優勢 成抑制EMI首選解決方案

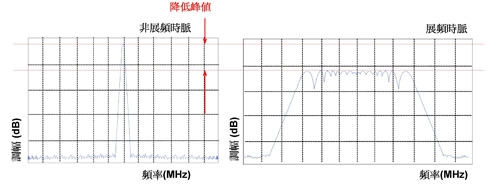

要解決訊號放出過多輻射問題,另一種方法就是時脈調變。時脈調變亦稱為展頻,並已運用多年。展頻時脈(SSC)則是一種高效率、有效且低成本的替代方案,可有效抑制電磁干擾。SSC能降低電磁干擾的峰值,將一個時脈的能量散布至較廣的頻帶。圖2顯示當頻帶拉大時,能源波峰就隨之降低。

|

| 圖2 當頻帶拉大時,能源波峰就隨之降低 |

透過這項技巧,可把峰值降低5~18dB。建置時僅須增加少數元件,甚至完全不必增加,且時脈訊號被扇出並傳輸至目的地,就能維持能量散布的優勢。

以時脈頻率與時間為兩座標軸描繪成圖後可看出調變訊號的波形:最大頻率偏移Δf,是上方與下方極限的差值。這通常指的是主頻率的比率,並經常被稱為展頻量(Spread Amount)。展頻值通常介於0.25~4%之間。這個變數通常會被微調,以便把電磁干擾控制在規格範圍內。

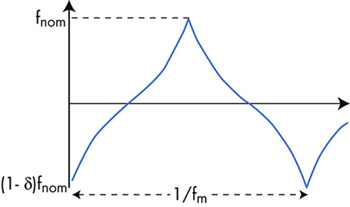

調變的設定波形相當重要,因為它決定了dB最大降低幅度。雖然一個三角型的波形輪廓很容易建置,而且能產生良好的結果,但Lexmark波形輪廓(圖3)經過最佳化後,能產生較平坦的頻率波形(圖2),且讓高峰值降得更低。大多數SSC元件都採用一種波形輪廓或是另一種,有些元件則可選擇或設定波形輪廓。

|

| 圖3 Lexmark波形輪廓 |

慎選調變率可將電磁干擾降至最低

調變訊號的最後一項變數是頻率。標準調變頻率約為30kHz。一般較傾向採用低調變頻率,因為它能把許多展頻時脈在下流元件上可能有的負面效應降到最低。若調變頻率過低,音效干擾就會成為一項風險。因此建議選擇30kHz這段沒有音響頻帶的頻率。當然偶而會看到100kHz或更高的調變頻率,但通常一些特定應用可與這些調變頻率相容。大多數SSC元件都是在一個固定的調變頻率中運作。

電磁干擾降低的幅度,不僅取決於展頻量,也取決於時脈頻率。例如,在100MHz時脈上進行1%的展頻,意謂波峰間頻率偏移為1MHz。相較之下,在20MHz時脈上1%幅度的展頻,則只有200kHz。因此,雖然兩款的展頻率相同,但實際展頻的幅度卻不一致,因此電磁干擾波峰降低的幅度也不相同。較低頻率的時脈需要更大的展頻比例,才能達到和較高頻率時脈相同的電磁干擾降低幅度。

這種頻率的關係適用於諧波以及主頻率上。正如諧波頻率是主頻率的整數倍,展頻的頻率寬度也是類似的整數倍。回到展頻1%的100MHz時脈,第三諧波的頻率是300MHz,展頻為3MHz--是100MHz時脈展頻的三倍。由於諧波展頻的頻率增加,電磁干擾降低的幅度也超過主頻率。

另一項有趣的觀察重點,是尖峰電磁干擾降低幅度與展頻量之間,呈現非線性的關係。在小幅展頻比時,達到最理想的降低幅度,因為增加展頻比率時,產生的效應會逐漸減少。基於這個因素,只有少數應用會使用超過5%的展頻比率。

電磁干擾抑制法具低成本效益

運用具備電磁干擾抑制功能的時脈晶片,可讓系統輻射的電磁干擾降低10dB以上。這種方法能大幅降低系統的成本,幅度從不到1美元一直到5~10美元。降低電磁干擾的傳統技巧包括有遮蔽的接地面、濾波元件及遮蔽等。從雙層板到四層板,並在其中插入額外的接地面,成本為5~6美元。濾除電磁干擾,通常須用到約0.25美元的暫存器、電感和電容,以及花0.70美元的成本來加裝扼流圈與磁心線圈等元件。在許多狀況下,濾波尚不足以讓系統通過電磁干擾測試,此時就需要昂貴的遮蔽元件。遮蔽可輕易讓系統成本增加數美元。

整合資源供應 大幅克服EMI難題

在整合SSC至設計時,工程師會發現市面上有許多SSC元件可以利用。時脈產生器會從晶體產生一個特定的頻率。有些能在多個不相關的頻率上產生一組展頻時脈以及非展頻時脈。市面上也有單一頻率、完全整合的展頻振盪器(SSXO)。其他低接腳數元件可置放在正常時脈訊號上,藉以擴增展頻。

許多SSC元件允許自行開啟或關閉展頻功能,有些元件可透過選擇接腳來調整展頻量。可編程展頻時脈產生器提供彈性,讓使用者設定輸出頻率及實際的展頻量。可編程程度最高的元件,連輸出強度也能設定。若在設計週期結尾的電磁干擾測試,研判需要變更展頻參數,現場可編程元件就能用來以新的設定值對元件進行快速編程。透過這種方法,在系統設計階段為SSC供應適合資源,工程師可確保有完備的資源來控制時脈產生的電磁干擾,並且在設計週期尾聲有足夠的時間來微調電磁干擾。

(本文作者為賽普拉斯產品行銷經理)