在矽穿孔技術的加持下,立體堆疊封裝技術的發展也一日千里,朝向更高度整合、更小尺寸與更佳效能的方向演進。近期此類立體堆疊技術也已陸續獲得數家國際大廠之支持,聲勢頗為浩大。但眾業者也認同,相關技術之發展仍需一段時間才能真正成熟並邁向普及。

受到2009年景氣的波及,不少半導體廠商莫不縮衣節食,產能利用率一落千丈者有之、關廠裁員者有之,更有遭購併或重整,自此消聲匿跡者。

不過,儘管2009年半導體產業活動力大減,卻有多家業者將重心放在下一代立體堆疊封裝技術三維晶片(3D IC)上,甚至將其視為顛覆半導體產業既有規則之明日之星,期望3D IC的問世能為沉寂多時的半導體產業注入活水。

立體堆疊技術誘人國際大廠伸臂擁抱

3D IC與現有其他立體堆疊技術的不同之處在於,相較於其他立體堆疊技術(表1)透過外部打線(Wire)進行訊號傳遞,3D IC乃透過矽穿孔(TSV)協助3D IC之成型。

表1 各式立體堆疊技術之比較

資料來源:高通

根據工研院的定義,TSV是在晶圓上以蝕刻或雷射的方式鑽孔(Via),再將導電材料如銅、多晶矽、鎢等填入穿孔,以形成導電的通道(即內部接合線路),最後則將晶圓或晶粒薄化再加以堆疊、接合(Bonding),而成為3D IC。

工研院指出,由於採用TSV的構裝內部接合距離即為薄化後之晶圓或晶粒的厚度,相較於採打線接合(Wire Bonding)的傳統堆疊封裝,或過去強調效能優勢的系統單晶片(SoC)設計,3D IC的內部連接路徑更短,相對可使晶片間的傳輸速度更快、雜訊更小、效能更佳,尤其在中央處理器(CPU)與快取記憶體,以及快閃(Flash)記憶體間資料的傳輸上,更能突顯TSV的短距離內部接合路徑所帶來的效能優勢。此外,3D IC的構裝尺寸等同於晶粒尺寸,在強調多功能、小尺寸的可攜式電子產品領域,3D IC的小型化特性更是市場導入的首要因素。

也因為今日之可攜式裝置均朝輕薄短小之方向邁進,3D IC之發展也大受歡迎,高通(Qualcomm)CDMA事業群資深副總裁暨總經理James A. Clifford便指出,為有助開發可應用於可攜式裝置之晶片,該公司已投入於3D IC之發展,並期望3D IC之演進能帶來上述效益。

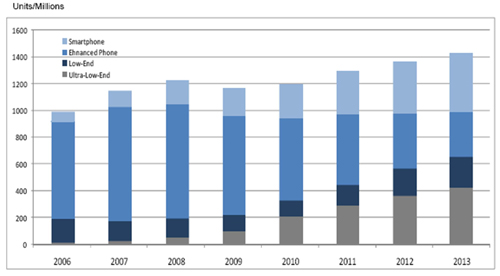

Clifford指出,從2004年90奈米(nm)問世以降,每閘極(Gate)之成本便以每年減少29%之比例下降,並成為推動成本降低與技術演進之動力。而尤其在手機市場的變化(圖1)下,可攜式裝置對尺寸之要求更加嚴苛,也迫使半導體廠商必須朝向晶片立體化的方向演進。

|

| 圖1 2006~2013年全球手機發展 |

資料來源:ABI

除了高通之外,其他半導體廠商也對此一領域興致勃勃。如英特爾(Intel)與IBM皆明白指出,在現有製程微縮極限12奈米現身後,半導體廠商勢必需要更先進之技術,才能突破現有技術門檻,同時在成本、效能上有所改善。

另外,為在記憶體領域有所改善,爾必達(Elipda)與三星(Samsung)之矽穿孔3D IC動態記憶體產品便已初試水溫,有意透過立體堆疊技術提升記憶體產品之效能,進而增加產品競爭力。

鑽孔先後/晶圓薄化/散熱管理難度高

雖然3D IC具有上述多項優勢,並且已受到大規模的討論,但業界也不諱言,該技術要成熟,須要突破鑽孔先後、晶圓薄化與散熱管理之挑戰。

鑽孔先後影響後續作業

|

| 圖2 愛美科事業發展經理李宗正認為,鑽孔之先後順序可能大幅影響後續晶圓之設計,不可不慎。 |

從鑽孔先後之差別來看,愛美科(IMEC)事業發展經理李宗正(圖2)指出,鑽孔之先後由於可能影響後續作業之複雜度、耗費時間以及投資成本,因此也各有一定考量。舉例來說,先鑽孔(Via First)技術便是先在晶圓上開挖穿孔,稍後再進行其他製程步驟。不過由於後續製程手續繁雜,因此較不被業界所看好。

後鑽孔(Via Last)則因在製程上可與晶片設計分開,因此對無晶圓(Fabless)業者與封裝業者來說則有較大發揮空間。其他尚有介於兩者之間的Via Middle等方式。

晶圓薄化與材料息息相關

至於在晶圓薄化領域,由於晶片堆疊之數量將由2007年的三至七顆晶片,演進至2015年的五至十四顆晶片,且後者之封裝仍須符合厚度小於1.0毫米的要求,因此可以想見晶圓薄化的考驗也將愈大。

於此延伸的議題是,由於晶圓厚度的變化將導致強度不足,甚至可能造成晶圓的損毀,因此也引起一波在晶圓上進行特殊承載材料(Carrier)之風潮。

散熱管理不可小覷

|

| 圖3 創意電子系統級封裝計畫總監林崇銘表示,晶片堆疊程度愈高,熱度管理之議題也更加艱困。 |

另一項同樣極為重要的挑戰則是散熱管理。隨著元件的整合密度愈高,其產生之熱度也就愈高,如何進行熱度管理便是另一難題。創意電子系統級封裝(SiP)計畫總監林崇銘(圖3)透露,不論是下一代的3D IC、已問世之SiP與整合度更高之系統單晶片(SoC),晶片堆疊所產生之熱度無疑是最大難題。他指出,在SiP領域已面臨散熱、功率管理、封裝方式與印刷電路板(PCB)等考驗,而隨著3D IC的整合程度進一步提升,相關挑戰自然只增不減。

林崇銘不諱言,欠缺適合之設計與分析工具是目前業界所面臨的最大難題。尤其因為設計工具的缺乏,工程人員必須人工計算來完成散熱管理,不但曠日廢時,也可能造成錯誤。目前的模擬軟體乃針對量產材料所設計,並不適用於具備精細結構的多層超薄材料。軟體工具必須能支援薄型材料、進行黏性分析與失效分析,以及預測生命週期,以改善設計並最佳化組裝結果,方能進而加快產品上市時程。

實際效益待商榷 3D IC演進牛步

正因為3D IC還有前述的多項挑戰須要跨越,近期的發展腳步並不快速。不少業者認為,此類封裝方式僅為工具,並非目標,因此不打算在其中多加著墨。其次,也有業者對3D IC於成本及效能上的回收有所疑慮,需要更多佐證才願意投入。

Tessera台灣區總經理暨東亞區總監魏煒圻即指出,隨著各式半導體元件被應用於越來越多元的產品,而成本的障礙、尺寸的微縮與可靠度的提升,也都會是吸引客戶採用的關鍵。相較於過去大為強調單晶片之效能表現,今日3D IC由於使用薄型晶片、較小的內連線與較多的材料與處理流程,要如何維持可靠度,也將是另一挑戰。

無論如何,TSV的問世確實為晶片立體堆疊技術打開了全新的一扇窗。各界若能持續針對此領域加以著墨,也將有助3D IC的加速實現。