如何將測試系統對高速串列介面訊號的影響降低到最小,並且無失真的採集待測訊號,對新的設計方案的評估、測量非常重要。整個測試過程可分為五個重要的部分:連線性、測試碼型產生、接收端測試、訊號採集與訊號分析。

使用正確探頭避免訊號損壞

測量路徑中,包括待測物(DUT)到示波器通道的訊號路徑,同樣存在著傳輸線效應,將導致訊號的損傷以致測試失敗,因此,使用正確的探頭進行正確的連接是非常重要的。高速串列匯流排標準的機械結構,有時稱為物理媒介相關(PMD)規範,決定如何連接DUT。對於不同的標準,有著不同的連接方式,每一種都有獨特的特性。

有五種方式滿足各種訊號探測的需求,第一種方式是最新的三模(TriMode)差分探頭,該探頭能透過一次連接,實現差分、單端和共模訊號的測試。第二種方式為用單端探頭進行「偽差分」探測,可完成差分、單端和共模訊號的測試。第三種方式是適用於測試夾具和示波器連接的SMA(SubMiniature version A)偽差分探測。第四種方式是用差分探頭直接測量差分訊號。第五種方式則是以SMA真差分探頭連接示波器和測試夾具。

必須注意的是,上述五種方式,探頭皆會對DUT施加一定的負載。不同的探頭都有不同的電路模型,輸入阻抗會隨著頻率的升高而變化,會影響被測電路的行為和測量的結果。

| ‧ |

|

| |

|

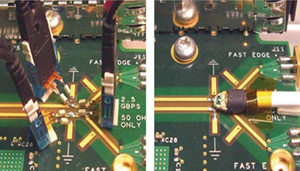

| 圖1 Tri-Mode(右)簡化傳統探測方式(左) |

不同於傳統的差分探頭,TriMode差分探頭可用一個探頭,僅須和被測電路連接一次,即可實現單端、差分和共模訊號的測量。以往對共模訊號的測試,需要兩個單端探頭分別探測差分訊號正端和負端,然後在通過兩個通道做加法運算得到共模訊號(圖1左)。新型的TriMode探頭能僅以一個探頭完成共模訊號的測試(圖1右)。 |

| ‧ |

|

| |

|

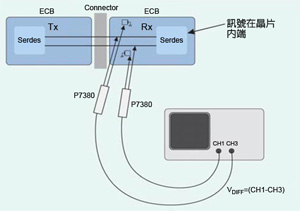

| 圖2 在接收端晶片處進行偽差分探測 |

通常使用探頭在電路板上進行電路故障定位,需要探頭能靈活方便的在不同的走線、接腳上探測電壓訊號。兩個有源單端探頭可分別探測差分訊號的兩端,進行偽差分的測量和共模訊號的測量,如圖2所示,兩個探頭分別連接在示波器的兩個通道上,透過示波器上的數學運算得到差分或共模訊號,由於要使用示波器的兩個通道,因此在測量前,通道之間的時間偏差(Skew)校準非常重要。 |

| ‧ |

|

| |

|

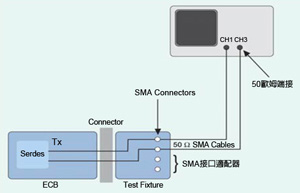

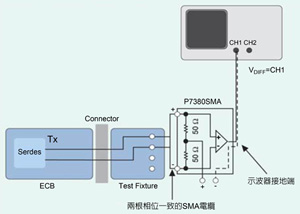

| 圖3 使用SMA電纜連線夾具連結待測物和示波器 |

許多的一致性測試夾具和原型電路都是透過高頻的SMA連接器輸出待測訊號,在這種環境下,用SMA同軸電纜連接訊號進行偽差分測試是可行的。訊號的發送端直接將訊號輸出到示波器,示波器每個採集通道內部採用50歐姆負載端接,另外,可通過SMA介面適配器直接將訊號連接在示波器通道上。

正如前面所描述,偽差分測試須使用示波器兩個通道,通道間的時間偏置校準非常重要。圖3說明使用SMA進行偽差分測試的情況。

|

| ‧ |

|

| |

|

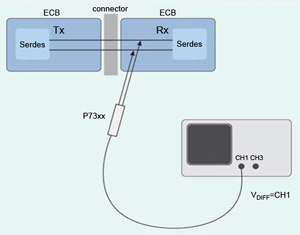

| 圖4 在接收端使用差分探頭探測訊號圖 |

真正的差分探頭具有低損耗、良好訊號保真度。圖4描述在接收端晶片處使用差分探頭測試的例子。

真正的差分測試不像偽差分測試,僅需要一個示波器通道,毋須對波形使用數學運算,這樣測試工程師可更好的利用示波器多通道、高取樣速率的優勢,同時測試更多的差分訊號,有利於高速串列訊號多通道測試。

|

| ‧ |

|

| |

|

| 圖5 使用SMA差分探頭連接在夾具上進行訊號探測 |

對於一致性測試點定義在連接器或夾具端面的串列標準而言,探頭輸入端是SMA介面差分探頭是最理想的訊號探測方法。探頭的兩個SMA輸入端提供100歐姆的差分端接,並且提供用戶可調節的端接電壓,端接電壓可根據不同的訊號類型而選擇。如果訊號發送端驅動100歐姆的負載,共模的連接器可開路。圖5所示為在連接器端或夾具端使用真差分SMA探頭的情況。 |

| ‧ |

|

| |

測試夾具對訊號的影響會隨著訊號速率上升而變大,因此對高速串列系統進行一致性測試必須使用經過認證的合格夾具。對於3Gbit/s的SATA 2.0訊號而言,很多夾具的影響可忽略不計,然而對於速率更快的PCI Express(PCIe)和高畫質多媒體介面(HDMI),夾具的影響將非常的大,測試工程師須重新設計現有的夾具系統。

對於某些應用,低成本的FR4板材已不再適用於第二代和第三代串列匯流排的設計,因為FR4在高頻情況下表現更多的損耗、反射和延時,進而不得不採用更昂貴更好的介質材料。

|

依規範定義產生測試碼型

每一種串列標準都指定作用在DUT一致性測試中的「黃金」測試碼型。這些指定的碼型是全面測試DUT以達到預期效果的關鍵。

例如PCI Express訊號發送端和接收端產生自有的測試碼型,而其他的標準採用更複雜的訊號處理方式。如果須要外部產生測試碼型訊號,測試儀器必須按照規範定義,產生頻率、幅度等完全一致的測試訊號激勵DUT。可程式設計訊號源包括定時資料發生器提供標準的測試訊號,例如TS1和TS2訓練訊號或偽隨機碼流(PRBS);任意波形產生器(AWG)提供任意的資料碼型及真實環境中的各種干擾,如雜訊、抖動、延時等;抖動產生源用以改變測試碼型資料的抖動,以進行壓力測試。儀器業者全新的多合一的訊號產生器簡化類比波形、資料碼型產生,可讓工程師更加方便的調節訊號源調製方案。

通過測試儀器間的互聯,如示波器、邏輯分析儀和主控機等實現自動的測試,可更加準確的完成一致性測試。AWG可透過MATLAB可自訂的波形資料,以及對示波器所捕獲資料的重播功能,可以加速測試的進程。

接收端靈敏度測試可確保相容性

雖然接收端位於各種各樣傳輸路徑的末端,但也必須滿足不同訊號發射端、不同傳輸路徑的相容性測試。為保證相容性,接收端晶片內部,特別是時脈數據恢復(CDR)和解串列部分,在特定惡劣的場合下須能正常的工作。CDR必須能對帶有抖動和雜訊的訊號進行時脈提取,同樣,解串列器必須按照規範要求容忍一定量的抖動、雜訊和通道間的時間延遲。

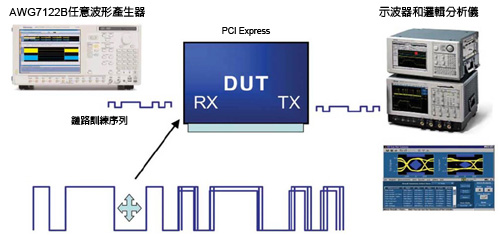

圖6描述單通道PCI Express接收端測試的量測儀器組成系統。根據不同的標準,具體的測試參數、過程和容限值都有所不同,基本的測試方法描述如下:

|

| 圖6 PCI Express接收端測試環境 |

首先設置DUT進入回送(Loopback)模式,並利用邏輯分析儀、示波器、串列匯流排協定分析儀或誤幀檢測儀監控資料發送端訊號是否與測試碼型一致。第二在資料流程中插入黃金測試碼型;第三改變幅度已確保接收端能準確的識別1和0;第四改變差分對的時間偏差用以檢驗能否容忍真實電路環境中的訊號延時;最後插入抖動確保CDR的鎖相迴路(PLL)能跟蹤輸入訊號。

觀察接收端晶片內部訊號

接收端測試和調試的難點在於無法直接用探頭探測到元件內部。許多接收端晶片內部有輸入濾波器用來補償傳輸鏈路的損耗和傳輸線效應,提供CDR更乾淨的訊號,因此,示波器探頭所看到的訊號是在濾波器前的訊號。

採用可程式設計數位訊號處理器(DSP)的示波器能以接收端晶片的角度,捕獲虛擬探測點的訊號。透過在示波器中應用有限脈衝響應(FIR)濾波器,示波器能顯示在輸入濾波器之前和之後的訊號,可提供工程師更加精確、影響CDR工作的抖動測試資料。

訊號進入接收端晶片時,不可避免的會有能量損失。幅度靈敏度測試就是用來檢查當訊號到達CDR和解串列器時,接收端能否準確的識別1和0。另一方面,時序測試通過改變差分對間時間偏差和上升沿快慢,用來驗證接收端容限,因此,資料碼型產生器或任意波形產生器須能提供差分的訊號輸出。

接收端抖動容限測量

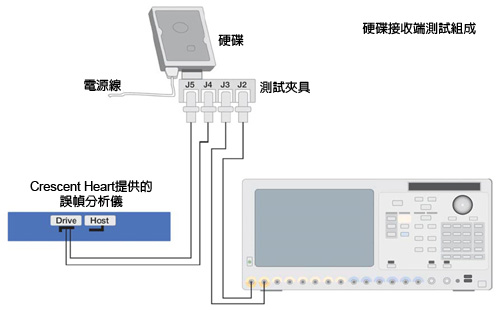

抖動容限測試目的是檢驗接收端能否正確的識別帶有抖動的訊號,若能滿足規範要求,則說明CDR能恢復出正確的時脈,並能準確的在使用者介面(UI)中間進行採樣。這也意味著即使訊號中有抖動,解串列器仍能正確的識別資料,圖7描述抖動容限測試的組成。

|

| 圖7 接收端抖動測試組成 |

對於嵌入式時脈、8b/10b的鏈路,例如PCI Express,嚴格的抖動容限測試非常重要。波形產生器必須具有提供生成特定幅度、頻率和調試方式,例如正弦波、方波三角波等抖動的能力。為能充分模擬DUT可能遇到的壓力,波形產生器必須能在上升沿和下降沿施加抖動。

目前,高速傳輸介面標準組織的各個工作組對在接收端測試中的碼間干擾(ISI)抖動干擾越來越感興趣。工程師和研究人員正在評估ISI對接受端的影響,以及測試和顯示碼間干擾抖動,例如DisplayPort和HDMI標準中,須使用電纜模擬器(Cable Emulator)模型用以類比最差情況的ISI。

使用示波器進行高速串列介面訊號採集

測量設備的特性可能會導致正常工作的DUT不滿足一致性要求。訊號採集系統包括探頭、電纜和示波器,須能讓足夠的訊號能量被採集。訊號採集系統關鍵因素包括頻寬、足夠的輸入通道、取樣速率與樣點記錄長度。

| ‧ |

|

| |

很多第一代的串列匯流排構架的速率在1.5G~3.125Gbit/s,最快的時脈頻率是1.56GHz,工程師可使用頻寬4G~5GHz的示波器進行測量,但訊號保真度測試和精確的眼圖分析要求示波器有更高的頻寬。

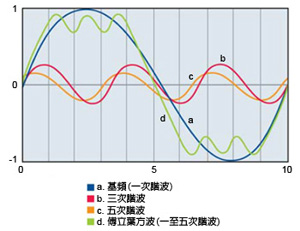

許多規範要求示波器在訊號發送端晶片接腳處精確的捕獲訊號基頻的五次諧波。以PCI Express 1.0為例,示波器頻寬須達6.25GHz,取樣速率至少是頻寬的兩倍。同樣,3.125Gbit/s的XAUI訊號要求示波器頻寬7.8GHz。許多的標準組織,特別是PCI-SIG,直接要求測試儀器的頻寬要滿足訊號五次諧波的原則。

隨著第二代串列匯流排發展,示波器頻寬需求也不斷增大。表1列舉當前和未來的串列匯流排一致性測試對示波器頻寬的需求。 |

| ‧ |

|

| |

|

| 圖8 各階諧波對合成方波的貢獻 |

示波器頻寬是影響眼圖測試的關鍵。對一個方波的傅立葉展開可發現訊號是由基波和各階諧波組成。如圖8所示,訊號的幅度特性的變化說明不同的諧波對訊號位準的貢獻。

頻寬不夠的示波器在採集訊號時會造成訊號五次諧波幅度的衰減,而五次諧波對眼高的測試時有增大的貢獻,因為資料判決就是在UI的50%位置進行。

|

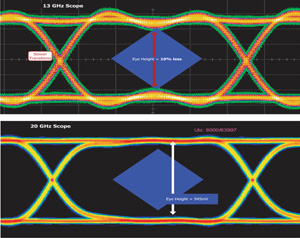

| 圖9 示波器頻寬對眼圖分析的影響 |

圖9描述頻寬對眼圖分析的重要性。用頻寬20GHz(圖9下)和13GHz(圖9上)的兩台示波器測量同一個6.25Gbit/s的訊號,可發現眼圖測試差異明顯,且會得到測試結果迥異的報告。

|

| ‧ |

|

| |

通常,標準對頻寬要求更多的是以訊號上升時間考慮。示波器和探頭的上升時間會影響到訊號上升時間的測量。公式1說明示波器、探頭上升時間和訊號真實上升時間以及測量結果間的數學關係,工程師須從測試結果中,除去探頭和示波器對訊號上升時間測試的影響。

...............公式1

例如測試系統20~80%的上升時間指標是65微微秒(ps),被測訊號的上升時間是75ps,測量結果顯示為99ps,這是不能忽略的測試誤差,因此,為更精確的測試訊號的上升時間,應該選用上升時間更快的示波器和探頭系統。

|

| ‧ |

|

| |

如HDMI此一高傳輸速率、低成本介質和多通道的串列匯流排,非常容易產生通道間的串擾及時間偏差。示波器可提供同時對訊號的即時採集能力,降低測試的複雜程度,提高驗證和調試的效率。

在多條通道上相關時間捕獲訊號,工程師能更容易理解故障產生的原因,同時記錄所有的串列訊號,不僅能完整的捕獲故障,而且還能發現故障對整個鏈路的影響。

|

| ‧ |

|

| |

除了示波器要有足夠的頻寬採集訊號,還必須能以夠高取樣速率記錄夠多的波形資訊以供工程師分析。每一個介面標準都指定了最小資料存儲數量,當然,記錄越長的波形,工程師就能分析越長時間間隔才出現的訊號異常。高性能的示波器具有高頻寬、更快的取樣速率及更長的記錄記憶體,都會為高速串列系統訊號分析帶來好處。奈奎斯特(Nyquist)採樣定律指出,要進行無混疊的採樣,取樣速率必須是類比訊號最高頻率分量的兩倍。隨著高速串列介面訊號速率超過20Gbit/s,取樣速率超過40GS/s的設備才能滿足測試需求。

具有大儲存深度的高階示波器,配合抖動分析軟體能揭示訊號中更多的細節,為設計提供可靠的保證。例如對於PCI Express 1.0標準,要求最少採集二百五十個UI進行一致性測試。高階示波器捕獲儲存一百萬個連續的UI,工程師可任意分析其中連續的二百五十個UI,提供更好的訊號品質評估。

對於多通道串列訊號採集,示波器必須對每個通道進行高取樣速率、長時間儲存,才能確保最多的訊號細節被採集。 |

選用正確的探測方式、正確的測試碼型及在訊號採集上採用性能優良的設備,這些都為最終的高速串列訊號分析提供保障。通常工程師都採用自動化測量和分析工具進行一致性測試,如安裝分析軟體的示波器可加速誤碼率評估、眼圖、反射和回波損耗等測試效率,並提供獨一無二的深入分析,幫助設計人員快速準確的定位串列系統的異常。

示波器採樣技術各有優劣

很多標準所定義的一致性測試都是基於即時採樣技術,而有另外一些標準卻需要等效取樣的設備,每一種採樣技術都有自己的優勢和使用背景。如即時採樣示波器(RT)通過觸發,並連續採集訊號,然後分析採集的資料樣點得到測量結果,採樣資料的細節資訊取決於示波器的頻寬、取樣速率和儲存長度。高階示波器使用軟體DSP技術進行CDR,這意味著可快速對不同的串列標準採用不同CDR模型。即時示波器能採集任何形式的訊號,且訊號可以是週期重複的,或者碼型是重複或單次出現的,都能被準確捕獲下來。

等效取樣示波器僅能重建週期重複的訊號波形。這種類型的示波器能夠採樣和重建的訊號頻率要比即時示波器高很多,但是被測訊號只能是週期重複的。採樣示波器依靠內部硬體CDR產生採樣脈衝,而示波器會根據每個採集脈衝隨機的採集訊號樣點,取樣示波器的測量、分析訊號的時間都比較長,因為要採集若干個訊號的重複週期。但是可以利用高階觸發系統,縮短觸發準備時間,加快測量速度。

現代高階取樣示波器還整合時域反射器(TDR)和時域傳輸器(TDT)的能力,可提供基於S參數的電路分析和建模,加上高階訊號處理功能,示波器能夠解釋更準確的訊號特性,並提供更深入的訊號分析。

| ‧ |

|

| |

每一個高速串列介面標準都定義如何捕獲資料進行眼圖測量,包括如何進行CDR,用範本決定訊號是否滿足一致性要求。另外,示波器軟體能夠進行統計分析決定範本邊界是否違規及其他重要的參數。

早期的標準中,覆蓋訊號五次諧波的高頻寬至關重要。如果示波器頻寬不足,可能滿足規範的DUT會被認為是不通過的。大多數標準把中間的範本都放在眼圖中央,然而,HDMI卻將範本進行偏移,因此,正確了解並掌握不同串列構架後,才採用眼圖測試方法極為重要。 |

| ‧ |

|

| |

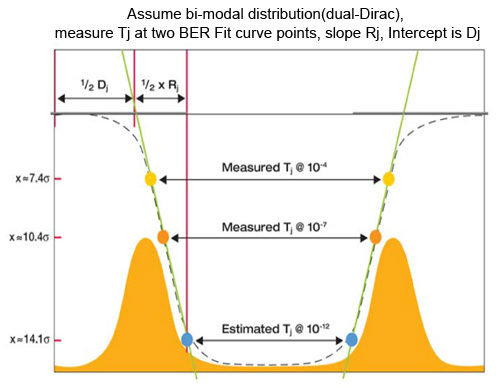

抖動測量的是訊號邊沿和恢復出的嵌入時脈邊沿的時間差,標準不同,CDR的方法也不盡相同,過大的抖動會引起系統誤碼率的惡化。確定性抖動(Dj)和誤碼率性能標準指明在誤碼率為10-12下考察總體抖動(Tj)容限。如果直接採集捕獲所需的UI,將非常耗時,因此規範採用的是另一種精確的評估演算法。 |

|

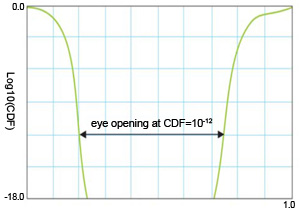

| 圖10 抖動浴盆曲線 |

不同的標準採用了不同評估演算法。一個通用的演算法是基於TIE抖動的概率分布函數(CDF)或者浴盆曲線(Bathtub)(圖10)。InifiniBand標準就是採用浴盆曲線;第一代PCI Express標準採用TIE的長條圖;而第二代PCI Express採用的是Dual Dirac模型(圖11)。

在BER為10-12條件下的抖動大小等於一個標準UI減去眼寬。Tj、抖動眼寬和UI的關係為Total Jitter+Jitter Eye Opening=1 Unit Interval。總體抖動(Tj)是由隨機抖動(Rj)和確定性抖動組成,而確定性抖動又由很多不同類型的抖動組成。

|

| 圖11 基於Dual Dirac的抖動眼圖張開度測量 |

Dj和Rj能從CDF中測量得到。高階即時和採樣示波器都能通過分析軟體進行Rj和Dj的抖動分離,抖動的分離能夠幫助工程師區分不同等抖動來源,進而從根源上消除抖動。

不是所有的抖動測量都是一樣,高速串列介面標準所定義的CDR模型是抖動測量區別的主要原因。這就意味著自動化測試工具必須針對某種特定的標準,採用相應的時脈模型。不同的方法會導致抖動測量結果的差異,因此,最重要的是和標準保持一致,可程式設計的CDR演算法模型和硬體的CDR電路可大大的簡化測量的任務。

高階示波器上提供抖動分析工具,這些工具能夠進行深入的、複雜的抖動分析和測量,包括眼張開度分析、TIE抖動頻譜分析、用Bathtub進行的BER分析,並整合在同一個示波器視圖中;對多次的測量結果還可做統計分析,工程師可非常直覺快速決定DUT是否滿足規範。

示波器捕獲越多的資料,抖動分析結果就越精確,這對於一致性測試很重要。測量低頻抖動對示波器有兩個衝突的需求:捕獲微小時間細節和長時間的記錄。意味著要用到很高的取樣速率,並儲存長時間的訊號,因此示波器必須能夠提供相應長度的儲存空間。現今的示波器最高取樣速率已可達到50GS/s,而且具有很大的儲存空間,足夠捕獲很長的時間訊號,以讓工程師確定低頻抖動對系統的影響。

(本文作者為太克資深技術經理)