目前有各種串列介面技術可滿足應用市場多樣化的需求。這些標準的關鍵性目標是在某一個體系框架內,讓不同製造商生產的設備能相互通用。

表1列出一些高速串列介面標準。每個標準是由一個管理機構、委員會和工作組,建立設計和測試要求。每個規範定義產品須符合的項目,包括電氣、光學、機械、互連等,並由管理機構發起標準化測試,檢驗產品是否能通過標準要求,且這些測試可能會詳細到指定具體的測試設備。以下列舉幾項高速串列介面標準,協助讀者進一步了解其特性。

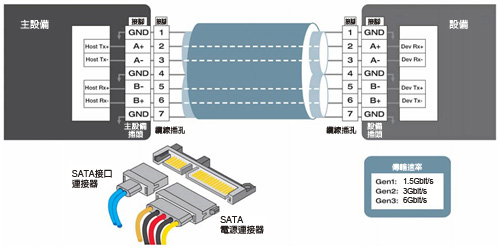

SATA介面是標準串列儲存介面,廣泛應用於桌上型電腦和其他計算平台。最初版的傳輸速率只達1.5Gbit/s,最新的3.0Gbit/s的第二代規範相關產品目前已商用。第三代標準規定傳輸速率是6Gbit/s。

SATA採8b/10b編碼

就如許多串列標準,SATA介面採用低電壓差分訊號(LVDS)和8b/10b編碼。資料在發射端和接收端間採用全雙工的資料通道,分別由一條發送通道(Tx)和一條接收通道(Rx)組成。SATA介面採用展頻時脈(SSC),因此並不將單獨的參考時脈傳送給接收端,圖1所示為SATA匯流排基本架構。

|

| 圖1 SATA匯流排機械結構 |

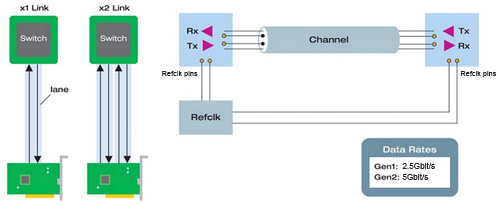

PCIe擴展性強

PCI Express已取代PCI成為大多數晶片到晶片的傳輸介面,或被用於電路板傳輸和電纜連線系統。PCIe是一個高度可擴展的架構,提供從一到十六條全雙工的PCIe連接。在多通道應用中,資料流程根據現有可用通道的情況而拆分,同時在多個通道上傳輸,最快的PCIe應用通常是影像處理應用,亦即通過十六條高速通道,在系統晶片組和圖形處理器間傳輸高解析度的圖形資料,圖2顯示PCIe架構。

|

| 圖2 PCI Express架構 |

第一代PCIe的每條通道傳輸速率是2.5Gbit/s;PCIe 2.0提供5Gbit/s的速率;第三代PCIe則提供8Gbit/s的傳輸速率。PCIe不僅採用嵌入式時脈,還將參考時脈傳輸到接收端做為鎖相迴路(PLL)參考時脈。

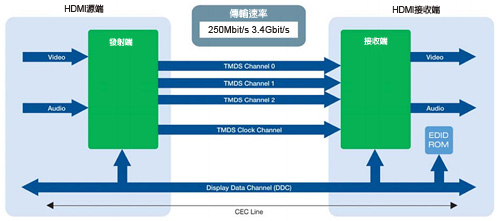

HDMI傳輸高畫質影音

高畫質多媒體介面(HDMI)是第一個專為滿足消費娛樂系統市場而推出的串列匯流排標準。HDMI介面建立在數位視訊介面(DVI)之上,並延伸更多功能、整合更多的娛樂設備,如大螢幕、高畫質電視和家庭影院系統。圖3所示為HDMI介面架構。

|

| 圖3 HDMI架構 |

HDMI是單向傳輸的架構,從源端向接收端傳送高解析度視頻和多頻道音訊。該規範定義三個高速串列資料通道,根據顯示器解析度,傳輸速率從250M~3.4Gbit/s。為追求更高的資料傳輸速率和更高的解析度,HDMI論壇(HDMI Forum)在機械部分規格定義Type B型連接器,將兩個HDMI介面並聯,可產生的最大傳輸速率為6.8Gbit/s。

雖然大多數高速串列標準依LVDS訊號格式和8b/10b編碼,但HDMI介面使用的是最小化傳輸差分訊號(TMDS),以減少連結訊號跳至錯誤的頻段,從而減少電磁干擾(EMI)。另外,HDMI介面採用參考時脈設計,時脈頻率為資料率的十分之一。HDMI透過低速串列匯流排(I2C匯流排),又稱為DDC的匯流排,在源端和接收端進行配置,以及識別時進行雙向訊號傳輸。

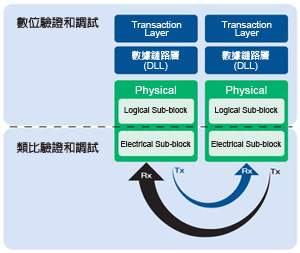

各串列匯流排結構基本要素相似

|

| 圖4 高速串列匯流排分層模型 |

所有的串列匯流排結構遵循如圖4所示的多層模型。實體層由電氣子層和邏輯子層構成,本文主要討論電氣子層上進行的一致性測試。

大多數高速串列介面標準的電氣子層有一些共通特性,包括利用差分訊號傳輸、展頻時脈與利用8b/10b編碼減少EMI,進而改善訊號完整性,同時使用嵌入式時脈和參考時脈。另一方面,高速串列介面典型的測量包含抖動、幅度、差分對間延時差(Inter-pair Skew),且規範和測試需求並隨著標準不斷發展而演進。

串列介面速率持續提升 量測挑戰隨之提高

高速串列介面技術不斷演化,訊號具有更快邊沿速率和更小的單位時間間隔(UI),因此工程師須在設計、一致性測試和調試過程中考慮很多特殊的要求。

在下一代高速串列介面的系統中,電子訊號的故障會更加嚴重影響介面訊號完整性和品質。訊號傳輸路徑上的導體,包括電路板走線、過孔、連接器和電纜等由於回波損耗和反射等傳輸線效應,也將嚴重降低訊號的位準、延緩上升時間,並產生更多的雜訊。

隨著高速串列介面標準定義的傳輸速度不斷上升,一個位元(bit)所占用的時間越來越短,LVDS和多位準訊號更加容易受到訊號完整性問題的傷害,如延遲、雜訊和碼間干擾(ISI)。此外,高速訊號對時序、發送端到接收端間的阻抗、系統級軟體和硬體的交互問題更加敏感,而多通道的結構則增加傳輸介面系統設計的複雜程度,以及提高通道間時間延遲和串擾發生的可能性。以下將說明串列介面邁向高資料速率時,將遭遇的問題。

| ‧ |

|

| |

高速串列介面採用嵌入式時脈系統意味著對抖動有更大的敏感,很可能由於抖動造成誤碼效能的惡化。抖動是由串擾、系統雜訊、同步開關輸出和其他有規律發生的干擾訊號產生,隨著高速串列介面傳輸速率不斷上升、多通道的設計和更加精巧的印刷電路板(PCB)布局,使上述干擾更易轉變為抖動。 |

| ‧ |

|

| |

PCB上會改變串列介面訊號傳輸特性的因素是分布電容、電感和電阻,而傳輸線效應將隨著高速串列介面訊號傳輸速率提升而發生,將影響訊號品質,並可能導致誤碼。 |

| ‧ |

|

| |

雜訊是出現在訊號幅度上的異常電壓,通常來自於系統的內部和外部。外部雜訊源有公用頻段干擾、空間輻射等;內部雜訊源包含數位時脈、高速晶片和開關電源。雜訊可能是瞬態或是寬頻的隨機雜訊,將導致訊號相位發生問題。就如抖動會影響訊號時序,雜訊會引起訊號幅度的異常,對系統誤碼率有至關重要的影響。 |

一致性測試確保訊號品質

高速串列介面的一致性測試規範中,通常包括幅度、時序、抖動和眼圖的測量。最新的串列標準則更加關注展頻時脈、接收端靈敏度的測試,以及電纜、連接器的回波損耗和反射。

| ‧ |

|

| |

|

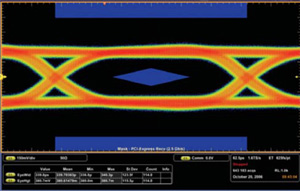

| 圖5 在示波器上進行高速串介面眼圖測試 |

眼圖測試是一致性測試中最關鍵的部分,如圖5所示,在示波器上得到的串列訊號的眼圖。眼圖測量透過從資料中恢復出的時脈進行觸發,對串列訊號在一個UI時間內多次疊加而形成。在眼圖的上、中、下方各有一塊測試失敗區域被稱為「範本」(深灰色部分),標明訊號不能進入的禁區。 |

| ‧ |

|

| |

幅度測試主要是驗證訊號能否到達規定的位準並保持穩定,能在傳輸媒介中可靠的向接收端發送"1"和"0"。 |

| ‧ |

|

| |

時序測試的項目列在表2,主要是驗證訊號是否存在異常的時序變化、是否有夠快的調變確保資料傳輸正確。時序測試需要高性能的測量工具檢測由分布電容、電阻,串擾等引起異常和訊號品質的惡化狀況。 |

| ‧ |

|

| |

隨著高速傳輸介面資料傳輸速率不斷提高,抖動問題成為最難解決的部分。許多量測儀器廠商開發專用的抖動分析工具,幫助工程師快速識別產生抖動的原因,以及抖動造成的結果。為保證相容性,資料發送端的抖動一定不能太大;而接收端須能容忍一定量的抖動,且能正確的進行時脈恢復(CDR),並解串列資料(De-serialize)。 |

時間間隔誤差(TIE)是許多抖動測量的基礎。TIE是恢復的時脈邊沿和實際波形邊沿的時間差值,透過對TIE進行長條圖分析和頻譜分析,可得到高級的抖動分析結果。

抖動測試通常需要較長的時間,因為工程師須連續採集上億個邊沿,才能確保對10-12誤碼率的準確表示。

| ‧ |

|

| |

接收端靈敏度的測試可證明接收晶片內部的CDR和解串列元件,能否在有外部干擾,如抖動、雜訊和時序問題的環境,準確的恢復時脈和資料。 |

| ‧ |

|

| |

傳輸媒介在訊號完整性中的作用越來越重要。在低成本的介質中,如FR4上,要設計速率超過Gbit/s的LVDS訊號,且訊號走線上有電纜、連接器等,會遇到很多布板設計以及測試上的挑戰,而許多的標準對介質的損耗、阻抗、串擾有嚴格的要求。 |

由於各類高速串列介面的特性與測試項目相似,因此可透過示波器測試多數高速串列介面,藉以確保高速串列介面訊號的品質、穩定性,以及不同廠家產品的相容性。

(本文作者為太克資深技術經理)