今天,駕駛輔助系統的處理需求超過現有汽車等級序列DSP的能力;此外,為提高消費者價值,以一組視覺感測器為基礎、結合多項駕駛輔助功能,已成為持續成長的需求,例如:前向視覺模組可能必須同時支援車道偏離警示、智慧型頭燈控制、以及號誌辨識功能,這些都需要不同的處理演算法,為FPGA帶來一個絕佳的市場機會。

許多汽車工程師採用各種智慧型技術來協助人類安全地操控汽車。汽車系統的重要包括雷達、超音波、以及攝影/視覺感測等。這些統稱駕駛輔助(DA)系統的技術,協助駕駛人在各種不利的環境與危險的路況下,安全地駕駛。

第一代以攝影器材為基礎的駕駛輔助系統,現已搭載於各種車款。這類系統大多數為駕駛人提供車輛周遭環境的動態影像。最常見的系統是停車/倒車輔助系統,使用後照攝影機來擷取車輛後方的影像,並把影像顯示在收音機/導航系統的螢幕,或是儀表板上的小螢幕。

第二代以攝影機為基礎的系統,目前正在研發與測試,並已小量部署。這些第二代系統不光為駕駛提供影像,還運用影像處理與分析技術,從影片中擷取資訊,分析與評估車輛周遭環境。必要時,駕駛會得到適當的警告。

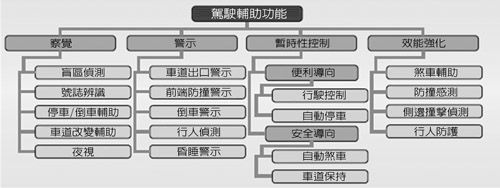

工程師在分析車輛環境時,會逐漸累積實務經驗,未來的駕駛輔助技術會提升精密度,為消費者提供更好的工具,並同時提升其他車輛子系統的效能。圖1歸納出各種現有與未來的駕駛輔助系統功能。

|

資料來源:作者整理

圖1 駕駛輔助功能 |

平行模式運作 FPGA效能高出DSP逾十倍

|

資料來源:賽靈思網站

圖2 FPGA具有彈性及擴充性 |

視覺型駕駛輔助方案的影像處理與分析功能,可加入空間/時間過濾、透鏡扭曲校正、影像銳利化、對比強化、邊緣偵測、圖案匹配、物體辨識、物體追蹤、以及圖形重疊等功能;其中,圖案匹配功能尤其重要,用以支援動態預測或立體像差計算。而現場可編程邏輯閘陣列(FPGA)可透過基本處理效能、組態彈性、以及元件的擴充性來提供系統價值(圖2)。

假設一個752×480畫素的寬螢幕VGA解析度影像裝置,如欲產生一個30Hz幀/秒(fps)的影片,須要預測物體在畫格之間的動作變化;一種適合立體範圍像差計算的演算法,便是將影像分割成4×4畫素的模組,作為第一個畫格中、每個模組評估的一個匹配標準,以便在第二個畫面中針對指定的搜尋區域(例如20×20畫素)進行搜尋。

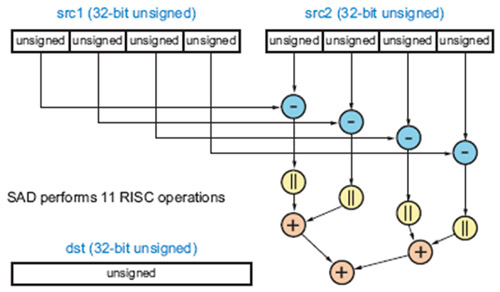

一個常見的匹配標準,就是運用一個名為「絕對誤差總和」(SAD)的運算子,在第一個影像中尋找4×4模組的畫素,與第二張影像搜尋區域之間的最低絕對誤差(MAE)。此例中,該4×4模組匹配範例需要超過250MMAE/s(每秒百萬次平均絕對誤差計算),因為(752畫素)×(480線)×(20×20畫素的搜尋區域)×(30fps)÷(4×4畫素模組尺寸)=270,720,000 MAE/s.。MAE代表4×4畫素模組的最終匹配誤差,SAD是指四個獨立元件部分的絕對差額計算總和。因此每個平均絕對誤差都需要四次SAD運算。

汽車設計工程師手中可行的處理選項,包括超長指令字元的數位媒體處理器(VLIW DSP-CPU)與FPGA。FPGA的處理功能遠勝過任何現有極低中頻(Very Low IF, VLIF)的DSP-CPU。儘管FPGA的時脈頻率遠低於DSP-CPU,但其大量的功能單元以平行模式運作(包括可程式化MAC),讓FPGA效能可高出一般數位訊號處理器(DSP)十至三十倍,實際速度端視應用而定(圖3)。

|

資料來源:作者整理

圖3 8位元畫素影片資料中四個元素的SAD運算,可建置在一個32位元架構DSP-CPU內SIMD裡,並有效率地在一個周期內執行十一個基本指令。 |

DSP會有周期延遲問題

一次處理超過一個4×4模組,尖峰效能可略為提高。例如,兩個4×4模組平行運算MAE值,可在七個周期內完成,達到85.71MMAE/s的速度;而三個模組可在九個周期內處理完成,約等同100MMAE/s的效能。

平行處理的模組數量上限,會受限於任何長指令字元允許的單一指令多重資料(SIMD)SAD運算數量、VLIW-CPU通用型暫存器的數量,以及最佳化編譯器的排程演算法。特別留意的是,由於加入更多模組時,整體效能會趨於飽和,故不考慮平行處理超過三個MAE。

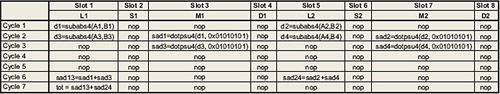

一般DSP-CPU透過兩個獨立的資料通道,每個周期可處理八個RISC運算的長指令--每個周期四個時槽的其中一個。VLIW-CPU在每個周期可執行兩個SAD指令,每個指令會有一個周期的延遲。但在累加所有部分結果後,必須運用一個常數0×01010101來執行一個延遲三個周期的SIMD MAC運算。

因此,一個600MHz的DSP-CPU能在七個周期內運算一個MAE,故在處理4×4畫素模組時能達到85.71MMAE/s的尖峰效能。若兩個模組平行處理,則需要九個周期及133.33MMAE/s的速度;然而三個模組則會用掉十一個周期與163.64MMAE/s的速度,仍低於250MSAD/s的要求水準。

FPGA能創造資源餘裕

假設每個畫素為8位元,相當適合32位元架構的DSP-CPU處理器。但新型互補金屬氧化半導體(CMOS)影像感測器有更高的解析度範圍,每個畫素為12~14位元。針對此類型的資料,32位元架構的傳統四重8位元子字元SIMD(表1),處理效率偏低,必須換成兩個16位元半字元SIMD(表2)。在SIMD中,子字元的平行度只有2,尖峰效能會大幅降低,需要更多的周期來進行MAE運算。

|

資料來源:作者整理

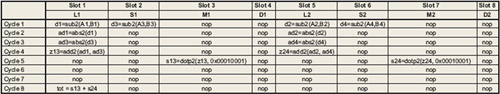

表1 運用四重8位元次字元平行模式,在VLIW DSP-CPU上執行偽組譯碼進行MAE運算。 |

|

資料來源:作者整理

表2 運用兩個16位元次字元平行模式,在VLIW DSP-CPU上執行偽組譯碼進行MAE運算。 |

表2顯示使用16位元次字元指令進行運算時,SAD在VLIW DSP-CPU進行運算時的偽組譯碼,並考量到校正延遲以及這類指令的函式發送時槽。因此,一個4×4模組需要八個周期,若平行處理兩個與三個模組時,則分別需要十與十二個周期;其尖峰效能分別為75MMAE/s、120MMAE/s以及150MMAE/s,都小於8位元次字元指令。

如果運用一個150MHz時脈頻率的FPGA元件,僅需要兩個平行架構、約占6%的元件空間,就能達到300MMAE/s的效能,並符合範例應用要求的250MMAE/s。如此能留下充裕的資源,以建置其他影像處理功能、資料傳送管線、記憶體介面控制器、以及32位元嵌入型處理器,用來進行序列處理與外部通訊作業。

以賽靈思(Xilinx)的Spartan 3A-DSP 1800A FPGA元件為例,150MHz的速度僅須運用70%的資源(最高能達到250MHz),即能以平行模式處理二十三個模組(70%×16,640 slices/508 slices/模組=23模組),相當於3,529MMAE/s尖峰效能,比一般DSP-CPU的600MHz尖峰速度至少高出二十五倍;僅以四分之一的時脈速度,就能提供多出一倍的效能。

另一方面,VLIW DSP-CPU在進行SAD運算時,資源使用率常會達到滿檔,使其少有機會藉由運用序列處理器長指令的時槽,來同步處理其他功能。相較之下,FPGA元件相當適合需要優異處理效能、彈性、以及擴充性的視覺型應用,滿足未來世代汽車駕駛對於駕駛輔助系統的需求。

(本文作者任職於賽靈思)