Cortex-M系列MCU節能效果再升級。晶片商基於Cortex-M CPU核心指令集的節能機制,可大幅縮減CPU循環週期、記憶體存取次數,再搭配自主型周邊解決方案,更能在CPU休眠模式下主動觸發計時器、DAC等元件,進一步節省CPU資源和耗電量。

對嵌入式開發人員來說,可選用的中央處理器(CPU)型號種類繁多,每一種CPU都有自身的獨特性、架構優勢並具備不同的節能技術。目前業界大多聚焦於廣泛使用的安謀國際(ARM)Cortex-M系列核心架構,這是非常有意義的,因為能為範圍廣泛的嵌入式CPU選擇提供一個有益的背景參考。

Cortex-M提供幾個CPU版本,同時擁有來自半導體晶片供應商的多種不同MCU產品。Cortex-M系列中的多樣性選項十分重要,因為最小化CPU功耗不僅取決於CPU本身的架構,還須透過周邊元件支援,例如中斷控制器、儲存介面、儲存加速器、低功耗模式和智慧周邊等。本文將探討如何降低搭載Cortex-M核心微控制器(MCU)功耗的方式。

縮減運算循環週期 Thumb-2提升CPU執行效率

首先從一個看起來不顯眼的起點開始討論MCU節能技術--指令集。所有Cortex-M CPU都使用Thumb-2指令集,它融合32位元ARM指令集和16位元Thumb指令集,並且為原始效能(Raw Performance)和整體代碼大小提供靈活的解決方案。在Cortex-M核心上,一個典型的Thumb-2應用程式與完全採用ARM指令完成的相同功能應用程式相比,代碼大小可縮減約25%,而執行效率達到90%(當執行時間進行最佳化後)。

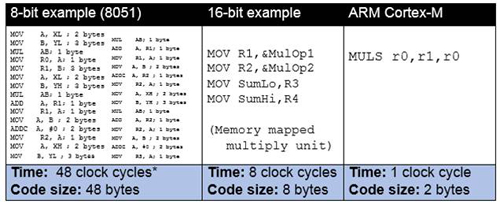

Thumb-2中包含許多功能強大的指令,能有效減少基礎運算所需的循環週期(Cycle Count)。減少循環週期數意味著系統能以更少的CPU功耗,完成手上的工作,例如要完成一個16位元乘法運算(圖1),在8位元8051核心的MCU上執行將需要四十八個循環週期,並占用48bytes的快閃記憶體(Flash)儲存空間;若使用16位元核心的MCU(例如C166)執行相同運算則需八個循環週期,並占用8bytes的Flash儲存空間。相較之下,在使用Thumb-2指令集、Cortex-M3核心的MCU中,相同運算僅需一個循環週期和2bytes的Flash儲存空間。

|

| 圖1 不同處理位元形式的CPU循環週期對照表 |

Cortex-M3核心能使用更少循環週期完成相同任務,因而大幅節省能耗;同時也能夠透過占用較少的Flash空間,減少記憶體存取次數,實現最終能耗節省的目標(除此之外,更小的應用代碼也使得系統可以選擇更小的Flash記憶體,進一步降低整體系統功耗)。

接下來將用較多篇幅討論Thumb-2指令集中的各種重要技術,並探討其他MCU周邊元件對節能帶來的幫助。

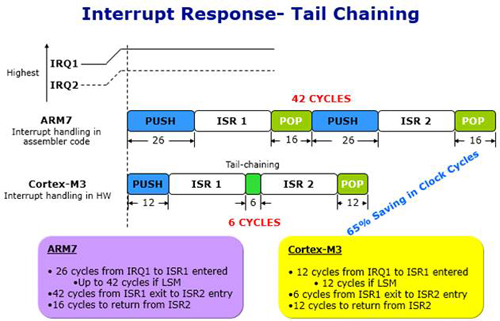

採用末尾連鎖技術 NVIC減少中斷循環週期

Cortex-M架構中的中斷控制器(Nested Vectored Interrupt Controller, NVIC)在降低CPU功耗方面也具有關鍵作用。過往的ARM7-TDMI需多達四十二個循環週期,Cortex-M3 NVIC從插斷要求發生到執行中斷處理代碼僅需十二個循環週期的轉換時間,顯然提高CPU執行效率,避免時間浪費。如此一來,MCU除可更快進入中斷處理程序外,亦可提升中斷之間的切換效率。

在ARM7-TDMI核心實現中,須先花費數個循環週期,由中斷處理程序返回主程序,再進入到下一個中斷處理程序中,中斷服務程式之間的「中斷服務程式之間的堆疊(Push-and-pop)」操作就要消耗多達四十二個循環週期。而Cortex-M NVIC採用更有效的方法實現相同任務,被稱為「末尾連鎖(Tail-chaining)」。這種方法使用僅需六個循環週期處理,就能進入下一個中斷服務程式的所需資訊。採用末尾連鎖,工程師不須進行完整的堆疊,這使得管理中斷過程所需的循環週期數減少65%(圖2)。

與此同時,指令集中的記憶體介面和記憶體加速器也會明顯影響CPU的功耗。

|

| 圖2 ARM7和Cortex-M3的中斷響應比較 |

促進記憶體節能 推測取出指令提升存取速度

代碼中的分支和跳轉,可能對為CPU提供指令的管線(Pipeline)產生刷新影響,在這種情況下,CPU須延遲幾個循環週期以等待管線重新完成填充。在Cortex-M3或Cortex-M4核心中,CPU配備一條三級管線,若刷新整條管線將導致CPU延遲三個循環週期,而且當Flash記憶體等候狀態發生,時間還會更長,以便完成重新填充過程;這些延遲完全浪費功耗,沒有任何功用。

為減少延遲,Cortex-M3和M4核心內建推測取出指令(Speculative Fetch)功能,即它在管線中對分支進行取出指令,同時也取出指令可能的分支目標;如果可能的分支目標命中,那麼推測取出指令能夠把延遲降低到一個循環週期。雖然這個功能是有用的,但顯然不夠,許多Cortex-M產品供應商都增加自己的矽智財(IP)以強化這個能力。

舉例來說,Cortex-M MCU中的指令緩衝運行方法不盡相同,採用簡單指令緩衝的MCU,例如芯科實驗室(Silicon Labs)的EFM32產品,可儲存128×32(512bytes)的目前多數執行指令。EFM32參考手冊指出典型應用在這個緩衝中將有超過70%命中率,這意味著極少的Flash存取、更快的代碼執行速度和更低的整體功耗。

與此同時,採用64×128位元分支緩衝器的MCU能儲存最初的幾條指令(取決於16位元或32位元指令混合,每個分支最多為八條指令,最少為四條指令),因此,分支緩衝實現能在一個循環週期內,為命中緩衝的任何分支或跳轉填充管線,消除任何CPU循環週期延遲或浪費。

兩種緩衝技術與同類型沒有緩衝特性的CPU相比,皆提供相當大的效能改善和功耗減少。這兩種緩衝類型也最小化Flash存取次數,有效降低MCU整體功耗。

減輕管線資源浪費 Cortex-M0+節能表現出色

對功耗敏感型應用來說,每個Nano-watt都很重要,Cortex-M0+核心是一個適合的選擇。M0+基於范紐曼型(Von-Neumann)架構(Cortex-M3和Cortex-M4核心是哈佛(Harvard架構)),這意味著它具有更少的閘道數量實現更低的整體功耗,且僅損失極小的效能(Cortex-M0+的0.93DMIPS/MHz對比Cortex-M3/M4的1.25DMIPS/MHz)。它也使用Thumb-2指令集的更小子集,幾乎所有的指令都有16位元的操作碼(52×16位元操作碼和7×32位元操作碼;資料操作都是32位元),這使得它可進一步降低CPU功耗。

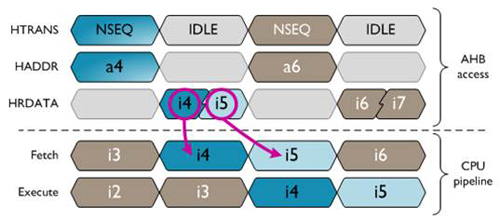

節能首要措施就是減少Flash存取次數,一個主要的16位元指令集意味著你可以交替循環存取Flash記憶體(圖3),並可在每一次Flash存取中為管線獲取兩條指令。假設在記憶體中有兩條指令,並對齊成一個32字元組(32bit Word);在指令沒有對齊的情況下,Cortex-M0+將禁止剩餘的一半匯流排,以節省每一點能耗。

|

| 圖3 基於Cortex-M0+中Flash存取的交替循環 |

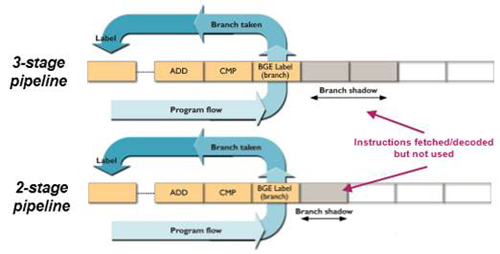

另外,Cortex-M0+核心也可透過減少至兩級管線而降低功耗。在通常的管線式處理器中,下一條指令在CPU執行當前指令時被取出。如果程式產生分支,並且不能使用下一條取出的指令,那麼被用於取出指令(Branch Shadow)的功耗就被浪費了。在兩級管線中,這個Branch Shadow縮小可節省能耗(雖然僅有少量),它也意味著在發生管線刷新時,僅需不到一個循環週期就能重新填充管線(圖4)。

|

| 圖4 管線和Branch Shadow架構圖 |

Cortex-M0+利用高速GPIO埠節能

Cortex-M0+核心提供節能特性的另一個關鍵是它的高速通用輸入輸出(GPIO)埠。在Cortex-M3和Cortex-M4核心中,反轉位元或GPIO埠的過程是「讀-修改-寫」一個32位元暫存器,雖然Cortex-M0+也使用這個方法,但是它還有一個專用的32位元I/O埠,可採用單一循環週期存取GPIO,進而能高效的反轉位元/接腳。此一功能在Cortex-M0+上是一個選配的特性,並不是所有供應商都具備這個有用的GPIO特性。

CPU休眠模式再添節能保障

事實上,降低CPU功耗最有效的方法之一就是關閉CPU。在Cortex-M架構中有多種不同的休眠模式,每一種都在功耗和再次執行代碼的啟動時間之間進行折衷考量,能讓CPU在完成中斷服務後,不須執行任何代碼就能自動進入某種休眠模式。這種方法可為那些常見於超低功耗應用中的任務,進一步節省CPU循環週期。

至於在深度睡眠模式下,MCU也可使用喚醒中斷控制器(WIC)來減輕NVIC負擔。在使用WIC時,為實現低功耗模式下外部中斷喚醒CPU,毋須為NVIC提供時脈。除了核心指令集對功耗影響甚鉅外,MCU周邊元件亦在節能方面扮演吃重的角色。

減輕CPU負荷 自主型周邊獨立完成觸發

MCU內建的自主型周邊具有降低功耗的優點,大多數MCU供應商皆已在本身產品架構中實現自主周邊互動,例如芯科實驗室的EFM32 MCU使用周邊反射系統(PRS),能實現十分複雜的周邊動作鏈(觸發而不是資料傳輸),同時使CPU處於休眠狀態。

例如,使用EFM32 MCU的PRS功能,其應用程序被配置為在CPU休眠的低功耗模式下,當晶片比較器檢測電壓值超過預設限值時,則會主動觸發一個計時器,並開始進行倒數。當計時器到達0時,觸發DAC開始輸出,所有事件發生過程中CPU可一直保持休眠狀態。

自動進行如此複雜的互動,使周邊元件之間能夠完成大量工作,而無需MCU處理核心的參與,對系統節能將大有幫助。另外,具有內建智慧型的周邊(例如感測器介面或脈衝計數器),還能透過預設條件用於中斷喚醒CPU,例如在累積十個脈衝時中斷喚醒CPU。在這個例子中,當CPU被特定中斷喚醒時,它明確知道須做什麼,而不須檢查計數器或暫存器以判別發生什麼情況,因此可節省相當多的循環週期以完成其他重要任務。

本文介紹多種易於實現的方法以減輕Cortex-M元件的功耗。除此之外,當然還有其他因素會影響功耗,例如用於加工設備的處理技術,或用於儲存應用代碼的記憶體技術,均會顯著影響系統運行時的功耗和低功耗模式下的漏電情形,因此也應當納入嵌入式開發人員的整體功耗設計考量中。

(本文作者為Silicon Labs微控制器和無線產品資深行銷經理)