全球微波存取互通介面(WiMAX)對寬頻網路連結,如同手機對語音通訊一樣重要。它可以取代數位用戶迴路線(DSL)和有線服務,為使用者隨時隨地提供網路連結。用戶只須打開電腦,連接到最近的WiMAX天線,就可以暢遊全世界的網路了。

寬頻網路連結遇到的最大挑戰之一是移動性,而這正是最新WiMAX標準所要解決的。IEEE 802.16e-2005介紹了傳輸和接收過程中採用多種天線的方法,即多重輸入多重輸出(MIMO)概念,這是行動式WiMAX的一個關鍵特性。

MIMO設計受倚重

空間分割多工(Spatial-division Multiplexing, SDM)MIMO處理可顯著提高頻譜效率,進而大幅增加無線通訊系統的容量。空間分割多工MIMO通訊系統可作為一種能夠大幅提升無線系統容量和連接可靠性的方法,近來也獲得人們的廣泛關注。

MIMO無線系統最佳硬決策(Hard Decision)偵測方式是最大似然法(Maximum likelihood, ML)偵測器。ML偵測因為誤碼率(BER)效能出眾,非常受歡迎。不過,直接建置的複雜性會隨著天線和調變方案的增加呈現指數型上升,使特殊應用積體電路(ASIC)或現場可編程閘陣列(FPGA)僅能用於使用少數天線的低密度調變方案。

在MIMO偵測中,既能保持與最佳ML偵測相媲美的BER效能,又能大幅降低計算複雜性的出色方法,非球形偵測法莫屬。這種方法不僅能夠降低SDM和空間分割多工連結系統的偵測複雜性,同時又能保持與最佳ML偵測相媲美的BER效能。實現球形偵測器(SD)有多種方法,每種方法又有多種不同演算法,因此設計人員可以在諸如無線通道的傳輸量、BER及建置複雜性等多項效能指標之間尋求最佳平衡。

雖然演算法如K-best或深度優先搜尋(Depth-first-search)和硬體架構,對MIMO偵測器的最終BER效能有極大影響,不過一般在球形偵測之前進行的通道矩陣預先處理也會對MIMO偵測器的最終BER效能產生巨大影響。通道矩陣預先處理可繁可簡,例如根據對通道矩陣進行的差異計算結果(Variance Computation),計算出處理空間多工資料流程優先順序,也可以使用非常複雜的矩陣因數分解方法來確定更為理想(以BER衡量)的資料流處理優先順序。

Signum Concepts是一家總部位於聖地牙哥的通訊系統開發公司,一直與賽靈思(Xilinx)和萊斯大學(Rice University)共同合作,運用FPGA設計出可用於802.16e寬頻無線系統的空間多工MIMO的MIMO偵測器。該處理器採用通道矩陣預先處理器,實現類似貝爾實驗室分層空時(BLAST)結構上採用的連續干擾抵消處理技術,最終達到接近最大似然法的效能。

系統考慮須周全

一般理想情況下,偵測過程會要求對所有可能符號向量組合進行ML解決方案計算。球形偵測器旨在透過使用簡單的算術運算降低計算複雜性,同時還能夠保持最終結果的數值完整性。採行的方法是,第一步是把複雜的數值通道矩陣分解為只有實數的運算式。這個運算會增加矩陣維數,但也簡化處理矩陣元的計算。降低計算複雜性的第二個方面體現在減少偵測方案分析和處理的可選符號。其中,對通道矩陣進行QR分解是非常重要的一步。

|

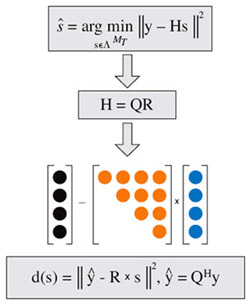

| 圖1 用於球形偵測器MIMO偵測的部分歐基里德距離度量方程式 |

圖1顯示如何進行數學轉換,得出計算部分歐基里德距離度量法的最終運算式。歐基里德距離度量法是球形偵測過程的基礎。R代表三角形矩陣,用於處理以矩陣元rM,M開始的可選符號的迭代法。M代表通道矩陣以實數表達的維數。該解決方案透過M次迭代定義出樹追蹤(Tree Traversal)結構,樹的每層i對應第i根天線的處理符號。

實現樹追蹤有幾種可選方法。在本例建置方案中使用廣度優先搜尋法,這是因為該方法採用備受歡迎的前饋(Feed-forward)結構,也因為如此,所以具有Hardware-friendly特性。在每一層,該建置方案只選擇K個距離最小的倖存節點來計算擴展情況。

球形偵測器處理天線的次序對BER效能有著極大影響。因此在進行球形偵測前,此處採用類似於垂直貝爾實驗室階層式時空(V-BLAST)技術的通道重新排序技術。該方法透過多次迭代,計算出通道矩陣虛擬反矩陣(Pseudo-inverse)的行列範數,然後確定通道矩陣最佳列偵測次序。根據迭代次數,該方法可以選擇出範數最大或者最小的行列。歐基里德範數最小的反矩陣行列表示天線的影響最強,而歐基里德範數最大的行列則表示天線的影響最弱。這種新穎的方法首先處理最弱的資料流,隨後依次迭代處理功率從高到低的資料流。

為實現上述系統,這裡採用賽靈思Virtex-5 FPGA技術。該設計流程採用賽靈思System Generator進行設計捕捉、模擬和驗證。為了支援各種不同數量的天線/用戶和調變次序,將偵測器設計為可用於需求最高的4×4、64QAM情況下。

此處的模型假設接收方非常清楚通道矩陣,這可以透過傳統的通道估算方法來實現。在通道重新排序和QR分解之後,開始使用球形偵測器。為準備使用軟輸入、軟輸出通道解碼器如Turbo解碼器,透過計算偵測到位元的對數似然比(LLR)來產生軟輸出。該系統的主要架構元素包括資料副載波處理和系統子模組管理功能,以便即時處理所需數量的子載波,同時最大程度地降低處理延遲。對每個資料副載波都進行通道矩陣估算,並限定每個通道矩陣可用的處理時間。對選中的FPGA而言,其目標時脈頻率為225MHz,通訊頻寬為5MHz,相當於WiMAX系統中的三百六十個資料子載波,而每個通道矩陣間隔可用的處理時脈週期數為六十四。此外,設計過程中採用硬體功能單元精湛的流水線和分時多工(TDM)功能,以達到WiMAX正交分頻多工(OFDM)符號的即時要求。

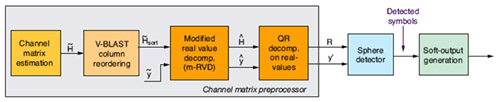

除了高資料率外,在架構設計指導過程中控制子模組延遲也是一個重要問題。透過引入連續通道矩陣的TDM解決了延遲問題。這種方法可以延長同一通道矩陣元之間的處理時間,同時還能保持較高的資料傳輸量。構成TDM組的通道數會隨著子模組的不同而變化。在TDM方案中,通道矩陣反轉過程用了五個通道,而有十五個通道在實數QR分解模組中進行了分時多工。圖2是該系統的高階流程圖。

|

| 圖2 MIMO 802.16e寬頻無線接收器的高階流程圖 |

通道矩陣預先處理

通道矩陣預先處理器確定了空間多工複合訊號每一層的最佳偵測次序。該預先處理器負責計算通道矩陣的虛擬反矩陣範數,並根據這些範數,選擇待處理的下一個傳輸流。虛擬反矩陣中範數最小的行列對應著最強傳輸流(檢波後雜訊放大最小),而範數最大的行列對應著品質最差的層(檢波後雜訊放大最大)。這裡的建置方案首先偵測最弱的層,然後按最低雜訊放大到最高雜訊放大的順序逐層偵測。對排序過程中的每一步,通道矩陣中相應的列隨後會被清空,然後簡化後的矩陣進入下一級的天線排序處理流水線。

在預先處理演算法中,虛擬反矩陣的計算要求最高。這個過程的核心是矩陣反轉,通常透過Givens旋轉進行QR分解(QRD)來實現。常用的角度估算和平面旋轉演算法如座標軸數位旋轉計算器(CORDIC),會造成嚴重的系統延遲,這對系統來說是無法接受的。因此,目標是運用FPGA的嵌入式DSP資源如Virtex-5元件中的DSP48E,找出向量旋轉和相位估算的替代性解決方案。

|

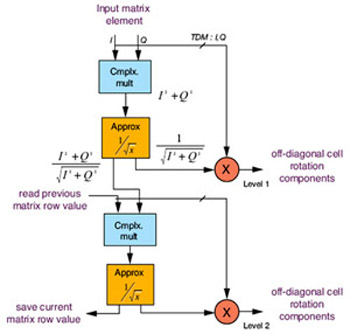

| 圖3 對角線脈動單元結構圖 |

QRD的脈動陣列結構由兩種類型的處理單元構成--對角線單元或邊界單元,和非對角線單元或內部單元。邊界單元執行向量函數,可以產生陣列內部單元使用的旋轉角度。可以把非對角線單元中的值與對角線單元中的共軛複數相乘,然後除以複數的倒數即可獲得想要的旋轉角度。相除實際是用乘法的方式完成的,即在觀察到函數接近線性時,乘以根據定義的間隔的多項式近似值計算出的倒數。圖3顯示了採用這種近似值在對角線脈動單元中完成複雜旋轉的訊號流程圖。

發送到非對角線單元中的資料是旋轉向量的同相部分和正交部分除以相應的近似值得出的結果。這裡不僅透過在對角線單元和非對角線單元採用流水線架構實現高資料傳輸量,同時還透過對跨五個通道的硬體進行時分複用的方式,控制近似值模組和複雜乘法器引起的延遲。

對4×4矩陣,這裡使用一個對角線單元和七個非對角線單元。分解單個矩陣所花的處理時間為4×4=16個資料週期,而該設計交付資料的速度是每三個時脈週期一個樣本,因此分解單個矩陣的所用的總時長為3×4×4=48個時脈週期(低於可用的六十四個時脈週期)。接著,對分解後的矩陣使用了回代法(Back Substitution),同時以相同的TDM方式進一步進行重新排序操作。

球偵測器採用部分歐基里德距離(PED)單元進行範數計算。根據樹的層次,採用了三種不同類型的PED單元。根節點PED模組負責計算所有可能的PED。二級PED模組針對上一級計算得出的八個倖存路徑計算出八個可能的PED。這樣在樹的下一級索引中,就有六十四個會產生的PED。第三種類型的PED模組用於其他樹級,負責計算上一級計算出的所有PED最鄰近節點PED。

球形偵測器(SD)的流水線架構可以在每個時脈週期中處理資料。其結果就是樹的每級只需要一個PED模組。因此,對4×4 64QAM系統而言,PED單元的總數為八,與樹的級數相等。SD可以採用硬解碼和軟解碼兩種類型的解碼技術。硬解碼能夠用貫穿樹的各級的最小距離矩陣度量次序;軟解碼用對數似然比來代表輸出的每個位元組。對數似然比一般被當作優先輸入值提供給通道解碼器,例如Turbo解碼器。

建置和模擬包括圖2所示的偵測過程,但不 包括軟輸出產生模組。目標晶片是Virtex-5 XC5VFX130T-2FF1738 FPGA。設計的時脈頻率為225MHz,可用的資料率為83.965Mbit/s。表1顯示設計中每個主要功能單元的資源占用情況。利用率(%)表示FPGA面積占XC5VFX130T元件總面積的百分比。

System Generator實現完整偵測鏈

這裡使用針對DSP設計流程的賽靈思System Generator實現完整的偵測鏈。設計驗證工作不僅使用MATLAB/Simulink環境的模擬語義,還有System Generator的協同模擬功能。通道矩陣參數的同相部分和正交部分從正常的分布得出,並由MATLAB交付給System Generator建模(Modeling)環境。這裡同樣使用這種模擬框架進行誤碼率計算。圖4對定點硬決策設計BER曲線、浮點硬決策設計BER曲線和最佳ML參考曲線進行比較。透過對賽靈思ML510開發平台進行基於乙太網的硬體協同模擬,開發出該設計的硬體展示。通道矩陣參數採用賽靈思AWGN IP核發送給球形偵測器。接著,透過把設計嵌入到自同步BER測試器來計算BER。該儀器能夠向偵測器發送輸入並捕捉誤碼。

(本文作者Milos Trajkovic、Slobodan Denic、Dragan Vuletic任職於Signum Concepts,Chris Dick、Raghu Rao任職於賽靈思,Kiarash Amiri為萊斯大學研究生及賽靈思實習生)