對於系統設計來說,控制電磁輻射是一個關鍵考量因素。目前市面上各種先進電子產品的電磁輻射大多來自於高速的數位時脈訊號。隨著時脈頻率增加,將產生更多的電磁干擾(EMI)。

由於美國聯邦通訊委員會(FCC)與其他監管機關嚴格規定每個電子產品的電磁干擾上限,因此以上的情況將會產生嚴重問題。這些法規是為確保電子產品不會產生互相干擾,例如:當你在講電話時,也能同時使用電視遙控器。

本文將詳述電磁干擾與其對美國聯邦通訊委員會認證的影響。此外,亦將介紹能夠降低電磁干擾的其他解決方案,以及展頻時脈產生器(SSCG)的優勢。

EMI防治挑戰日益艱鉅

當電流通過電路時,會產生電磁場。這個磁場從設備的電子線路向外發射,其強度則取決於電流的頻率與大小。任何電子電路所需功能以外的多餘副產品就被稱為電磁干擾。

電磁輻射的來源可能是像手機等無線通訊裝置,由於這類裝置是以電磁輻射來實現其通訊功能,因此又被稱為「意圖發射源」。然而,包含個人電腦(PC)、個人數位助理(PDA)、影印機、掃描機與數位相機等裝置,即便不是射頻通訊系統,在操作的過程中也會產生電磁輻射,因此這類產品又被稱為「非意圖發射源」。數位系統中的高頻率週期性時脈訊號是電磁干擾發射的主要原因,因為這些是最高頻率的週期性訊號,且這些能量不僅集中在傳輸高峰,更會分布在個別的頻率諧波上。

控制與時序訊號、位址與資料匯流排、排線互連與連接器亦會讓電磁干擾增加。這種輻射訊號將影響設備本身或周邊其他設備的效能。

屏蔽與濾波是兩種最常用來控制電磁干擾的方法,但是這兩種方法的成本頗高,且當頻率增加時,傳輸線與接地阻抗的效果會讓輻射增加、波長減少,進而讓屏蔽與濾波不能完全發揮作用,因此只能算是治標的對策。

在系統開發的過程中,要保持關鍵的訊號完整性及進行電磁干擾模擬,必須仰賴難以預測的模組與參數萃取,而讓這兩項作業不僅困難、浪費時間且容易出錯。而因為穩定增加的時脈速度與日漸減少的供給電壓,讓這種情形隨著每一世代產品的演進而更加惡化。

涵蓋範圍廣大 FCC標準無可迴避

即使是重重挑戰,降低電磁干擾對於FCC與其他認證機構來說是非常重要的任務。對於使用時脈或振盪器、在高於9kHz頻率下運作及使用數位技術的各種電子產品,即便是非意圖無線射頻發射源,只要是要在美國境內銷售,均須通過FCC所制定的EMI規範。

因此,幾乎所有內建微處理器或微控制器的產品,都必須通過FCC的EMI相容性認證。因為若無適當的設計方法加以控制,即便是一個非意圖發射源,也會產生並發射出大量能量,進而影響其他裝置。

直到目前為止,確定一個裝置不會影響另一個裝置功能的技術仍不是一種精確的科學,且由於產品組合太過複雜,認證單位不可能針對每種產品組合均進行檢測,因此相關主管機關莫不採取從嚴把關的態度。

|

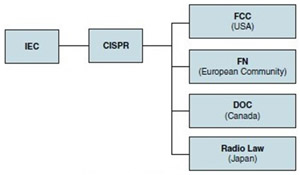

| 圖1 各國電磁干擾標準均由IEC下的CISPR制定 |

然而,目前有許多標準可讓消費者的數位裝置免於遭受這種困擾。針對電磁波所訂定的這些標準價值在世界各地已愈來愈受重視。圖1顯示國際無線電干擾特別委員會(CISPR)針對每個國家所發射的電磁干擾所制定標準。CISPR是國際電工委員會(IEC)的特別委員會。

表1顯示歐洲、日本、亞洲與美國等國都有不同的限制。為了要將電子品行銷全世界,這些產品必須符合各國的法規規定。任何可降低峰值能量的方法,都可以幫助產品符合這些要求。

如果要在美國境內銷售電子產品,FCC要求產品必須經過在電磁干擾範圍的特定環境下測量其電磁干擾。這些裝置在特定的頻率波段中,必須讓其電磁輻射遠低於特定值。

如果更進一步細看各國對EMI的規範,便可發現監理機關很注重發射主峰,而非一般發射值。以FCC為例,其規範便依據針對電壓、距離與頻率,規定輻射能量的限度。

在美國境內,FCC提供兩種等級的輻射層級:A等級與B等級(表2)。A等級的裝置是適用於商業、工業與工作環境的數位產品,而不是消費者平常或在家可使用的產品。

而B等級的數位產品則不僅適合家用,亦可在其他環境下使用。大致上來說,B等級的標準較A等級更為嚴苛。

表2列出美國聯邦通訊委員會的規則與規範之第十五條,規定A等級產品的電壓層級為10公尺,而B等級電壓層級為3公尺。

假設待測物(DUT)超過這些限度,則多餘能量必須降至表2所列出的限度以下。如果電磁干擾能量只是剛剛好低於規定限度是非常危險的,因為這些能量會因為製造過程與環境的改變稍微提高。

大多數的企業均要求安全限度,即使製造過程或環境條件改變,還是能確保這些裝置可完全符合美國聯邦通訊委員會的規範。在第五諧波上降低過量的特定干擾頻率是很困難的。如果企業強行將安全限度提升至4dB,則會讓這問題更加嚴重。

|

| 圖2 FCC電磁相容認證標章 |

美國聯邦通訊委員會驗證過的產品將會貼上如圖2的標章。一旦驗證通過,則產品即可在全美各地銷售。如果企業無法在市場機會最多之時,及時符合規範要求,將會導致產品上市時程延遲或取消上市計畫。

避免掉入FCC電磁相容認證十大陷阱

根據筆者的經驗與所收集到的資料,列出以下十大常見的FCC首關認證失敗原因,以供讀者參考。

整體來說,輕忽大意或對自家產品的輻射能量預估過度樂觀,往往是設計人員掉入陷阱,導致產品上市時程延宕最主要的原因。

EMI測試成本高昂

要通過FCC的電磁相容認證,產品製造商若想建立自有的測試能力,必須在基礎架構上進行不少投資,人力和時間等資源的耗用也不容小看,因此FCC電磁相容認證的成本可說是相當高昂。

測量電磁干擾需要一個大型的基礎架構與設施。電磁干擾測試設施可以區分成密閉式測試空間(圖3)與開放型測試空間兩種。

|

| 圖3 電磁干擾測試設施 |

前者是在一間小房間內放置幾個天線,以測量產品發射的電磁波,後者則是在一個幾英畝大的戶外空間中進行。測試設施、設備與方法必須先獲得政府的認可,其測試結果與品質才能夠達到符合法律效力的認證目標。

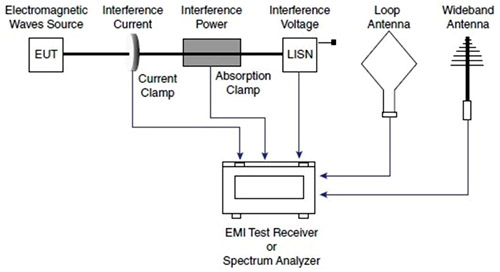

測量電磁干擾的方法與測試一般射頻的方法大為不同,且要發展出一套完整輻射測試步驟的時間與金錢成本是很高的。在電磁干擾的測試中,工程師無法預知訊號狀況。由於每個待測設備都是新的,且規格種類不同,正確選用可分辨出電磁干擾訊號的工具極為關鍵。為測量待測試備的輻射,必須使用環狀天線、寬頻天線與頻譜分析儀,或電磁干擾測試接收器來測量輻射程度(圖4)。

|

| 圖4 電磁干擾測試建置範例 |

此外,了解選用工具的優點與缺點亦非常重要,所以需要經驗豐富的工程師來執行測試,人力成本也因而提高。

除了測試設備投資與人力成本外,為通過FCC電磁干擾相容性認證所須進行的文件作業也相當龐雜。

終端產品製造商必須檢附完整測試計畫、美國聯邦通訊委員會規範第十五條的A、B等級產品的測試數據、詳述測試過程與使用標準的測試報告,並將技術檔案、美國聯邦通訊委員會相容文件(DoC)一併呈交主管機關。DoC文件是美國聯邦通訊委員會的官方文件,上面載明產品符合標準,且已通過標準認證。

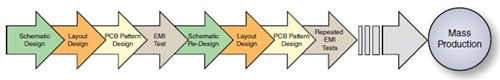

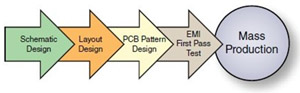

如果第一次無法符合法規要求,則工程師須要重新編寫電磁干擾屏蔽技術。過程中將須要重複修改系統設計與硬體,直到通過美國聯邦通訊委員會測試的所有步驟為止。圖5詳示重複性的設計變更、包含印刷電路板電路布線修改的重新驗證、濾波器建置(增加材料清單成本)及第二次測試設施的使用成本(如租金、文件撰寫等費用),以求符合法規要求。

|

| 圖5 傳統降低電磁干擾的多重步驟系統設計流程 |

展頻策略有助降低電磁干擾

在系統設計初期與產品測試之前,若先考量電磁干擾因素,將為企業大幅節省投入的時間與金錢。幸運的是,目前已有各種避免電磁干擾過量的機械式與電子式解決方案,並適用於各種系統設計方案上。

傳統上,濾波與屏蔽是兩種最常用來解決電磁干擾的方法。然而這兩種方法在成本、時間與資源運用上來說,均有其缺點。例如濾波法通常須使用價值約0.25美元的電阻器、電感器與電容器,以及價值0.75美元的共模扼流圈與環形線圈。

在很多情況中,濾波的方法不足以讓系統通過電磁干擾測試;這時就必須採用更昂貴的屏蔽解決方案。採用屏蔽策略往往會讓系統成本提高幾塊美元。

另一種可解決訊號發射過量的方法就是時脈調變,也就是所謂的展頻。約在1990年時,企業開始將時脈調變應用在電腦系統設計上。

到目前為止,展頻時脈因其更快的時脈速度及與小尺寸高解析度液晶顯示器(LCD)的整合度提高之優勢,已被普遍應用在手持式電子裝置上,例如手持式導航系統與掌上型遊戲機等。因為這些裝置的體積通常輕薄且價格實惠,因此如電容器或屏蔽等被動式降低電磁干擾的方式已不可行。

展頻是透過頻率調變來分散能量,而不是將參考能量集中在單一頻率上。不像濾波與屏蔽的方式是在電磁波產生後,才抑制電磁干擾;展頻時脈產生器是在系統時脈源頭就抑制電磁干擾。此方式可讓系統電磁干擾降至20dB左右。在更高的諧波頻率上,降低幅度會達到最高,展頻時脈產生器針對降低共模雜訊是最難控制的部分之一。

透過在更寬的頻帶上分散輻射,展頻時脈調變的效果卓著。在數百kHz速率上,透過頻率調變微控制器或處理器時脈,此頻帶可隨著輻射層級持續降低而擴展。因此,了解決定一個頻譜系統設計的最理想架構變得非常重要,可進而加速設計流程。

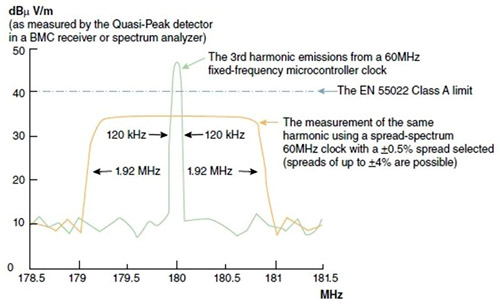

圖6顯示頻率速率的改變在最低與最大峰值頻率上是較為快速的;而由於架構因素,在頻率頻譜中央的改變是相對緩慢的。

|

| 圖6 頻率速率的改變 |

根據表2,若要符合FCC B等級電磁相容認證要求,60MHz的時脈(如圖6所示)必須低於40dBuV/m。低頻率調變速率因為多種因素變得相當重要。

如果調變速率低於120kHz,系統則可能出現音頻雜訊。如果調變速率過高(超過200kHz),調變效果可能會因為在下游鎖向迴路(PLL)使用的濾波器環狀頻寬而降低。因此,擁有最理想的調變技術與架構是非常重要的。

除了速率之外,使用調變技術還須考量其他重要因素,如頻寬需求、調變的方式(中心展頻或向下展頻)及諧波抑制程度等。使用展頻技術通常不會對其他系統效能考量因素造成影響,即便產生影響也是非常小的。

緩慢且受控制的調變不會產生短暫的抖動,例如富士通微電子(Fujitsu Microelectronics)的展頻時脈產生器系列元件通常可具備與非展頻時脈相同的低於100微微秒(ps)的週期性時脈抖動。

|

| 圖7 展頻時脈產生器簡化系統設計流程 |

總結來說,相較於被動式EMI抑制技術,展頻時脈產生器的系統特性具備更多主要優勢,例如從源頭大幅降低系統發射出來的電磁干擾、更容易通過美國聯邦通訊委員會的認證,加速產品上市時程、將系統設計步驟大幅度簡化(圖7)、具備可編程的彈性,以編寫出最理想的調變架構,及協助降低電磁干擾測試基礎架構的成本與資源。

展頻時脈產生器顯著降低輻射量

採用展頻時脈產生器可縮短設計週期、降低總體材料清單成本,並可讓產品在毋須犧牲系統效能的情況下,成功通過FCC電磁相容的首關認證。本文接著將以富士通的展頻時脈產生器來說明展頻時脈技術在降低EMI方面所能做出的貢獻,並以行動應用產品做為實際案例,說明導入展頻時脈技術不會對系統產品的效能帶來衝擊。

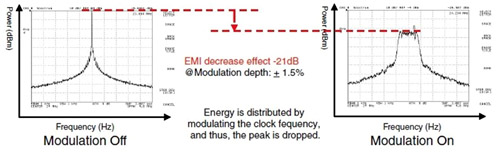

展頻時脈產生器充分發揮數位頻率調變控制技術的優勢,因為此技術具備了多重調變功能。如圖8所示,電磁干擾可降低至21dB,並可抑制基本頻率與諧波。 圖8所示的降低電磁干擾的效果顯示當調變功能在啟動與關閉狀態下的電力與分貝指數比例。以下為此比例的計算公式: 10×LOG10(P1/P2)

|

| 圖8 展頻時脈產生器開啟前後的電磁輻射強度變化 |

當調變功能或關閉時,電磁干擾降低效果為0dB,但開啟調變功能後,由於電場強度比(P1/P2)變成1/150,因此約可帶來-21.76dB的EMI降低效果。

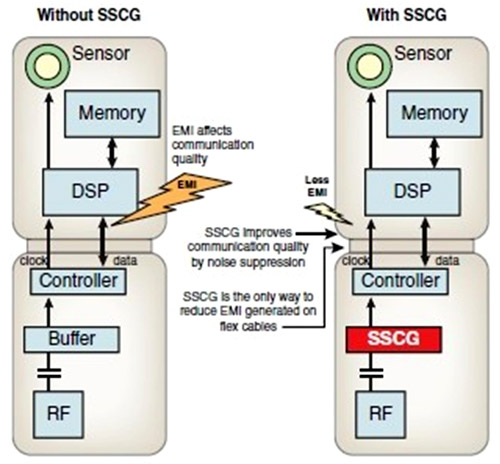

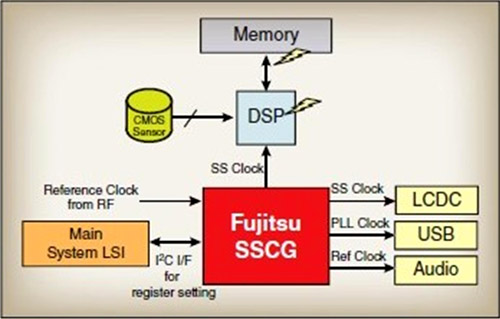

以下範例詳述這些功能在應用上的影響,顯示展頻時脈產生器可使用在手機上,且不會影響其效能。在此範例中(如圖9與圖10所示),主要中央處理器(CPU)、全球衛星定位系統(GPS)與射頻模組均使用多重時脈。手機中電磁干擾的主要來源是控制器、數位訊號處理器(DSP)與記憶體之間的傳輸,以及連結至顯示器的排線所引起的。

|

| 圖9 展頻時脈產生器在手機上的應用範例 |

|

| 圖10 以單一產生器支援多重時脈展頻 |

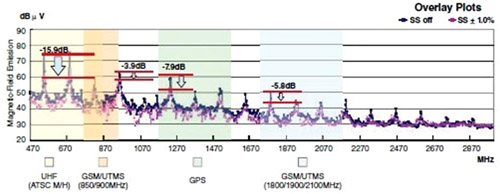

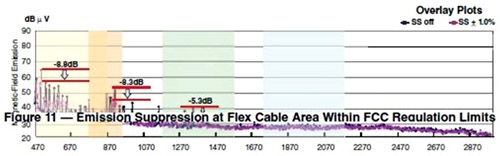

圖11與圖12顯示在主要CPU與排線區域中的輻射抑制是低於美國聯邦通訊委員會的規範限制的。

|

| 圖11 在主要CPU的輻射抑制低於美國聯邦通訊委員會的規範限制 |

|

| 圖12 在排線區域中的輻射抑制低於美國聯邦通訊委員會的規範限制 |

在行動系統設計中內建展頻時脈產生器將大幅降低電磁干擾,並可讓基本頻率與諧波符合美國聯邦通訊委員會規範第十五條的規定。

展頻技術根治EMI惠而不費

總而言之,相較於其他降低電磁干擾的技術,展頻的系統特性具備更多主要優勢,透過系統協助降低電磁干擾。此方法可提升系統效能,並同時抑制電磁干擾。採用展頻時脈產生器可降低封裝、濾波、屏蔽與設計週期的成本。重要的是,使用展頻時脈產生器可加速產品上市時程,但另一方面卻有可能無法通過認證測試。多重時脈輸出、可編程與低週期性抖動產品,可提供一個更具經濟效益的解決方案,讓顧客降低因電磁干擾所帶來的高昂成本問題。

(本文作者任職於富士通微電子)