隨著無線網路用戶快速激增,各種服務不斷推陳出新,而可攜式上網產品日趨平價化,也使市場對於基礎設施容量的要求每天持續攀升。3G智慧型手機、3G聯網迷你筆電及3G聯網平板電腦等產品,對無線數據服務與基地台容量掀起一波爆炸性的需求成長。現有的無線寬頻設備包括增強版高速封包存取(HSPA+)及演進資料最佳化(EVDO)如3G+,這些產品的效能滿足一部分的資料傳輸量需求,但是全球各地的無線服務供應商正不斷地被客戶抱怨服務速度不夠快,尤其是在超大型都會區。

無線電信業者未來將邁向更高頻寬的服務,如長程演進計畫(LTE)與先進長程演進計畫(LTE-Advanced)來因應這方面的挑戰。但是這些4G技術在未來數年陸續問世之際,資料傳輸量的需求還會持續攀升。全球各地的市場都要求桌機等級(Desk-top Class)無線寬頻服務,而且許多產業分析師預測未來6年這種情況就會出現,因此無線服務供應商被迫同時提高基地台的密度。為因應此種情況,業者必須大幅增加基礎設施設備的安裝數量,再加上高度競爭的區域市場,將對基地台原始設備製造商(OEM)形成日趨沉重的壓力。

分散化部署降低BOM成本

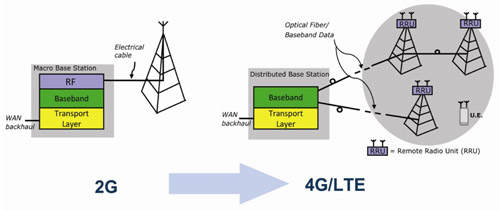

從以往的歷史來看,電信業中更高的基地台接收站(BTS)效能通常會增加耗電量,並造成更高的總持有成本(Total Cost of Ownership)。然而展望未來,這些趨勢將會有所改變。亞洲與非洲地區的3G及與性能強化的3G設備,將形成降低售價與功耗的壓力,這些影響將逐漸擴散至整個無線基礎設施市場。對於無線基礎設施OEM而言,維持與提高獲利能力的關鍵,在於降低基地台的物料清單(BOM)成本。降低BOM成本其中的一種方法,就是從傳統單機式的基地台部署模式轉移至分散化的模式(圖1)。

|

| 圖1 基地台網路的演進 |

這種架構能克服上述的部分挑戰,並促使業界採納串列器-解串列器(SERDES)邏輯元件及此類元件的成熟化,以支援遠端無線射頻單元(RRU)與BTS間的光學資料傳輸。然而,無線射頻單元在整體BTS的BOM成本中仍占有相當大的比例,因為它們含有射頻與資料轉換設備。

新型的低成本、低功耗現場可編程閘陣列(FPGA)如LatticeECP3元件,就能降低整體無線射頻單元的成本,因為其提供彈性化的資料處理功能,並可透過整合式SERDES來支援通用公共射頻介面(CPRI)與開放式基地台架構組織(OBSAI)基頻介面。

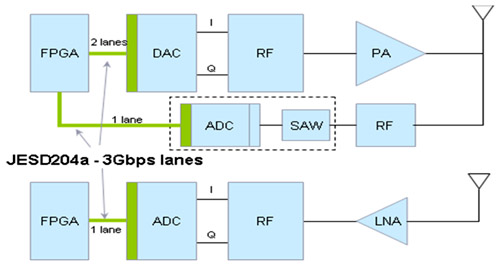

不過,對於資料傳輸量要求的提升,促使傳統平行資料轉換器(Data Converter)介面在效能、印刷電路板(PCB)布局的複雜度與製造成本,以及維持資料完整性等方面均逼近其極限。這些挑戰導致SERDES的功能從BTS介面轉移至數位資料/控制介面,而此類介面連結實際的RRU資料轉換器與資料處理FPGA如圖2所示。

|

| 圖2 JESD204A介面 |

由工程設計發展聯合協會(JEDEC)JC-16委員會提出的這種新介面,已在2008年成為一項開放性的業界標準,名為JESD204A,在降低無線射頻單元的零組件成本方面,擁有極大的潛力。

現已整合至恩智浦(NXP)CGVTM資料轉換器內的JESD204A,是一種高速的序列介面,採用電流模式邏輯(CML)相容的差動訊號搭配8B/10B編碼機制。目前最高的資料傳輸率為3.125Gbit/s,每個通道頻寬為312.5MB/s,資料轉換器與FPGA間的多重通道設計,讓系統頻寬得以隨意複用。由於JESD204A支援精準的跨通道同步化,所以能夠在原生模式下支援正交採樣,這也是各種3G與4G傳輸介面中正交分頻多工(OFDM)調變機制的基礎技術。

JESD204A實現低功耗高容量

邏輯可編程性及高速資料轉換,在基地台設計的流量演進方面扮演關鍵性的角色。資料轉換器在射頻功率放大,以及無線電單元中射頻訊號的元件間擔任橋接的任務,而FPGA則提供充裕的彈性,讓業者能在無線傳輸介面規格完全底定前便著手展開設計。

對於基地台資料傳輸量持續攀升的要求,促使無線射頻單元零件的成本與功耗逐漸提高,印刷電路板與介面日趨複雜,也使得訊號完整性的問題更加嚴重。

JESD204A帶來的利益包括降低BOM成本,以及為資料轉換元件樹立其他商業與技術的標準,這些效益讓BTS原始設備製造商無法忽視此一突破性的新介面選項。所省下的BOM成本,以及提高系統可靠性所省下的成本,很快地便會超越採納新技術所耗費的成本。

簡化PCB設計 協助降低功耗

JEDEC JESD204A能大幅簡化PCB布局,有效降低無線射頻單元的BOM成本,這方面的簡化讓業者有機會減少PCB電路的層數與尺寸,而這兩者都是影響成本的重要因素。

此外,由於JESD204A大幅減少資料轉換器與FPGA間介面訊號的數量,所以整體系統的可靠度也得以提高。透過低電壓擺幅CML協助降低功耗,讓業者能夠降低電源供應器的BOM成本。

除了降低零組件成本的利益外,JESD204A還帶來許多系統架構方面的效益。強大但不會耗用軟體資源的嵌入式通訊協定,包括資料擾碼、偵測單一位元錯誤、偵測鏈路同步損耗、提升無線電PCB中類比與數位區域的隔離效果,以及提高雜訊免疫力等。許多產業觀察人士認為資料轉換器介面轉移至JESD204A是不可避免的趨勢,就如同個人電腦(PC)與數位訊號處理器(DSP)硬體轉移至通用序列匯流排(USB)、PCI Express及Serial RapidIO高速序列傳輸技術。

就資料轉換元件而言,成本、功耗及效能等方面的要求,促使FPGA架構經歷許多革命性的改變,使其能大幅提高效能、功能及邏輯密度。低成本FPGA在彈性、上市時程等方面明顯勝過特定應用積體電路(ASIC),這些優勢眾所周知,但FPGA的應用範疇以往一直局限於黏裝電路(Glue Logic)與修正錯誤(Bug Fix)等領域。

未來,這種局勢將會被打破,FPGA的價值主張已大幅提升。例如,市面上全新系列的低成本、低功耗FPGA已針對許多功能進行強化,如整合式SERDES、DSP資料通道及嵌入式記憶體功能,這些元件已成為眾多無線射頻單元的關鍵零件。系統與設計工程師將能運用這些可編程平台來開發複雜的訊號通道應用,進而著手建置如數位降頻(DDC)、數位升頻(DUC)、峰值因素衰減(CFR)及數位預失真(DPD)等各種功能,且功耗與價位僅是其他SERDES型FPGA產品的一半。

可擴充JESD204A勢成主流

BTS原始設備製造商除應審慎評估無線射頻單元的零組件成本,也應在其他方面可能節省的成本納入考量,而運用新推出的JESD204A高速序列介面來作為重要選項,將可因應無線基礎設施設備在售價方面持續承受的降價壓力。

對於無線電單元的設計而言,FPGA與資料轉換器一向扮演著關鍵性的角色,如今,它們將達到更上一層樓的效能,並協助降低系統的建構成本。以SERDES打造的可擴充JESD204A介面,提供一個無縫接合、簡化、低功耗且低成本的資料高速通道,以用來連結類比數位轉換器(ADC)/數位類比轉換器(DAC)與FPGA。多功能、低成本的FPGA帶來更快速的上市與獲利時程,加上充裕的彈性,將讓業者可透過低廉的成本來支援持續演進的標準。現在,系統設計工程師將可運用現有的改良工具,在不斷演進的寬頻無線市場中克服種種挑戰。

(本文作者依序為萊迪思歐洲區FPGA行銷經理、恩智浦高速轉換器產品線經理)