隨著類比數位轉換器(ADC)藉由更小的製程節點而在設計與架構上持續進步,新類型的GHz ADC產品也開始興起。其能夠以GHz與更高速率直接進行射頻(RF)取樣(沒有假插入訊號),為通訊系統、儀器以及雷達應用的直接射頻數位化所需要的系統,提供了新的解決方案。

在以往,這些解決方案需要多個濾波級、合成器與混頻器,藉以將ADC輸入訊號轉換成能夠在100MSPS範圍內加以數位化的參考頻率。現在,直接射頻取樣可以透過寬廣頻段的ADC技術來加以實現。

不久之前,能夠以GSPS(每秒千兆取樣)速度運作的唯一單晶片ADC架構是具有6b或8b解析度的快閃記憶體轉換器。它們的用電需求很高,而且因為其快閃架構對於幾何尺寸與功率限制上的權衡,所以通常無法提供超過7b以上的有效位元數(ENOB)。

唯一能夠對超過1GHz這類更高動態範圍類比輸入訊號進行取樣的方法,就是加入多組具備取樣時脈的高速ADC核心,才能夠以精密的精確度或是工作週期對每組核心提供交錯相位。必須被加以分割與混合到每組ADC當中的類比輸入,都會為新的訊號雜訊提供進入訊號鏈的機會,並且降低輸入功率。雖然這種方法可能會為某些應用裝置提供適當的結果,但是設計相當複雜,而且會在輸出頻率域中製造出難以處理、無法預期的非自然插入訊號,而必須以數位方式加以過濾。

架構/演算法大翻新 迴避插入突波問題

插入的突波能夠在快速傅立葉轉換(FFT)的頻率響應中被觀察到;亦即輸入偏移、增益、頻寬以及取樣時序都沒有與每組內部交錯式ADC核心完全匹配的位置。這會對系統工程師在預先判定非自然插入訊號會在頻率的何處出現,在數位後處理予以避免或將其移除時造成額外的計畫複雜度。由於每組ADC核心都是獨立的,所以在一個正在量產的系統生命週期當中,這些性能參數會有很大的潛在機率於製造時形成不匹配差異。而這些不匹配會在進入訊號的週期內造成不平衡,並且使寄生頻率出現在交錯式ADC的輸出當中。

目前已有廠商開發出新的ADC技術,能夠得益於先進的架構與演算法,進而避免在雙通道與四通道交錯式ADC所會出現的問題。取代傳統須要使用兩組以一半速度運作的交錯式ADC。例如亞德諾(ADI)即是透過增加的假訊號,使用全速運作的單一ADC就能夠實現所需要的性能,不會有插入突波。另外,工廠修整演算法以及晶片內建的校正功能,可以確保每組ADC以所預期的高性能標準運作,不會再出現使用多重離散交錯式核心時所產生的不匹配差異。

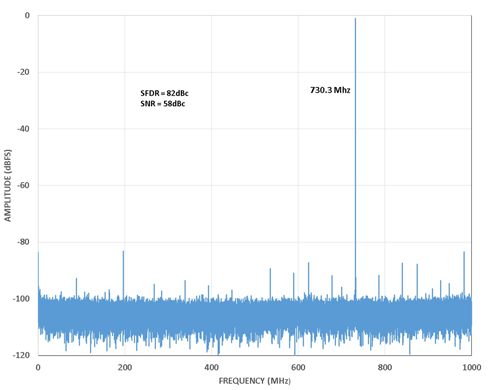

當寄生頻率透過快速傅立葉轉換,在原本純淨的頻譜當中被觀察到時,這會降低載波訊號相對於其他雜訊的既有無寄生動態範圍(SFDR)(圖1)。為了要改善GSPS ADC的SFDR,現在已經有新的架構和演算法出現,並且取代了交錯式核心的使用。這將使得系統工程師省去進行專注於ADC後處理時,必須辨別與移除不需要之插入突波等例行程序的重擔。

|

| 圖1 寬頻2.0 GSPS ADC的快速傅立葉轉換,顯示沒有插入假訊號的高性能SFDR。在高速ADC中,此種情況一直造成問題。 |

採用JESD204B 簡化例行程序

具有10b、12b或是14b解析度的多重千兆取樣轉換器能夠產生大量的輸出資料,而且是以很快的速度來達成。要使用低電壓差動訊號(LVDS)傳輸資料,可能需要二十組適用於2 GSPS ADC的1Gbit/s資料的並聯線道。要處理每個ADC的二十組差動LVDS配對,對於在系統布局中的路由與維持匹配長度而言是一項相當大的挑戰。使用JESD204B--一種高速串列器/解串列器(SerDes)的標準,等量的資料能夠只使用六或八組差動線道進行傳送。

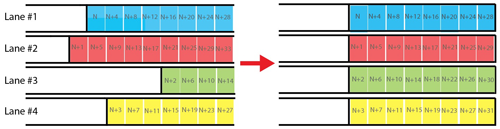

JESD204B以較少資料線提供高速輸出資料,因此沒有許多高速LVDS線道會出現的匹配型時序板複雜度。由於以JESD204B傳送的資料會依據嵌入式時脈與控制特性而被加以框架,因此較低數量的串列線道的路由會比LVDS具有更加寬容的時序歪斜(圖2)。如此便不須要再花費無數個小時在每一組系統印刷電路板(PCB)的輸入輸出(I/O)上調整時序。

|

| 圖2 JESD204B框架通訊協定允許資料線道之間以及PCB路由內的顯著時序歪斜。FPGA能夠藉由內部緩衝器延遲使資料與取樣重新對齊。 |

此外,JESD204B提供了在輔助資料中具有資訊的「控制位元」,可以附加到每一個類比取樣中以便讓下游處理的特性更明顯。透過這種方式,觸發時間戳記與過範圍狀況可以在每個取樣中被標示出來,如此後端現場可編程閘陣列(FPGA)就能夠獲得有關於資料對齊以及其有效性的進一步情報。

過範圍偵測 縮短反饋時間

自適應增益演算法對於能夠調整類比輸入訊號的振幅來說相當重要,因為飽和的ADC輸入基本上會使系統解譯訊號的能力喪失。在理想狀態下,增益自適應回授迴路應該要越快越好。無論高速ADC輸出是以LVDS為基礎或是使用JESD204B,這種數位輸出的附加延遲往往會為了要接收飽和資料、偵測問題以及對狀況做出反應,以致於太長而無法等待。

對於這種問題有一個解決方案,那就是能夠利用ADC核心本身內部的可變位準比較,以及在過範圍狀況發生時直接傳送一組立即輸出旗標。這種技術會將較長後端輸出級的延遲避開,以便縮短對於放大器的反饋時間,進而實現更快速的自適應增益週期。除了這種「快速過範圍偵測」輸出外,使用JESD204B,過範圍取樣也可以加入警示位元,讓下游系統處理更能對資料做出適當的決定。

重要三步驟:調整、濾波、消除

寬廣頻段ADC能夠提供寬頻取樣的優點,但是可能也會提供比某些應用裝置實際所需還要更多的資料。對於那些需要高取樣速率,但是不必觀察大型頻譜的系統,數位降頻轉換(DDC)允許子取樣(Sub-sampling)以及濾波策略,用以消除由GSPS ADC輸出的資料量。接著,下游處理會觀察較小部分的頻譜。

雖然在訊號鏈中,DDC通常會在ADC之後執行,但是這不僅會消耗更多FPGA當中的資源,同時也須要使用完整頻寬在ADC與FPGA之間進行傳輸。除了傳輸與處理在FPGA中的取樣資料外,DDC濾波功能也可以在ADC內完成,而且只需要八分之一或四分之一的總頻寬。

在與合成的數值控制振盪器(NCO)結合使用時,頻段中轉換器DDC濾波器的精密位置能夠以精確的解析度加以調整。如此將能夠容許較低的輸出速率,而且不須要在FPGA中移動與處理大量的非所需資料。當有兩組DDC可以使用時且每組都有獨立的NCO,它們可以在整個頻譜中交互步進,以便針對預期的訊號進行清除,而不會喪失可見性。在某些雷達應用裝置中,這可能是一種典型的使用方式。

以亞德諾最近才發表的12b、2.0 GSPS ADC--AD 9625為例,可提供在廣大頻寬中優於-75dBC的SFDR性能,其專屬的技術能夠在沒有假插入訊號(通常會出現在以高於1.5 GSPS進行取樣的GHz ADC當中)的情況下實現這種性能。而具有寬廣波段頻率調諧器的可選式雙重消除降頻轉換濾波路徑,讓系統設計者能夠觀察到完整頻譜頻寬的八分之一或四分之一寬度,而且每個都具有獨立的10位元NCO位置解析度。

(本文作者為亞德諾特約技術專家)