用於第五代行動通訊(5G)智慧型手機與網路的系統單晶片(SoC)和射頻積體電路(RFIC)皆須管理大量的天線數據,並在熱和功率受限的環境中提供高度處理能力。多物理場模擬可同時解決晶片、封裝和系統範圍內的功率、熱、可變性、時序、電磁和可靠性之各項挑戰,讓矽晶與系統得以一舉成功。

半導體現況發展

5G使SoC的設計更加複雜,這些SoC用來推動5G智慧型手機/用戶設備(UE)和無線接取網路(RAN)/網路基礎設施元件。5G基地台和手機晶片組應可支援智慧波束成形和波束追蹤/轉向功能,以增加毫米波(mmWave)的覆蓋範圍並將干擾降至最低。具有自動波束成形功能的複雜三維(3D)天線陣列可用於大規模多重輸入多重輸出(MIMO)天線,然而卻會消耗大量功率(80瓦以上)。這些元件與其他敏感的類比和射頻(RF)電路相結合,組成射頻前端組件,提供完整整合的毫米波射頻解決方案。

目前共有類比、數位與混合架構等三種波束成形架構,在功率、複雜性和容量方面,三種架構各有其優缺點。例如,與類比和混合架構相比,數位架構的波束成形具備最高容量與靈活性,但功耗也相對較高。

此外,5G基頻晶片、波束成形模組與SoC皆需先進、基於性能的製程節點,如介於FinFET 14奈米(nm)~7奈米(或更低)且低功耗的絕緣體上矽薄膜(SOI),且同時具備先進的封裝技術。在進行這些設計時,設計餘量低,製程進度的壓力更大,且成本更高。16奈米以下的設計內含多物理場效應,如時序、功率、電磁學、熱學和可靠性,彼此之依存性與日俱增,使得設計收斂面臨更大的挑戰。 傳統的以設計餘量為基準、孤島式的設計方法不易產出最佳的設計。這些解決方案的模擬覆蓋範圍有限,無法發現潛在的設計弱點,從而導致實際應用時發生故障。本文將深入探討SoC和智慧財產權(IP)設計的早期電源效率、電源完整性、可靠性、進階封裝和串擾分析需求。

早期功率分析

各界期待4G轉移至5G後能提供更高之細胞邊緣(Cell Edge)資料傳輸率,從10Mbit/s提升至1Gbit/s以上,同時帶來50%之能源效率增益。從3G、3.5G、4G到現在的5G,峰值對平均功率比(Peak-to-Average Power Ratio, PAPR)一直持續增加。

對於持續發展的5G設計開發,重點在於,在晶片設計階段的早期就能預測電源配置(Power Profiling),尤其是以下重點領域,包括頻譜相關議題、流量屬性、射頻干擾與互通性、網路存取相關議題。

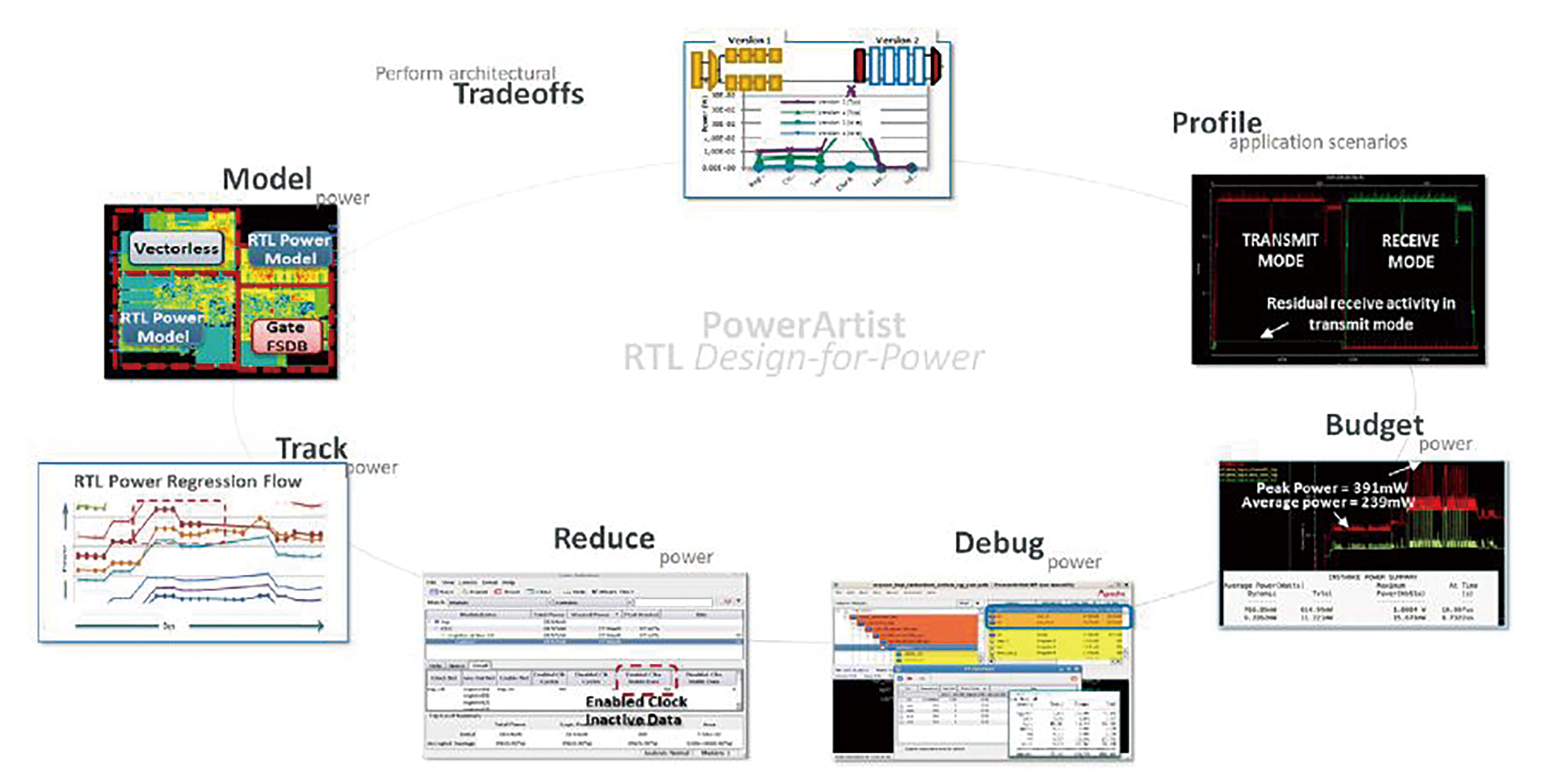

5G裝置的關鍵設計考量就是電源效率。平均功率、峰值功率、功率峰值變化與持續最糟情況之平均功率對於5G系統的熱穩定性、電源完整性與運作成本都很重要。早期反饋是達成5G功率目標的關鍵。如廠商Ansys的PowerArtist可協助設計人員在暫存器傳送層級(Register-Transfer Level, RTL)設計階段初期即處理功率,為5G應用打造高效率產品。

PowerArtist藉由模擬時脈樹(Clock Tree)、導線電容(Wire Capacitance)與多位元正反器(Multibit Flops)之物理效應,提供經過7/5奈米驗證、RTL跟邏輯閘層次(Gate-Level)功耗的誤差在15%以內。來回時間較傳統Gate-Level工法快20倍。這個做法讓設計人員能儘早並可靠地識別並做出功率決策。PowerArtist可揭示降低功率的各種機會,例如透過RTL技術之階層式時脈閘控(Hierarchical Clock Gating)與強大之互動式除錯以及功率效率指標,可節能高達70%。

PowerArtist亦可加速電源分析,較傳統區間式(Interval-Based)功率分析工法快上數倍。這種快速的分析方式將分析時間從數週縮短至數小時,促進識別出可能造成過度壓降與潛在時序失效(Timing Failure)之關鍵峰值功率與較大之電流瞬態(di/dt)循環(Current Transient (di/dt) Cycles)。關鍵循環選擇的重要性不只是針對降低功率,還包括保護晶片不受設計缺陷所影響,設計缺陷是因為未偵測到的情境,以致影響了在晶片、封裝與系統方面之健全的功率與散熱規畫(圖1)。

圖1 PowerArtist功能示意圖

圖1 PowerArtist功能示意圖

想像手機使用者的例子,在快速移動的火車上使用Gbps資料傳輸率,遇到基地台換手。切換基地台會導致功率的大型階躍函數(Step Functions),因為新的基地台在建立連線,開始服務大量使用者,同時前一個基地台釋出連線。5G系統必須提供不到1毫秒(ms)的低延遲來服務這種需求。透過快速之電源分析與模擬器之高效率活動轉移工作流(Activity Transfer Flows),PowerArtist可針對數百萬甚至數十億活動週期產生每單位週期之電源分析。這使得在RTL早期進行分析得以實現,在該階段依然能做出有意義、具高影響力的設計更動。

5G SoC之電源完整性

SoC若用傳統之電網簽核(Power Grid Signoff)是行不通,因為嚴格的布線限制可能造成下游之時序收斂(Timing Convergence)問題。先進FinFET技術製程之電網節點數極高,任何節點數的減少都會影響精準度。

在設計餘量極低的情況下,電源簽核(Power Signoff)方案的容錯空間極小,稍不精確會導致產品失效。因此重點要分析整體電網,而非採用分治法(Divide and Conquer)來分割設計。SeaScape大數據技術為上萬核心實現穩定度,在通用硬體上簽核十幾億實例設計僅需數小時。各種模擬模式,包括RTL與閘道向量(Gate Vectors)、功能模式與掃描模式之智慧型無向量分析(Smart Vectorless Analysis)、混合模式模擬如無向量加上VCD(Value Change Dump), 以及功率瞬態(Power-Transient)與通電(Power-Up)分析,可提高電源完整性簽核的設計覆蓋面。

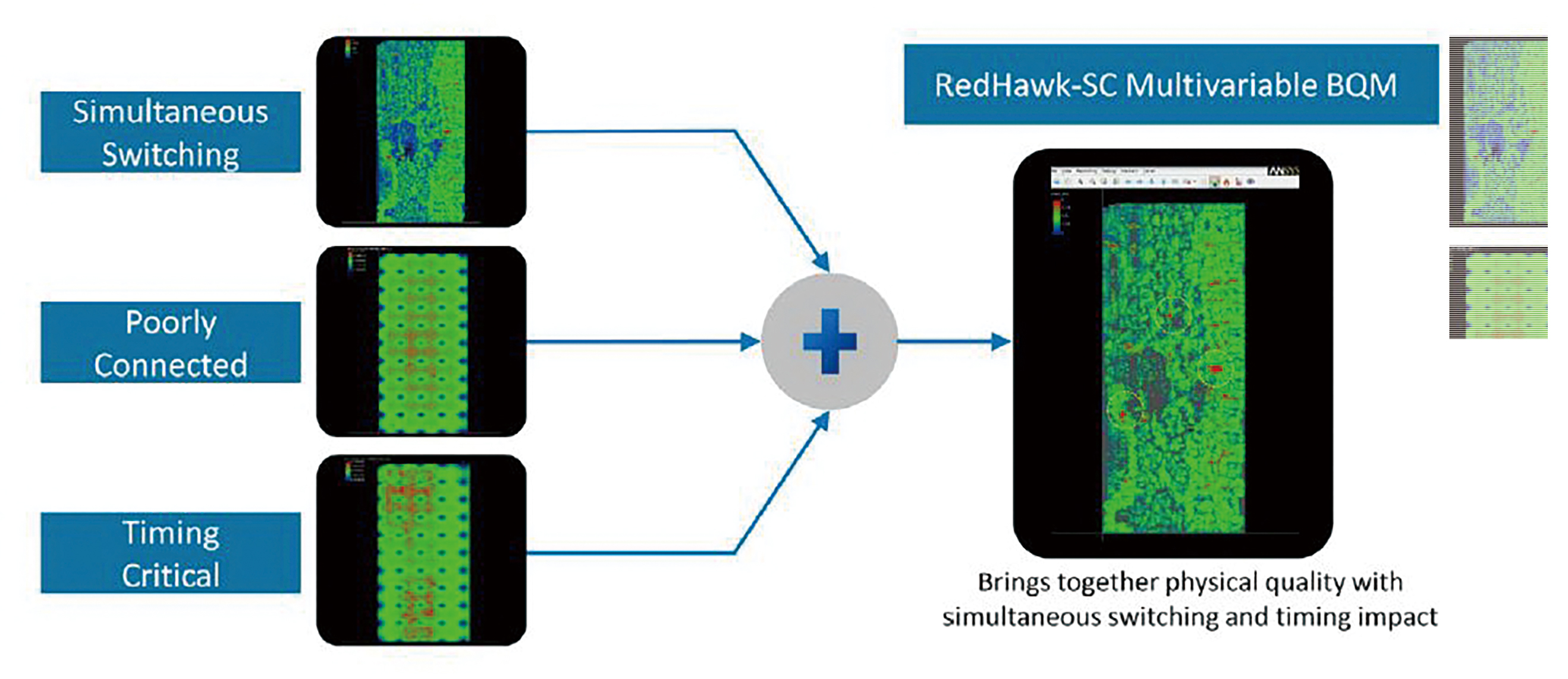

此外,資料分析工具能為設計弱點提供有用之洞見。客製化分析工具可打造獨特之量表,根據物理、電學與其他模擬參數來呈現設計品質。例如,修正通過高動態壓降區之低時序餘量路徑(Low Timing Slack Paths)需要知道所有時序路徑與所有壓降情境的相關資訊。透過這些分析工具進行目標鎖定式的設計修正,在7奈米可以更高效的方式來排序與修錯。

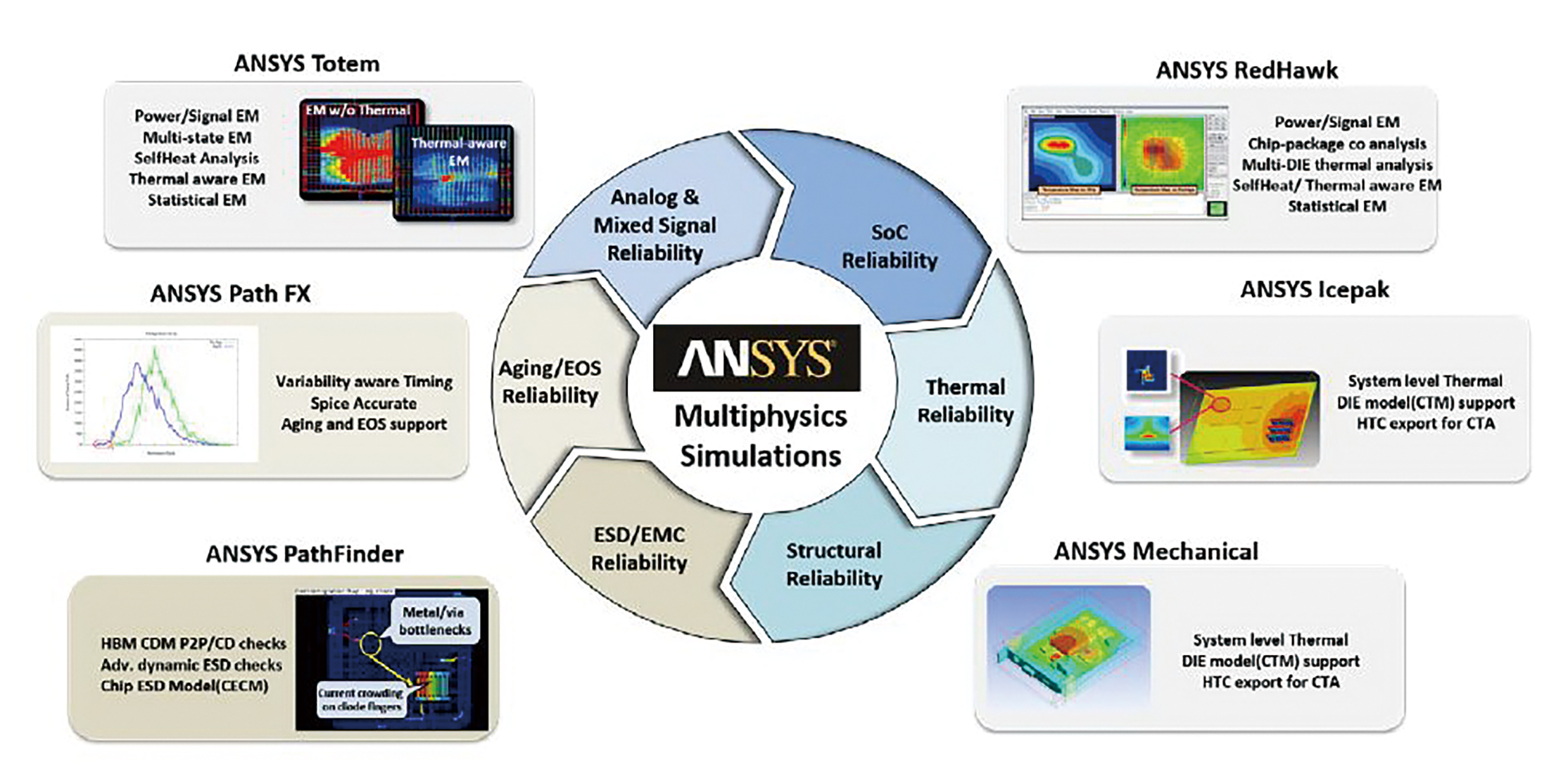

處理SoC之可靠度

5G通訊系統裡使用之先進SoC的關鍵考量之一就是可靠性設計。這些SoC將促成未來任務關鍵型應用,例如自駕車。實現先進FinFET節點裡的可靠度有時極具挑戰。FinFET設計之動態功率密度極高,而功率會直接影響晶片的熱特徵(Thermal Signature)。在整體系統環境裡考慮晶片,並據此針對晶片上之溫度分布精確建模,是確保晶片能可靠運作的關鍵。高溫、更薄的互聯都把晶片上的電遷移失效(Electromigration Failures)推到極限。散熱議題很重要,因為在先進FinFET技術節點裡,自我加熱效應與焦耳熱效應可使局部溫度上升10°C以上。會發生這種情況是因為低介電係數的周圍材料無法有效散熱至矽基板(Silicon Substrate),因此熱能卡在線路與裝置內。過高之Delta-T可能導致晶片互聯/裝置層電磁(Electromigration, EM)失效。需要投入額外工作來量化線路與裝置之上升溫度。RedHawk與Totem提供完整支援來進行具熱感知能力之功率、接地與訊號線路(Power/Ground and Signal Line)EM驗證。這些方案可精準分析EM違規,同時為先進FinFET設計將誤判降至最低。

使用具有熱感知能力的EM方案為自熱效應(Self-Heat Effects)與晶粒之整體接面溫度變化來建模,是實現精準簽核工法之必要條件(圖2)。

圖2 RedHawk-SC構建質量指標(BQM)的多變量分析

圖2 RedHawk-SC構建質量指標(BQM)的多變量分析

此外,統計電子遷移預算(Statistical Electromigration Budgeting, SEB)將簽核最重要之EM修正排在優先,同時避免過度設計,藉此讓晶片設計人員符合嚴格的安全與可靠度要求。

設計人員可大幅得力於SEB建模法,僅須修正影響產品可靠度最關鍵之EM違反即可。這種做法能將可靠度簽核所需時間從數月降至數週,加速設計收斂。RedHawk與Totem自加熱與晶片封裝熱共同分析解決方案在所有主要晶圓廠的先進FinFET技術節點(N16與以下)都有支援。

隨著SoC大量使用IP與高速介面,靜電放電(Electrostatic Discharge, ESD)之設計與驗證變得極為困難。ESD檢查現在是簽核的關鍵項目之一。近55%的失效都與互聯有關,可在設計階段進行全系統ESD檢查以避免失效。在IP層級能成功之ESD保護到了SoC層級不見得能成功,因為與SoC之其他IP與電路連結不良。因此,重點是要在SoC層級跨多個電壓區域分析ESD保護方案,確保能提供想要之低阻路徑來釋放潛在之ESD事件,而不使功能裝置過勞。

PathFinder能實現完全分散式機器處理,為數十億Instance設計達成全晶片ESD簽核。PathFinder Explorer提供以圖形使用者介面(GUI)為介面之互動式除錯功能,促進快速之設計探索與資料探勘,取得設計問題之關鍵洞察力,排序設計修錯。動態ESD分析現支援FinFET設計。PathFinder可為系統層級之ESD/電磁相容性(Electromagnetic Compatibility, EMC)模擬產生晶片ESD精簡模型(CECM)。

元件老化是另一個影響可靠度的議題,放在電信塔的基頻晶片須可靠運轉數年的時間。老化是指晶片隨時間衰變。橫跨電晶體閘道之電場緩慢使裝置之電介質衰變。

主要物理效應為偏壓溫度不穩定性(Bias Temperature Instability, BTI)與熱載子注入(Hot Carrier Injection, HCI)。就電學而言,其呈現方式為臨界電壓(Threshold Voltage)轉移,導致驅動電流(Drive Currents)隨時間降低,進一步導致更多延遲,最終造成時序故障(Timing Failures)。

老化效應通常於晶片生產後數年發生,一般以個別電晶體性能慢速衰變呈現。有些電晶體衰變顯著,而其他類似的電晶體則不受影響。老化現象對使用模式非常敏感。一般設計方式,例如時脈閘控(Clock Gating)可能會使老化問題惡化。Ansys Path FX為先進設計提供裝置老化模擬功能(圖3)。

圖3 ANSYS多物理場可靠性解決方案

圖3 ANSYS多物理場可靠性解決方案

先進封裝挑戰

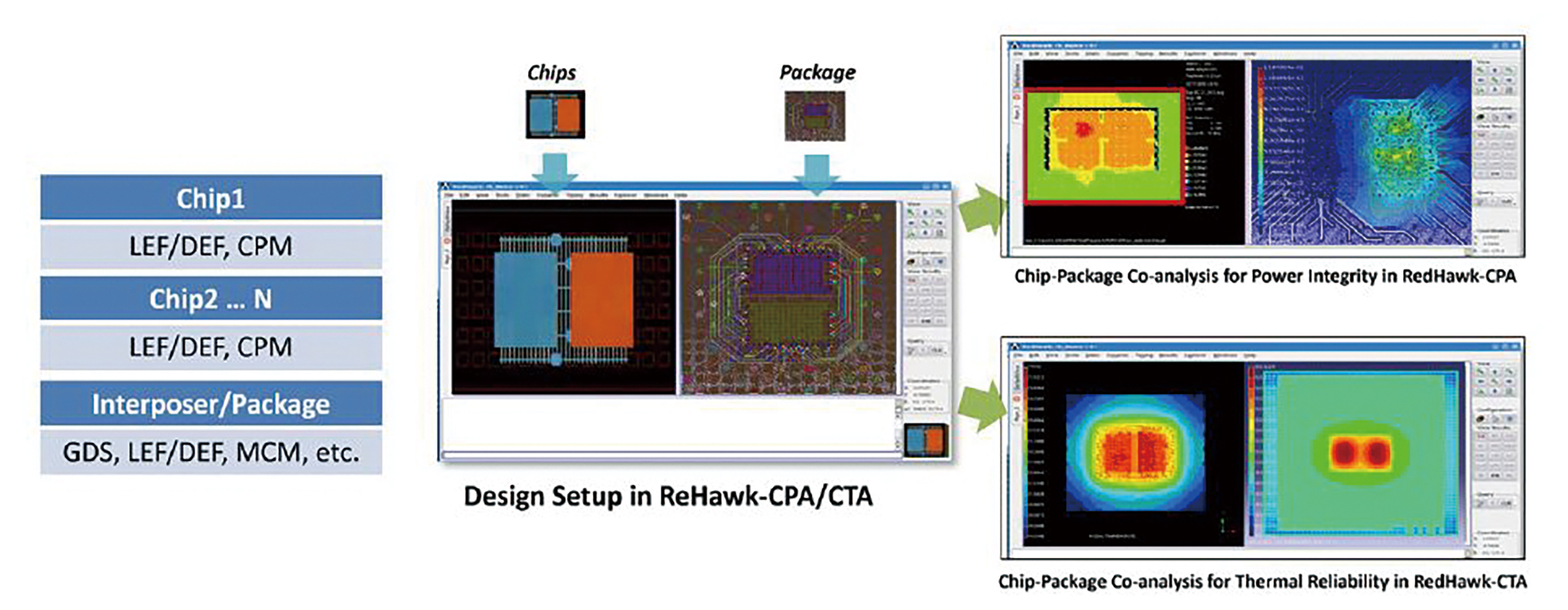

先進封裝技術將是推動下一代邊緣運算資料中心與5G電子系統異質整合的主力,實現極致效能、高系統頻寬、低功耗與低成本。5G基礎架構促成之萬物聯網將產生需要處理並儲存之巨量資料。處理巨量資料的能力會受限於傳統封裝之處理器與整合於系統中之記憶體間有限的系統頻寬。

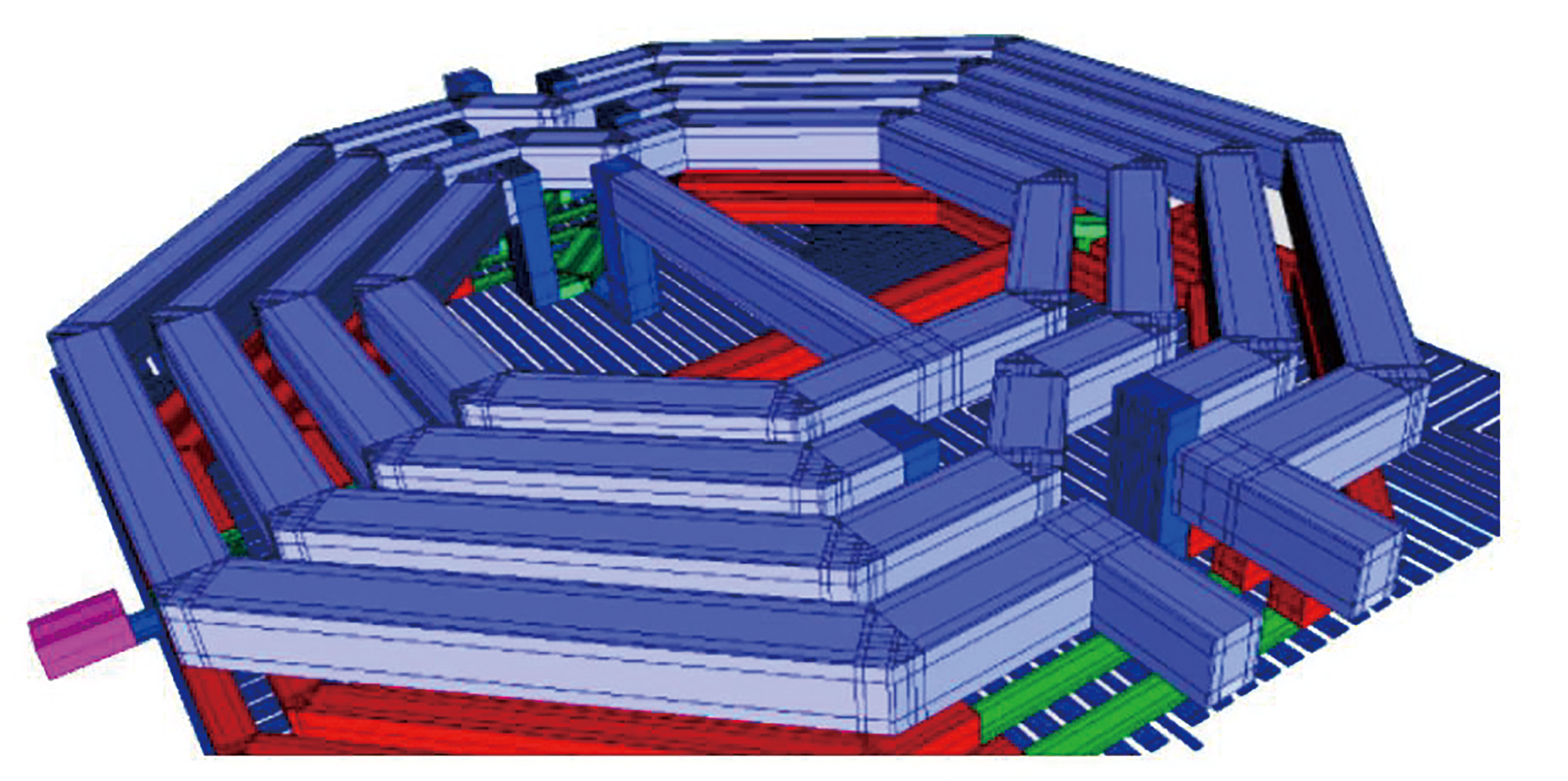

因此,先進之2.5DIC/3DIC封裝技術將成為5G系統設計的常用選項(圖4),這些技術包括:矽穿孔(Through Silicon Vias, TSVs)、晶粒與晶圓堆疊(Die and Wafer Stacking)、系統單封裝(System-in-package, SiP)、層疊式封裝(Package-on Package, PoP)、先進晶圓級封裝(Advanced Wafer-level Packages, WLP)與利用第三維擴充之中介層整合(Interposer Integration)。TSV可實現堆疊晶片間較短的連接通道,達成更高的效能,因為I/O速度得以提高。其功耗亦較低,因為電容降低,且多晶粒堆疊的尺寸較小。這的確是非常有前景的技術,只是因為複雜度而充滿挑戰性。

圖4 用於晶片級功率/熱完整性分析的2.5DIC/3DIC技術

圖4 用於晶片級功率/熱完整性分析的2.5DIC/3DIC技術

毫米波射頻解決方案之基板雜訊分析

整合高功率波束成形模組與敏感之類比與RF電路會導致基板雜訊(Substrate Noise)從波束成形模組波及類比/RF電路,或從類比/RF電路波及波束成形模組,進而影響整體效能。為實現精準之電源雜訊分析,設計人員必須能在DvD分析中針對基板雜訊建模。整合數位波束成形模組與構成RF前端模組之敏感的類比與RF電路,若未保障足夠之隔絕,可能會造成開關雜訊(Switching Noise)透過基板增生。

為實現毫米波RF模組可靠的運作,工法必須能為基板雜訊建模,該雜訊則是透過數位雜訊注入(Digital Noise Injection)於數位波束成形模組中產生。此工法亦須進行分析,以判定類比/RF區塊之頻率與時域反應(Time-Domain Response)。針對特定技術節點須採取正確之隔絕技術,必須在設計週期早期,利用測試架構規畫隔絕架構,例如p保護環(Guard Ring)、深層n型井(Deep n-well Tub)、深層n型井(Deep n-well)保護環等,以避免後期簽核階段有任何意外。

基板雜訊分析需要真正之混合式訊號電源雜訊與可靠度分析方案。Totem是一款混合訊號EM/IR工具,且有基板雜訊分析晶圓廠簽核的實績,有助評估雜訊對時序、頻域分析與保護環品質的影響,促成更快速之簽核收斂。

RFIC與SoC設計之電磁分析

針對5G,RF前端電路、高效振盪器與相關互聯必須設計適當,確保6GHz(與以上)至毫米波頻率之可靠運作。晶片上的混合訊號元件會受電磁效應影響,其設計考量應包括各個敏感之混合訊號電路區塊間之自耦合與交叉耦合。仔細檢查布局、寄生電感(Parasitic Inductance)與電容、基板建模與跟蹤電阻(Trace Resistance)是達成可靠度的關鍵。

從DC至毫米波頻率進行電磁效應建模需要布局的特殊處理(圖5)。Ansys HFSS是有限元素法(Finite Element Method, FEM)提取器,有經驗的工程師仰賴它進行技術探索與簽核驗證。

圖5 電磁效應建模需要布局的特殊處理

圖5 電磁效應建模需要布局的特殊處理

透過Ansys併購Helic所取得之新工具,讓工程師可打造晶片上元件之可擴充模型,例如電容與電感。在這些工具中,有一個新的、全3D網格演算法(Meshing Algorithm)可分割導體容積,使之適用於電容、電感與電阻之精確建模。在網格演算步驟前,引擎會計算所有的布局效應(Layout Dependent Effects, LDE)。除了LDE外,使用者可精準針對以下建模並定性:電源/接地網路(Power/Ground Nets)、打線接合/凸塊基板(Bond/Bump Pads)、去耦電容(Decoupling Capacitors)、密封環(Seal Rings)、金屬填充(Metal Fill)、封裝層(Package Layers)與螺旋電感(Spiral Inductors)。

電容抽取的方法根據隨機走步(Random Walk)理論,使用細緻之隨機取樣(Stochastic Sampling)演算法,計算高斯面之電場與任意形狀導體之間對應之耦合電容。透過隨機取樣與精密之多層格林函數(Multilayer Green's Function)之數值解(Numerical Solution),可算出高精準度之分散式3D電場。此方法不使用任何模式匹配查找表或平均算法,亦沒有導體離散(Conductor Discretization)瓶頸。這些解法提供最佳運算效率,因為隨機走步本身就是並行且極度高速之演算法。

這個獨特之抽取引擎(Extraction Engine)利用分散式RC網路來模擬基板之耦合效應。隨機之Monte Carlo工法與基板模型可快速且精確地抽取分散式RC基板網路。

此方法採用隨機走步演算法,透過適當之格林函數為多基板層定性,而不需3D離散。電容與基板建模算法的並行屬性提供絕佳之擴充性,並降低抽取次數。

針對電感與電阻建模,Ansys晶片上電磁(EM)方案結合全波EM建模引擎的精準度與SPICE網表輸出(Netlist Output)的彈性。被抽取之模型完整捕捉從DC至毫米波頻率之電感與電阻之行為。這些方案可捕捉所有的電磁現象,包括電流分布、集膚效應和鄰近效應(Skin and Proximity Effects),且高度精確,可調節電磁串擾(Electromagnetic Crosstalk)、被誘發性能衰變與高速、低功耗系統單晶片設計失效的風險。

綜上所述,5G轉型備受期待,但不可等閒視之,因為系統各元素的複雜度極高,藉由完整的設計方案,方可涵蓋SoC、行動終端裝置至網路等之需求。

(本文由Ansys提供)