現今各種日常物件日趨智慧化與聯網化,這些智慧物件不僅改變所有人生活與工作的方式,也扭轉嵌入式市場的面貌,未來安全防護將成為關鍵的要求。在聯網功能外,還須搭配防護與裝置管理,這也導致嵌入式韌體的複雜化。

(本文作者任職於ARM)雖然已有許多廠商針對現今這些需求推出解決方案,但業界至今還沒有定出一個共同標準,以致解決方案無法像擁有生態體系那樣地蓬勃發展,業者因為擔心被特定開發廠商綁死,以致市場規模難以拓展。

在過去十年,安謀國際(ARM)與所有夥伴聯手,以Cortex-M系列的32位元嵌入式處理器為主軸,發展出蓬勃的生態體系。截至目前為止,ARM夥伴廠商已累積出貨超過二百二十億顆以Cortex-M核心為基礎的裝置。

在物聯網需求暢旺之下,新一代Cortex-M處理器自然要針對這些新需求納入相關的設計,為所有嵌入式系統融入適合的安全基礎。Cortex-M23與Cortex-M33處理器是廣受歡迎Cortex-M產品家族的最新成員。因此,兩款處理器保留了用戶對嵌入式產品預期的各項特色,像是穩定的即時中斷反應、低功耗、小尺寸、易於開發,以及32位元運算效能,而安全基礎則是透過加入TrustZone技術來達成。兩款處理器加上如此蓬勃的生態體系全力支持,勢必能夠在眾多市場開創出可觀商機。

ARMv8-M專屬 TrustZone建構安全基礎

TrustZone是新款基於ARMv8-M架構處理器的一項里程碑,它不僅為程式碼、記憶體、I/O提供硬體存取控制機制,還持續滿足嵌入式應用的各項要求,包括即時反應、最低的切換資源、受限制的晶片內部資源,以及簡化軟體開發。

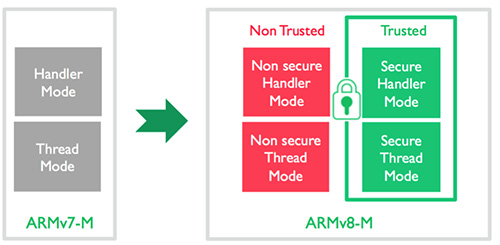

ARMv8-M針對處理器的運作額外新增一種狀態,因此現在有安全與非安全的執行狀態。這些安全狀態和現有的Thread線程以及Handler模式之間無相依性,因此兩種模式可在安全以及非安全狀態下並存。

處理器的設計包含以下特色:四個堆疊與四個堆疊指標暫存器;硬體堆疊極限檢查;透過類似記憶體保護單元(MPU)的可程式化安全歸屬單元(SAU),或固定/外部安全組態,將記憶體空間劃分成安全與非安全空間;在切換至非安全執行狀態時,例外處理硬體會自動儲存然後清除安全暫存器的狀態;以非安全模式轉換至安全程式碼時,會被限制在安全閘道器(SG)指令所設定的安全程式碼範圍,以及被標記為非安全可呼叫(NSC)區域內(圖1)。

|

| 圖1 ARMv8-M額外增加的狀態 |

兩種完整狀態開啟了新應用的大門。以安全狀態供應的高價值韌體經常被系統中的非安全應用所使用,而且受到完整的保護。安全狀態下的監視者程式可用來在經歷軟體攻擊或非可靠作業條件之後執行系統回復,開發人員仍可繼續利用非安全區塊為Cortex-M開發軟體。

TrustZone的設計模式讓現有使用者能夠繼續在非安全區域內從事研發,方式和過去完全相同。除錯與追蹤功能也有所改良,開發複雜應用會比過去更簡單。程式開發可完全採用C語言,在為所有Cortex-M處理器撰寫程式時都可使用所有例外處理器。現有的程式碼可輕易移植到Cortex-M23與Cortex-M33上重複使用,只須微幅變更設定(如果有必要),例如MPU設定碼等。這些要素提高了程式設計人員的生產力,因此能在更短時間向市場推出更複雜的解決方案。

維持熟悉工作模式 程式開發人員容易上手

就嵌入式解決方案而言,程式設計人員是最寶貴的資源,因此維持熟悉的開發環境,對於任何新處理器的設計工作而言,都是一項關鍵考量因素。在Cortex-M23與Cortex-M33方面,建構安全解決方案的複雜性,可藉由TrustZone有效排除,回復到傳統程式開發人員以及所有開發者慣用的設計模式。

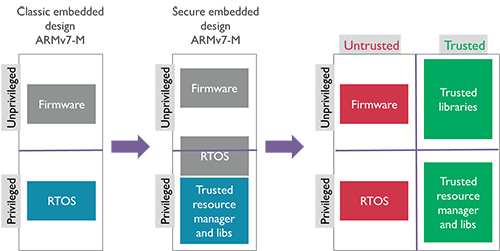

圖2顯示了設定方法。程式開發者習慣採用的典型模式內包含兩種層級,優先與非優先。現今市面上的安全解決方案必須為受信任資源管理器保留優先層級,其餘軟體會被排擠到另一種層級。

|

| 圖2 回復到傳統程式開發人員的模式 |

在Cortex-M33與Cortex-M23方面,置入兩種額外的狀態。使用者方面回到典型模式,安全區域則安排給受信任軟體獨享,該區域還分成兩種狀態。這樣的設定不僅為安全解決方案開啟創新的大門,還能保存程式開發人員熟悉的模式。

整合多種驗證方案 安全除錯充分保護

新架構的安全功能涵蓋整個系統的許多層面,包括除錯與追蹤功能。Cortex-M23與Cortex-M33處理器提供的除錯驗證介面讓晶片設計者能整合多種除錯驗證解決方案,像是ARM TrustZone CryptoCell。

用戶可透過除錯驗證功能,選擇設定成晶片允許所有除錯與追蹤功能、只允許非安全的除錯與追蹤功能,或關閉所有除錯與追蹤功能。除錯功能的權限等級(例如中斷、單步執行以及核心暫存器存取)與追蹤功能(例如指令追蹤、資料追蹤、事件追蹤)也能分開單獨設定。

如果只啟用非安全除錯與追蹤,除錯與軟體開發人員就無法存取安全記憶體,而且只能看到非安全軟體的運行狀況。在執行安全程式碼時,除了硬體會阻止處理器被中斷(例如採用單步執行的方式)外,追蹤功能也會防止安全程式碼的執行資訊外洩。因此,安全程式會受到充分的保護。

新處理器家族問市 開發人員選擇更多

ARM與現有夥伴合作,為他們提供技術資訊,協助改造其產品,納入Cortex-M23與Cortex-M33處理器。其中許多夥伴將在新一代處理器家族問市之際同步推出相關產品。

兩款處理器都採用ARMv8-M指令集,由於ARMv8-M是ARMv6-M與ARMv7-M的超集合,因此生態體系的夥伴要轉換跑道,面臨的障礙相對少得多。軟體與工具都經過修改以支援某些暫存器定義的異動,而且還經過更新,能使用新的記憶體管理單元,與獲得的效益相比,這些投入都只能算是微末小事,因為支援TrustZone技術的新一代處理器將帶動一波極其可觀的新發展機會。

許多過去運用開發工具與軟體來讓ARMv8-A支援TrustZone的夥伴廠商,現在能擴展其支援範疇,納入ARMv8-M專屬TrustZone的支援能力。這項簡單的轉移管道進一步擴展了Cortex-M的產業體系。

體積最小最省電 Cortex-M23進軍嵌入式應用

Cortex-M23是所有搭載TrustZone技術的ARM處理器中體積最小且最省電的元件(圖3)。Cortex-M23採用ARMv8-M基線架構,是各種受限制嵌入式應用的理想處理器,這類產品對於安全有多方面的要求。

ARMv8-M專屬的TrustZone帶來硬體執行的隔離機制,分隔每個Cortex-M23元件中信任與非信任資源。因此TrustZone帶來一個理想的基礎,在此之上開發各種嵌入式應用,這類產品以往須用到兩個獨立的實體處理器才能確保受信任與非信任資源之間做好確實的隔離。Cortex-M23提供一個紮實的安全基礎,滿足包括裝置辨識管理、高價值韌體保護、軟體認證、以及安全開機等方面的需求。

Cortex-M23是一款雙階管線化處理器,儘管小巧卻能支援整套ARMv8-M基線指令集。該指令集包含約八十個Thumb指令,大多數寬度為16位元,使程式碼長度儘可能縮減,甚至還收錄少數32位元指令,利用這些指令來提高效率。

Cortex-M23支援所有ARMv6-M指令,確保用戶能輕易地把程式碼從Cortex-M0轉移到Cortex-M0+。另外,ARMv8-M基線指令集還收錄多項新指令,用來改進條件式處理、互斥存取、分區作業、以及立即移動等程序的效率。

以Cortex-M23為基礎的低功耗微控制器可望獲得未來各種日常電子產品的信任,例如家用保全攝影機或生物特徵驗證裝置。這款小巧晶片適用範疇極為廣泛,為各種自我驗證的量產裝置提供有線聯網功能。此外,Cortex-M23另一項應用領域將是極度省電的生醫植入裝置,一般運用在更加成熟的技術領域,這類產品採用專屬的低漏電元件庫。

對於較大規模節點而言,緊湊性相當重要,TrustZone能藉由區隔來提高安全性。

最後,整合Cortex-M23處理器的相關除錯功能,有助於加快軟體的開發。使用者除了可透過一個JTAG埠或一個2腳位(Pin)的串列線除錯埠來觀測系統狀態外,還可選購嵌入式追蹤巨集電路元(Embedded Trace Macrocell, ETM)與微型追蹤緩衝區(Micro Trace Buffer, MTB),即可得到卓越的指令追蹤功能,選購中斷點單元(Break Point Unit, BPU)與資料觀察與追蹤單元(DWT)則可使用中斷點與硬體觀測點來執行除錯。

Cortex-M33在效能、省電性、安全性以及生產力之間取得最佳的平衡點。M33是第一款採用ARMv8-M架構的全功能處理器,並內建TrustZone安全技術與數位訊號處理功能(圖4)。

兼具效能/省電/安全 Cortex-M33全功能

M33支援大量的彈性組態選項,除了促成業界發展種類廣泛的應用外,還提供專屬的協同處理器介面,用來加快緊密耦合、頻率以及運算密集的作業。

Cortex-M33的特色與功能包括:ARMv8-M架構的主線延伸,包括16位元與32位元Thumb指令集;ARMv8-M例外狀況處理模型;選配的記憶體保護單元(MPU),以ARM保護記憶體系統架構(PMSAv8)為基礎,每個安全狀態配置最多十六個分區;選配的ARMv8-M Security Extensions(TrustZone)安全延伸集;選配的Configurable Security Attribution Unit,每個單元最多支援八個記憶體分區;選配的單精度浮點運算單元,採用ARM FPv5架構;選配的ARM數位訊號處理(DSP)延伸集;選配的執行追蹤功能,使用MTB或ETM;整合式中斷控制器,支援一至四百八十個外部中斷,最高支援二百五十六個優先權限等級;選配協同處理器介面,最多支援八個協同處理器單元。

Cortex-M33核心在設計時即搭配一種循序式三階管線。大多數指令在兩個階段就能完成,而較複雜的指令則需要三個階段。部分的16位元指令採雙派發(Dual-issued)模式。此核心具備兩個先進微控制器匯流排架構(AMBA)5先進高效能匯流排(AHB)5介面。AHB5規格能將安全性擴展到整個系統。Cortex-M33處理器內含一個專屬的協同處理器匯流排介面,該介面設計用來整合緊密耦合的加速器硬體,並包含控制與資料通道,最多能支援八個協同處理器。協同處理器會收到有關處理器的優先權限與安全狀態的資訊,以及指令種類和相關的暫存器與運作欄位。

協同處理器的作業會在合理數量的週期內完成,或在完成後立即中斷。系統可以選擇在資料與作業完成傳輸後立即啟動,或是處理器讀回結果後再啟動。若如果還沒有準備好,還可安插多種等待狀態。

對於經常用到的運算密集作業,這個介面還提供一種機制,用來在系統中加入客製化處理程序,所需的設計與驗證工作極少,更重要的是開發者依然能享受Cortex-M產業體系帶來的廣泛工具、軟體以及作業系統的選項。

選配的整數DSP延伸集新增八十五個飽和運算與單一指令多重資料(SIMD)運算功能。在大多數情況下,DSP指令在處理訊號方面的效能平均比軟體函式庫高三倍。

選配的單精度浮點運算延伸方案採用FPv5單元,內含額外增加的16-entry 64位元暫存器檔案以及相關的中斷處理機制。另外還可選配增加四十五個IEEE754-2008相容單精度浮點運算指令。使用浮點運算指令通常能得到比軟體函式庫高十倍的效能。浮點運算單元另外安置於專屬的電源域(Power Domain),在沒有啟用或使用時能單獨關閉供電。越來越耗時的應用驗證程序,使得晶片內部除錯與追蹤作業攸關產品是否能及時問市。

Cortex-M33處理器內建的除錯功能可加快軟體研發流程。使用者可透過JTAG埠或二針腳的串列線除錯埠來觀測系統。選配的ETM與MTB提供卓越的指令追蹤功能,而BPU與DWT則讓使用者能利用中斷點與硬體觀察點進行除錯。

在這些選配功能的力助下,Cortex-M33處理器不僅具備高度可設定的彈性,還能輕易調整組態以因應多元化的系統需求。研發業者可快速開發出各種複雜系統,在產品中納入最適合的元件組合,包括MPU、DSP、浮點運算單元(FPU)、TrustZone、ETM、MTB、檢測追蹤巨集單元(Instrumentation Trace Macrocell, ITM)、BPU、DWT以及協同處理器介面功能。

在簡單控制系統方面,巢狀向量中斷控制器(Nested Vectored Interrupt Controller, NVIC)控制器能設定成單一中斷,而在中斷密集系統應用中,NVIC可設定成支援四百八十個實體中斷,以及二百五十六個階層的優先權限。在許多不同程序要求安全運作的系統中,可加入MPU用來執行程序分隔,以及使用優先存取模式。若想提升對程式碼、資料、以及資源的保護力,TrustZone會是更好的選擇。

瞄準智慧聯網裝置 新處理器摩拳擦掌

Cortex-M33與Cortex-M23設計用來填補市場對智慧與聯網裝置的需求,延用傳統程式開發模型,以簡化開發者的轉移工作。兩款處理器的TrustZone專為嵌入式產品量身設計,用來提供可靠的即時中斷反應、低功耗以及微縮占用空間等特性。