在所有元件特性中,雜訊可能是一個特別具有挑戰性、難以掌握的設計課題。本文主要介紹電源雜訊對於高速數位類比轉換器(DAC)相位雜訊的影響。

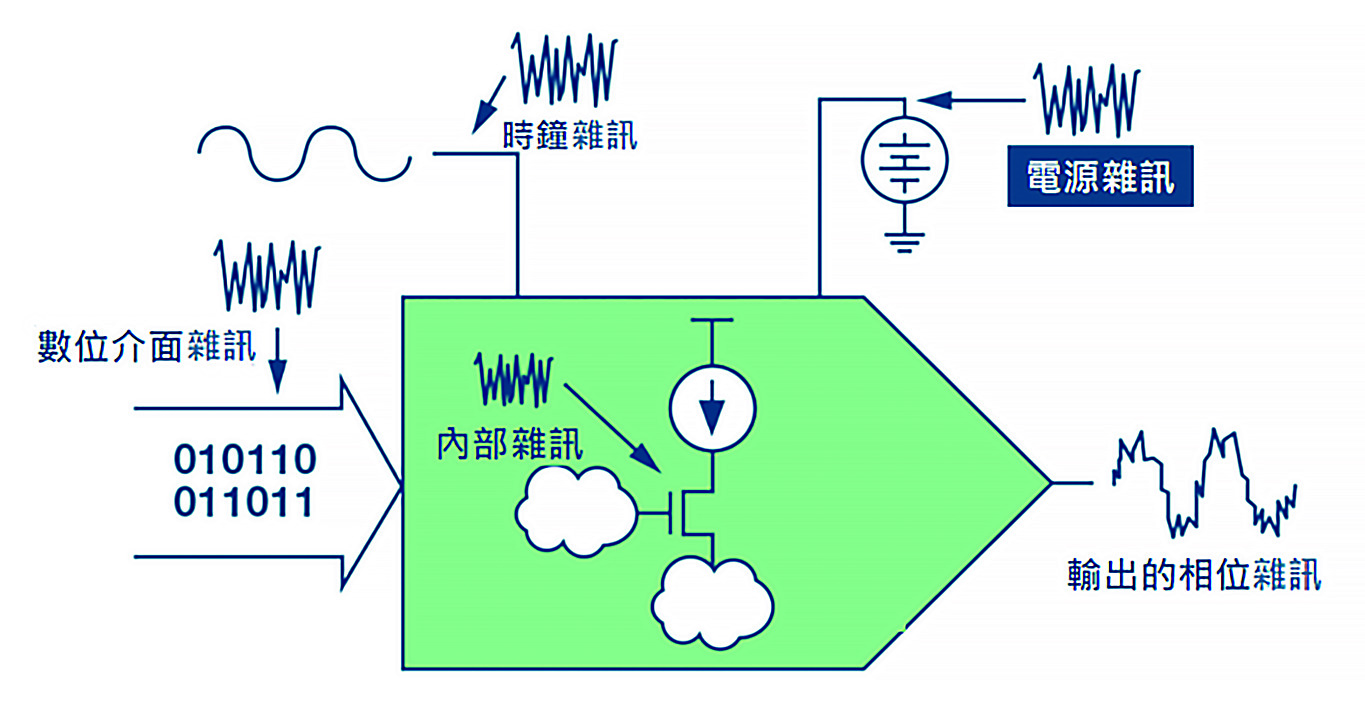

對於高速數位類比轉換器(DAC)來說,相位雜訊主要來自時鐘雜訊、電源雜訊,以及內部雜訊與介面雜訊(圖1)。其中,時鐘雜訊與電源雜訊是最重要的兩個來源。本文首先分析DAC相位雜訊產生的原因,並著重分析電源雜訊對於DAC相位雜訊的影響,以及分析相位雜訊的方法,並針對如何選擇超低雜訊的電源元件提供建議。

圖1 DAC相位雜訊來源 (圖片來源:ADI)

圖1 DAC相位雜訊來源 (圖片來源:ADI)

DAC電源相位雜訊傳播路徑

晶片上的所有電路都必須透過某種方式供電,為雜訊傳播到輸出提供許多機會。不同電路電源雜訊的傳播路徑也不一樣,下面著重指出了幾種常見的DAC電源雜訊傳播路徑。

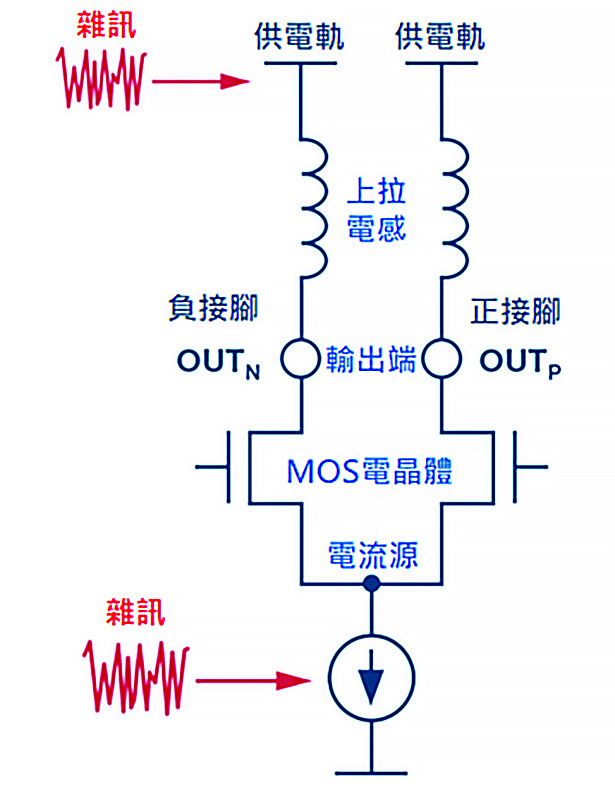

如圖2所示,DAC輸出端通常由電流源和MOS電晶體組成,MOS電晶體引導電流透過正接腳或負接腳供電。電流源從外部電源獲得功率,任何雜訊都會反映為電流波動。

圖2 DAC電源雜訊來源 (圖片來源:ADI)

圖2 DAC電源雜訊來源 (圖片來源:ADI)

MOS電晶體

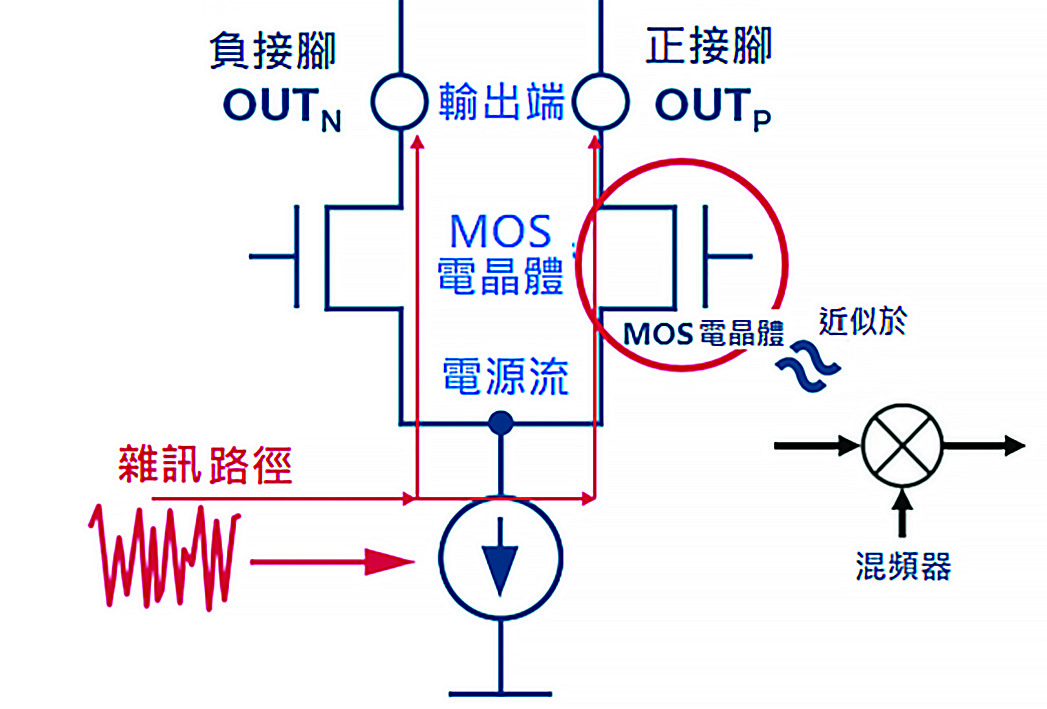

電流源的雜訊可以經過MOS電晶體到達輸出端(圖3),但這僅解釋了雜訊的耦合現象。如果要「貢獻」相位雜訊,此雜訊還需要透過MOS電晶體混頻到載波頻率。此處的MOS電晶體,相當於一個平衡混頻器。

圖3 DAC電源雜訊傳播路徑——MOS電晶體 (圖片來源:ADI)

圖3 DAC電源雜訊傳播路徑——MOS電晶體 (圖片來源:ADI)

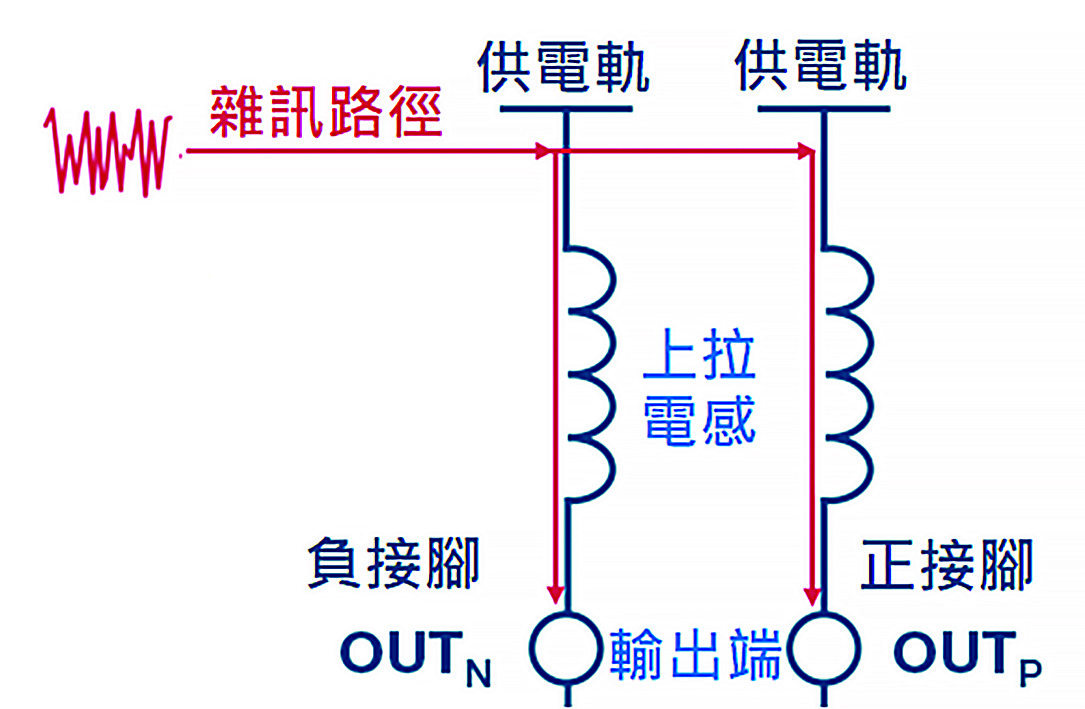

上拉電感

上拉電感是另一條雜訊路徑,雜訊從供電軌流至輸出端(圖4)。此處的任何供電軌和負載變化都會引起電流變化,進而又一次將雜訊混頻到載波頻率。

圖4 DAC電源雜訊傳播路徑——上拉電感 (圖片來源:ADI)

圖4 DAC電源雜訊傳播路徑——上拉電感 (圖片來源:ADI)

更多雜訊傳導路徑

一般來說,如果開關切換能夠把雜訊混頻到載波頻率,這些開關電路都是電源相位雜訊的貢獻者。

分析相位雜訊

對於上面提到的混頻現象,要快速模擬所有這些行為並進行改善相當困難。透過測量電源抑制比(PSRR)的做法,快速瞭解哪些電源對雜訊敏感,接著針對性地選擇一些高精度低雜訊的電源,才能事半功倍。

其他類比模組也具有類似的電源抑制比分析,比如穩壓器、運算放大器和其他IC,一般都會規定電源抑制比。

電源抑制性能衡量負載對電源變化的靈敏度,可用於相位雜訊分析。此處使用的並非抑制比,而是電源調變比(PSMR)。當然,傳統的電源抑制比依然有其參考意義。

本文專門調變一個雜訊進行測試。下文是獲得的具體資料。

三步驟測量PSMR

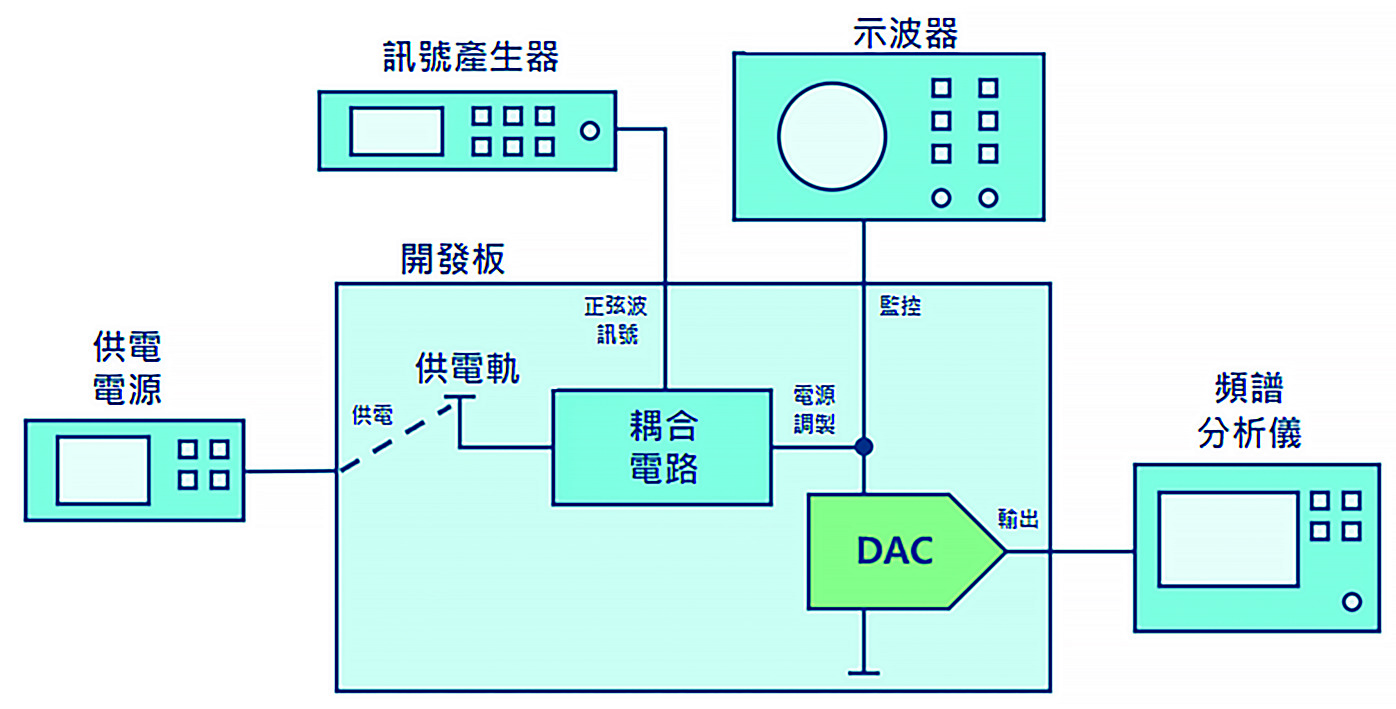

分析相位雜訊的其中一個重要方法便是測量PSMR。典型測量PSMR測試原理如圖5所示。PSMR測量可以分成三步驟:調變供電軌、獲取資料、分析資料。

圖5 PSMR測量 (圖片來源:ADI)

圖5 PSMR測量 (圖片來源:ADI)

電源調變透過一個插在供電電源與負載之間的耦合電路獲得,疊加上由訊號產生器生成的正弦波訊號。

耦合電路的輸出透過示波器監控,以監控實際電源調變。最終得到的DAC輸出,由頻譜分析儀檢測得出。

PSMR等於從示波器顯示的電源交流分量與載波周圍的調變邊帶電壓之比。

PSMR測量要點

耦合電路存在多種不同的耦合機制,耦合電路可以選擇LC電路,電源運算放大器、變壓器或專用調變電源。這裡使用的方法是1:100匝數比的電流檢測變壓器和函數產生器。建議使用高匝數比以降低訊號產生器的來源阻抗。

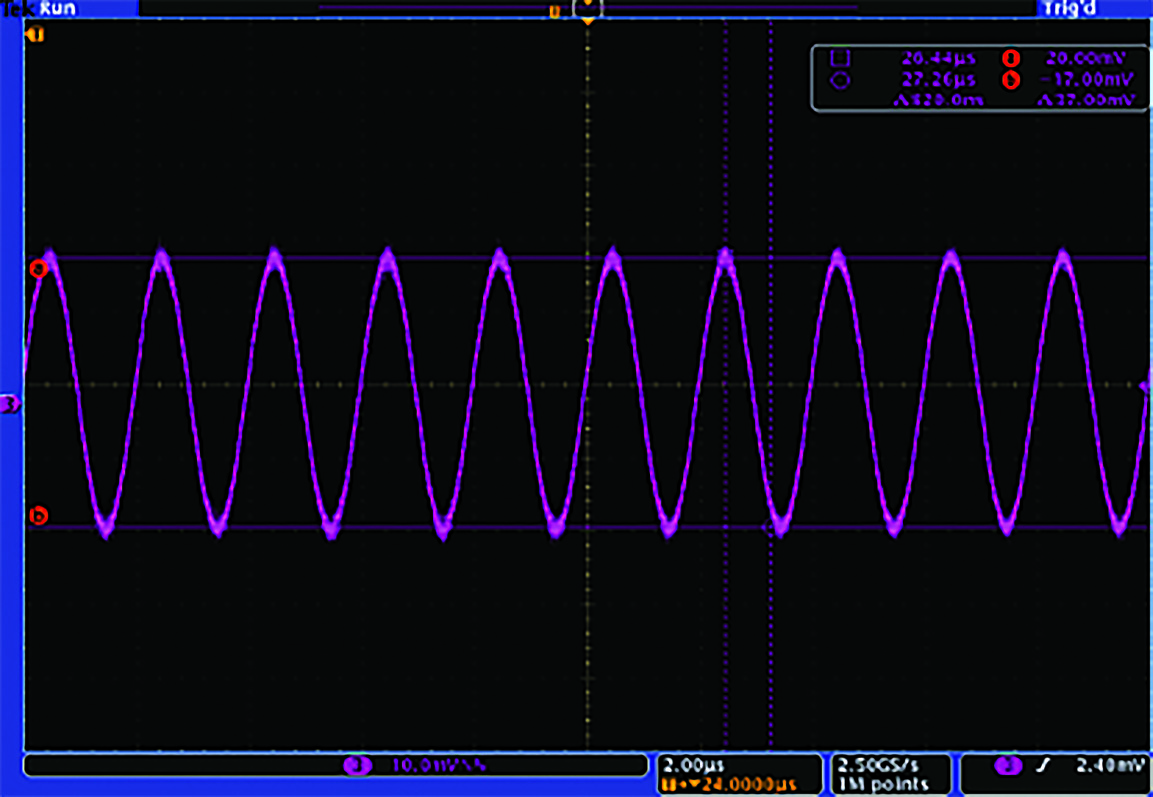

1.2V直流電源上疊加一個500kHz峰峰值電壓38mV訊號調變所得(圖6)。

圖6 時鐘電源調變 (圖片來源:ADI)

圖6 時鐘電源調變 (圖片來源:ADI)

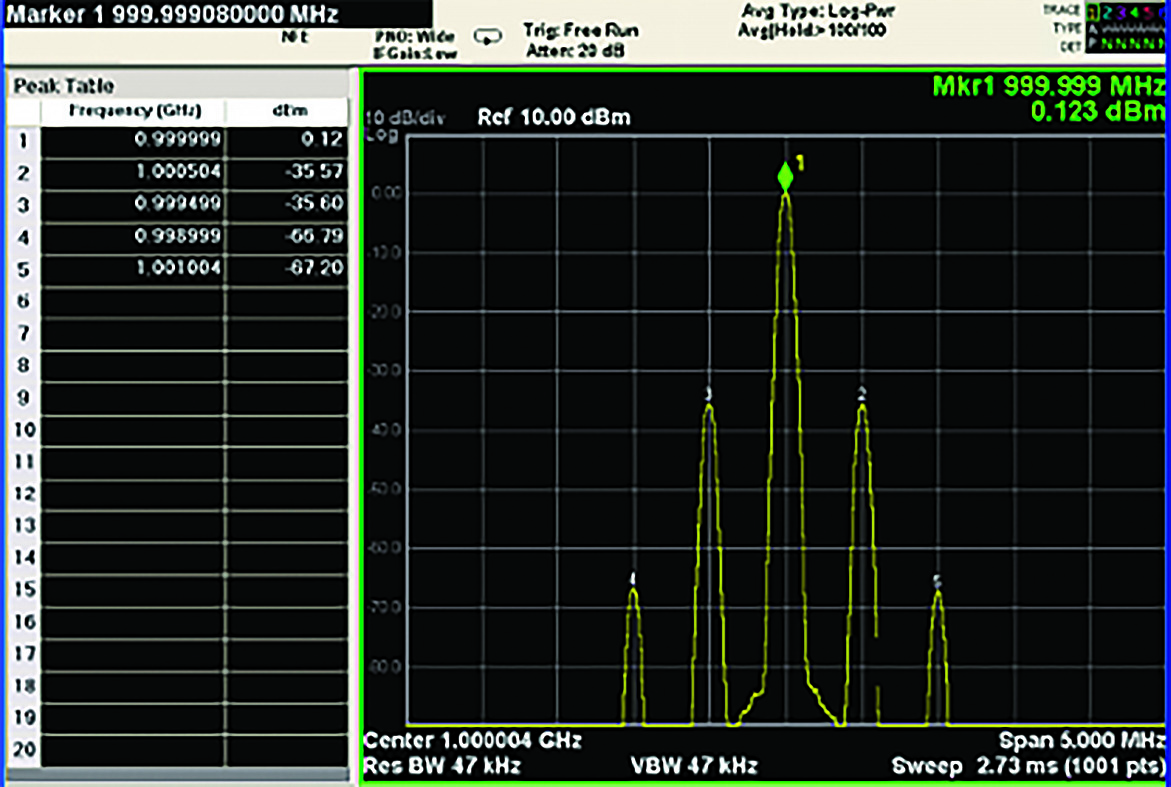

此處採用ADI的AD9164,DAC時鐘速度為5GSPS,所得輸出在一個滿量程1GHz、-35dBm載波上引起邊帶(圖7)。

圖7 調變邊帶 (圖片來源:ADI)

圖7 調變邊帶 (圖片來源:ADI)

將功率轉換為電壓,接著利用調變電源電壓求比值,所得PSMR為-11dB。

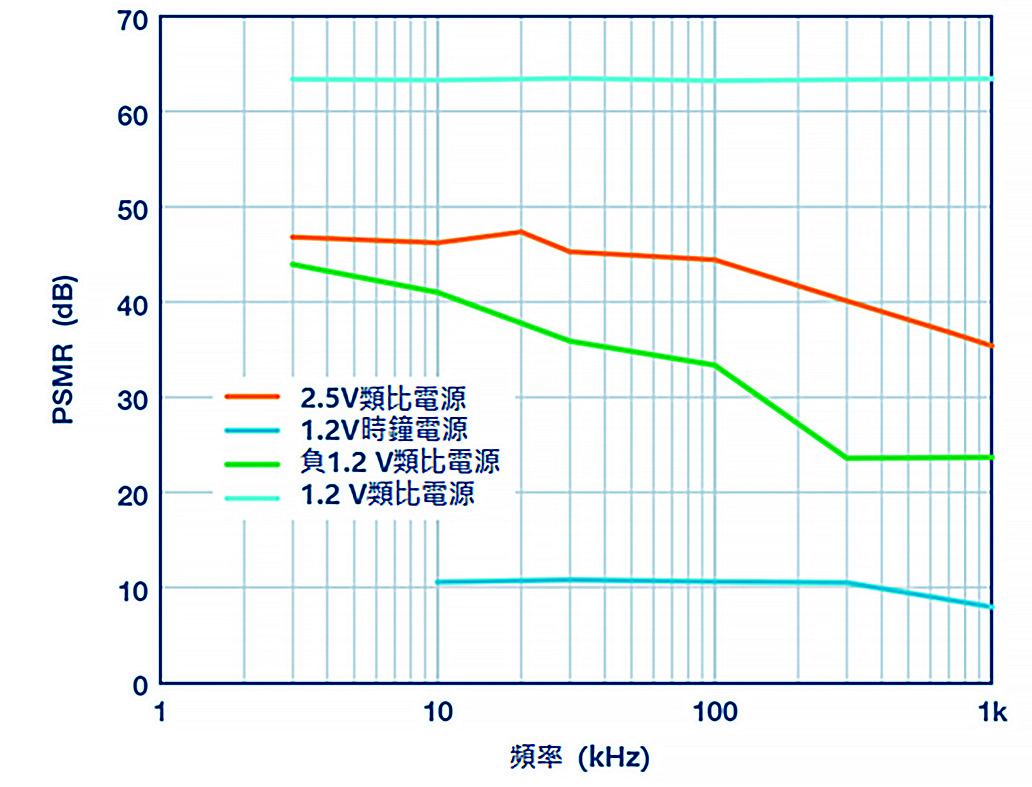

AD9164有八個電源,我們選擇重點掃描以下四個電源:1.2V時鐘電源、負1.2V和2.5V類比電源、1.2V類比電源。結果如圖8所示。

圖8 掃描頻率測得的電源PSMR (圖片來源:ADI)

圖8 掃描頻率測得的電源PSMR (圖片來源:ADI)

時鐘電源是最為敏感的供電軌,接著是負1.2V和2.5V類比電源,1.2V類比電源則不是非常敏感。加以適當考慮的話,1.2V類比電源可由開關穩壓器供電,但時鐘電源完全相反,需要由超低雜訊LDO供電,以獲得優質性能。

選擇超低雜訊的電源

LDO的選擇

LDO是久經考驗的穩壓器,尤其適合用來實現優質雜訊性能。對於敏感的電源軌道,也不是所有的LDO都可以勝任,依舊需要根據整體系統要求進行選擇與測試。

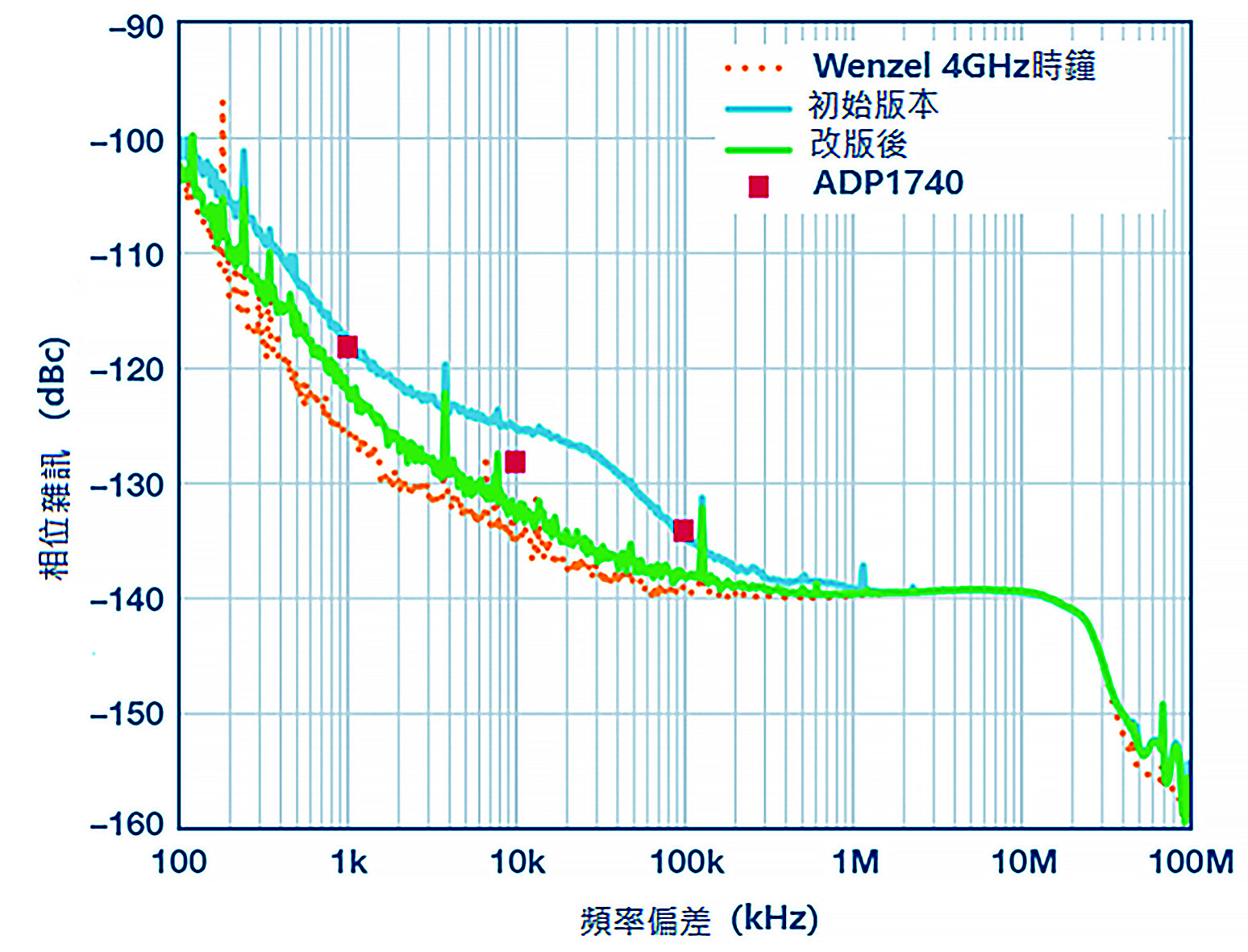

測試的方法係利用該LDO的頻譜雜訊密度曲線和DAC PSMR測量結果進行比對。舉例來說,某一電路在初始版本使用LDO ADP1740,對比LDO的頻譜雜訊密度曲線和DAC PSMR測量結果,如圖9所示。這證實了時鐘電源(圖9紅色點)對雜訊的影響。改版後,更換使用ADP1761,某些特定頻率處雜訊降低多達10dB。

圖9 AD9162評估板相位雜訊(圖片來源:ADI)

圖9 AD9162評估板相位雜訊(圖片來源:ADI)

在Digi-Key網站,可以根據參數來篩選合適的LDO,其中包括直接透過電源抑制比(PSRR)來篩選的功能(圖10)。

圖10 透過PSRR篩選LDO

圖10 透過PSRR篩選LDO

其他方案

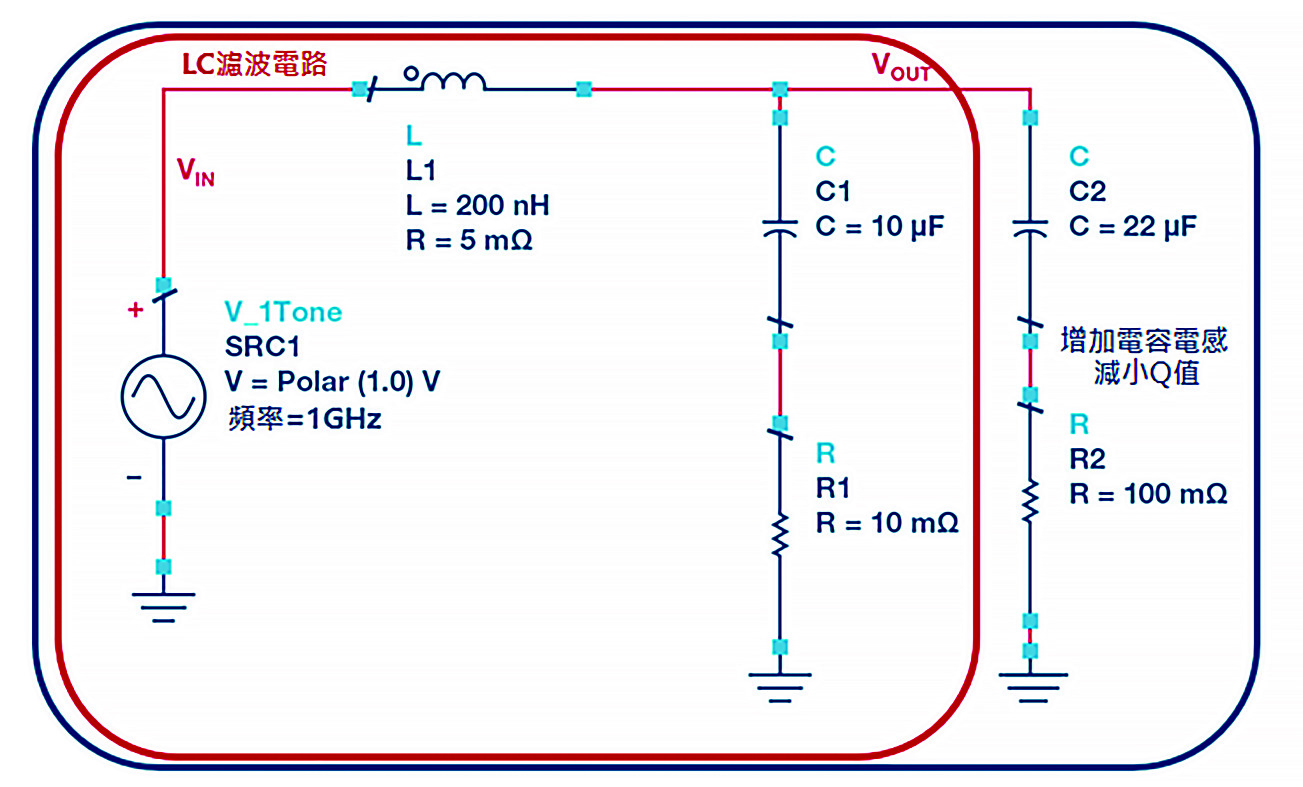

不過,這並不代表除了LDO,別的電源便不可以用。根據整體系統要求,透過適當的LC濾波,開關穩壓器也可以提供電源,進而簡化電源解決方案。採用LC濾波器應注意串聯諧振,否則雜訊可能變得更糟。對於諧振可透過對電路降低Q值加以控制,例如為電路增加損耗性元件。

圖11顯示了來自另一個設計的例子,其採用AD9162 DAC。時鐘電源也由ADP1740 LDO提供,但其後接一個LC濾波器。

圖11 LC濾波器和去Q網路 (圖片來源:ADI)

圖11 LC濾波器和去Q網路 (圖片來源:ADI)

原理圖中顯示了所考慮的濾波器,RL模型表示電感,RC模型表示主濾波電容(C1+R1)。紅圈裡是原始的LC濾波電路,藍圈是為了減小Q值額外增加的損耗性元件。

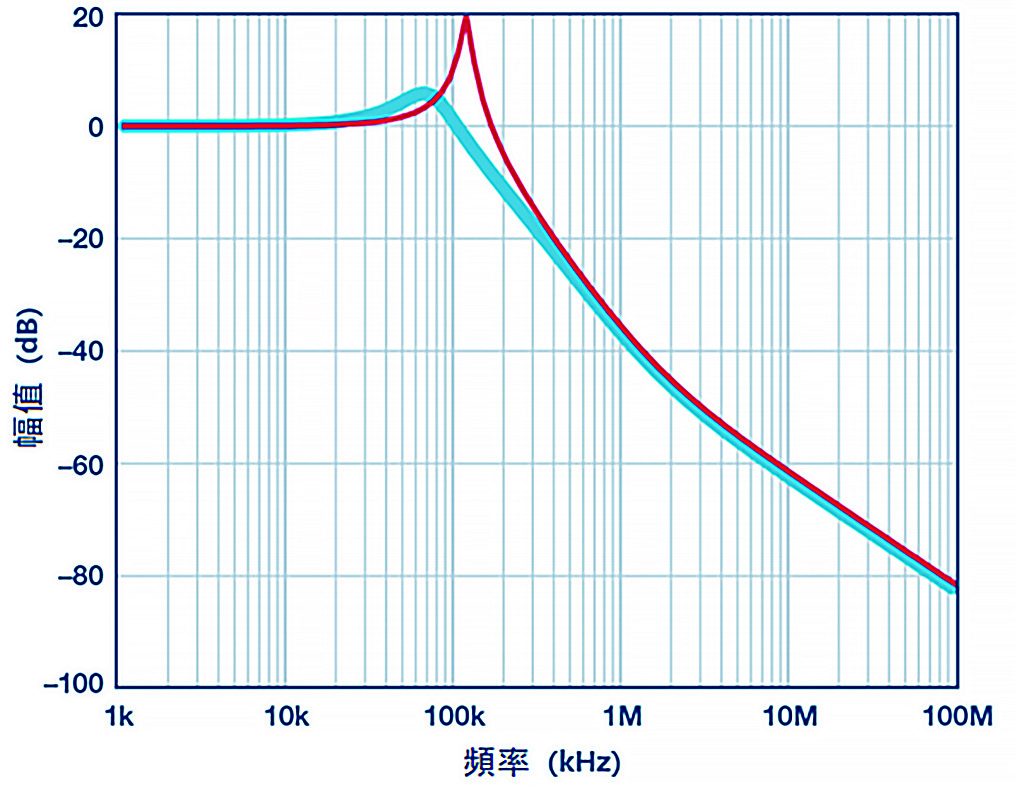

濾波器響應如圖12所示,紅線是原始的LC電路響應曲線,藍線是改進後的響應曲線。可以看出Q值減小。

圖12 LC濾波器響應 (圖片來源:ADI)

圖12 LC濾波器響應 (圖片來源:ADI)

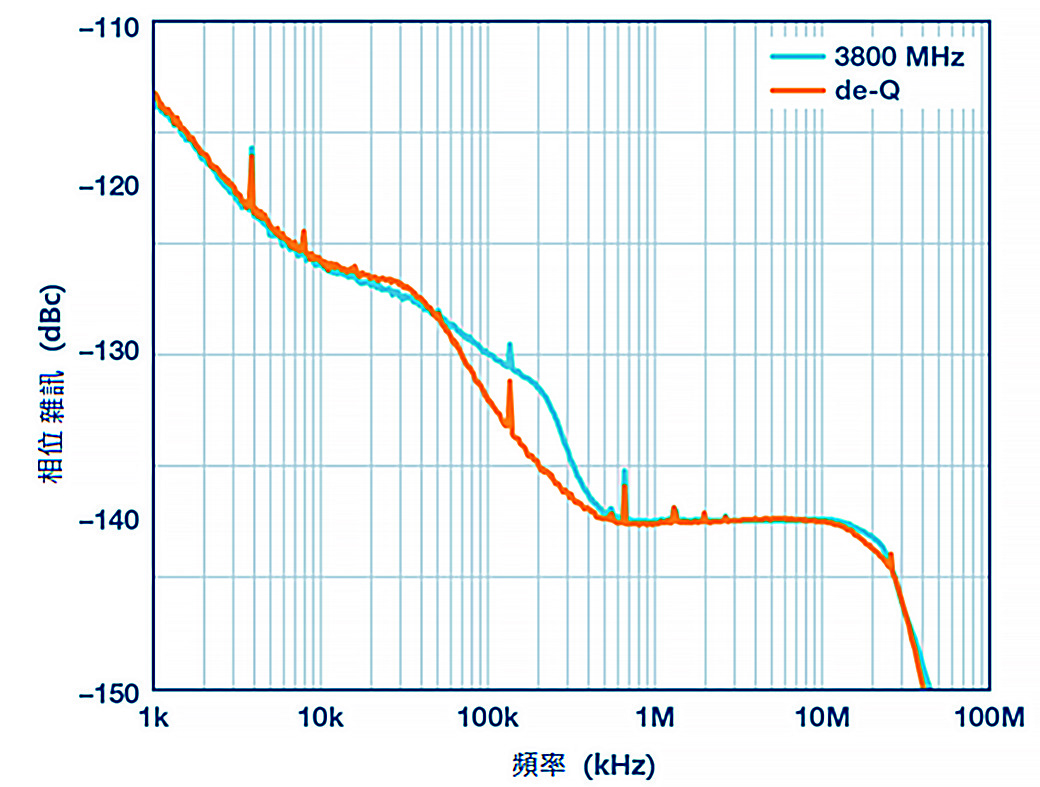

圖13顯示相位雜訊響應,藍線是原始的LC電路響應曲線,橙線是改進後的響應曲線,相位雜訊得到改進。

圖13 相位雜訊響應 (圖片來源:ADI)

圖13 相位雜訊響應 (圖片來源:ADI)

雜訊選擇至關重要

雜訊不僅會因為電源選擇的不同而大不相同,而且可能受到輸出電容、輸出電壓和負載影響。設計時應仔細考慮這些因素,對於敏感的供電軌來說尤其如此。

(本文作者任職於Digi-Key)