量子體積(QV)最早由IBM提出,現已成為量子領域的評估指標。然而,QV最初用於基於電路的量子電腦(CBQC),因此無法直接適用於基於量測的量子運算(MBQC)處理器,為此,本文首先說明適合採用MBQC的光子量子處理器特性,並介紹為量化處理器性能而研發的QV框架。

量子技術正在為未來的運算鋪路,超越傳統運算能力限制。在用於量子資訊處理的各種平台中,光子量子處理器因其可擴展性和可於量子網路中直接部署的潛力而受到關注。然而,若要衡量此類處理器的真正威力,必須評估這些光子系統的性能。本文將討論稱為量子體積(Quantum Volume)的量子電腦性能指標,並說明將該指標應用於光子處理器的方式[1]。

處理器性能指標:量子體積

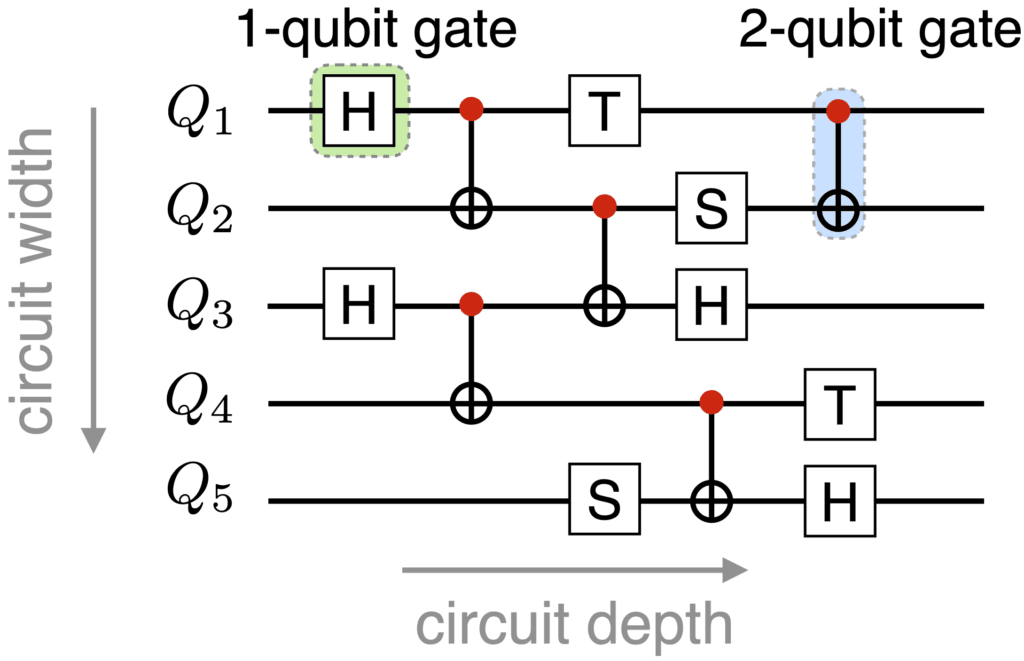

典型的量子運算任務涉及在量子電路中對多個量子位元(Qubit)執行量子閘(圖1)。

圖1 深度為5的量子電路,有5個輸入量子位元

圖1 深度為5的量子電路,有5個輸入量子位元

目前的量子處理器是由少量嘈雜量子位元(Noisy Qubit)所建構而成,被稱為嘈雜中等規模量子(Noisy Intermediate-scale Quantum, NISQ)技術。由於具有雜訊影響,我們需要知道這些嘈雜機器能在多大程度上可靠地執行任務,也就是說,在量子資訊完全被雜訊淹沒並使量子處理器變成隨機機器之前,能夠設計採用多少量子閘(增加電路深度)或是增加多少量子位元(增加電路寬度)。

這些考量即為量子體積(QV)指標的精髓所在。該指標最初由IBM提出,從那時起,QV就被用來回報基於超導電路和捕獲離子(Trapped Ion)量子運算平台的進展情況。QV通常以指數形式呈現,即2d,其中d代表處理器在可靠運作的前提下,所能實現的最大電路維度(即寬度或深度)。

下文將簡要回顧光子量子處理器及其所面臨的挑戰;接著,將介紹實現210QV所需要的光學特性。210QV為超導量子位元或捕獲離子等常見量子運算平台所回報的典型數值。

光子量子處理器以MBQC克服儲存挑戰

量子光子是(可能在室溫下)實現可擴展量子資訊處理的潛力平台,可以作為量子糾錯(Quantum Error Correction)的中繼器,或是分布式量子運算資源的伺服器,以實現量子網路的直接部署[2]。

光子量子位元可為同調脈衝或單光子,是量子光子的基礎。同調通訊技術,如零差偵測器(Homodyne Detector),用於測量編碼於同調脈衝(連續可變)量子位元的量子位元,而單光子偵測器則用於測量基於單光子(離散可變)的量子位元。不過,光子也將面臨相關挑戰,例如當量子位元以光速運行時,便很難儲存量子位元,以及將量子閘應用於量子位元。

為了應對儲存挑戰,光子量子處理器常採用基於量測的量子運算(Measurement-based Quantum Computing, MBQC)方案,而不是適合靜態量子位元的基於電路的量子運算(Circuit-based Quantum Computing, CBQC)方案。在MBQC方案中,光子晶片產生光子量子位元流,這些量子位元經過一系列干涉儀(即延遲線、分束器和移相器),最終將被導向光子偵測器以進行量測。各種閘透過不同的量測基準序列來實現。例如,一個包含三個量子位元的小型量子電路可以透過對42個脈衝進行一系列測量來實現(圖2),這些脈衝以六個同步脈衝的七個實例的形式在一個六通道光子晶片中穿行。

圖2 MBQC實作示意圖

圖2 MBQC實作示意圖

圖2為MBQC實作示意圖,在此範例中,光子晶片上具有三個量子位元,是深度為1的量子電路,該電路由一個CNOT閘和一個旋轉閘組成。六條波導(編號1至6)用於平行傳輸六個光子量子位元。波導1、3、5傳輸資料量子位元,而波導2、4、6則是用於實作MBQC的輔助量子位元。初始延遲線(黑色圓圈)對同一波導上的連續量子位元進行耦合,隨後的分束器對相鄰波導上的量子位元進行耦合。偵測器所顯示的字母X、Y和Z表示量測基準。量測結果從偵測器傳輸至典型電腦,以便進行數位化和進一步處理。基準的選擇和量測結果將決定所產生的閘。

光子量子處理器的QV評估

光子系統中,雜訊的主要來源是光子損耗(或光訊號衰減)。量子訊號透過波導進行傳輸,並最終在偵測器中被測量。在Cisco量子研究室(Cisco Quantum Lab)2023年所發表的論文[1]中,研究團隊發現了從有損(Lossy)量子光子晶片到由嘈雜閘組成的電路的投射(Mapping),能夠實現光子處理器的QV計算。研究結果顯示,光子硬體需要進行改進,才可將損耗降低至約10%(或0.5dB),此外,同調脈衝量子位元的擠壓率(Squeezing Rate)需要達到18dB,才能實現210的QV值。

截至本文撰寫時,全球光學實驗室已回報的最高擠壓率為15dB[3],而大多數光子損耗發生在波導介面,即訊號進入晶片及在偵測器進行測量的時候。介面端的損耗率通常為20%(或1dB)。將上一段所提到的需求與現有資料進行比較,顯示儘管差距不大,若要真正達到理想的擠壓和損耗率水準,仍需要進一步提高硬體品質。

量化指標助攻硬體升級

光子量子處理器為量子資訊處理帶來令人興奮的前景,而使用量子體積等指標評估其效能,可以在各種量子技術之間進行有意義的比較。未來,可期待透過光子硬體和編碼方案的進步,實現更優秀的性能以應對光子損耗所帶來的挑戰。

於本文撰寫時,各研究單位尚未實現基於MBQC的通用光子處理器。在處理器的研發過程中,性能量化將扮演重要角色,相關工具如Cisco研究團隊所發表的QV框架將有助於硬體研發,可用於回報進展、識別瓶頸和設計技術路線圖。

(本文作者任職於Cisco)

參考資料

[1] https://journals.aps.org/prl/abstract/10.1103/PhysRevLett.130.110602

[2] https://outshift.cisco.com/blog/long-distance-quantum-communication

[3] https://journals.aps.org/prl/abstract/10.1103/PhysRevLett.117.110801