提高功率密度與電源轉換效率,是電源設計者多年來持續追求的目標。伴隨著系統設計日益複雜,電源設計者必須滿足的性能指標日益嚴苛,現有技術或解決方案的局限也越來越明顯,需要靠各種創新才能克服。

物聯網(IoT)概念的興起,對電源設計帶來許多前所未有的挑戰。在邊緣端,大量以電池供電的裝置內建了各種複雜的休眠或省電模式,以盡可能延長電池壽命。同時,為了節省成本,這些裝置必須十分小巧,能留給電源子系統的空間往往非常有限。這些因素使得電源設計者在進行設計除錯與尺寸微型化方面,遇到了許多挑戰。在雲端資料中心部分,電源設計者則遇到了如何提高能源轉換效率與輸出功率,電源系統的尺寸又至少要維持一致的矛盾難題。

意法半導體數位電源成電源設計新趨勢

意法半導體(ST)亞太區微控制器事業體技術行銷專案經理張世昌(圖1)指出,為了讓有限的能源發揮最大的效益,傳統上使用類比技術實現的電源系統,都開始導入微控制器(MCU),實現數位化的控制機制,甚至藉由數位控制技術來實作更複雜的拓撲。這種以MCU為核心的電源系統,就是一般所說的數位電源。

圖1 意法半導體亞太區微控制器事業體技術行銷專案經理張世昌指出,MCU可為電源系統帶來諸多傳統架構不具有的優勢

圖1 意法半導體亞太區微控制器事業體技術行銷專案經理張世昌指出,MCU可為電源系統帶來諸多傳統架構不具有的優勢

跟類比電源相比,數位電源有許多優勢,包含更大的設計彈性、可以輕鬆實現更完整的通訊功能,以及把複雜的控制機制帶進電源系統裡。這些優勢都跟MCU有關,因為MCU除了內建CPU核心之外,通常還整合了大量通訊介面I/O,這使得開發者可以藉由程式來調整許多參數,來改變PWM輸出,滿足不同條件或應用的需要;也可以利用內建的通訊介面,更快地將聯網功能帶進電源系統。在很多應用案例中,電源系統本身都需要具有運作狀態監控並將資料回報給後台的能力,具有完整通訊功能的MCU,可以協助設計者快速實現這些功能。

由於數位電源具有這些優勢,客戶對相關解決方案的需求不斷增加。為滿足市場需求,意法在自家的MCU產品線規劃中,特別制定了一系列專門針對數位電源應用所設計的MCU方案。意法旗下的混和訊號MCU家族,例如STM32F3與STM32G4系列,都很適合應用在數位電源上。這類混合訊號MCU都具備實現數位電源所需的週邊功能。G4是F3的升級版,除了週邊更豐富外,還具有更強大的運算效能跟即時響應能力,可以提高數位電源的性能表現。

電源量測面臨大考驗 專用設備解難題

信果科技應用工程師方健維(圖2)指出,當前電源量測面臨兩個主要挑戰,一個跟電壓有關,另一個則跟電流有關。

圖2 信果科技應用工程師方健維指出,次世代電源的設計除錯,需要使用專用的量測儀器與解決方案

圖2 信果科技應用工程師方健維指出,次世代電源的設計除錯,需要使用專用的量測儀器與解決方案

在電壓方面,隨著摩爾定律(Moore's Law)不斷推進,核心晶片的工作電壓越來越低,這使得電源訊號變得越來越小,更容易被雜訊所掩蓋。通用型探棒本身的負載會引入一定程度的訊號失真,而隨著電源本身的訊號變小,失真的程度相對被放大,也讓工程師更難看到真實的電源訊號。這些因素都使得工程師更難以透過量測來確保電源一致性。

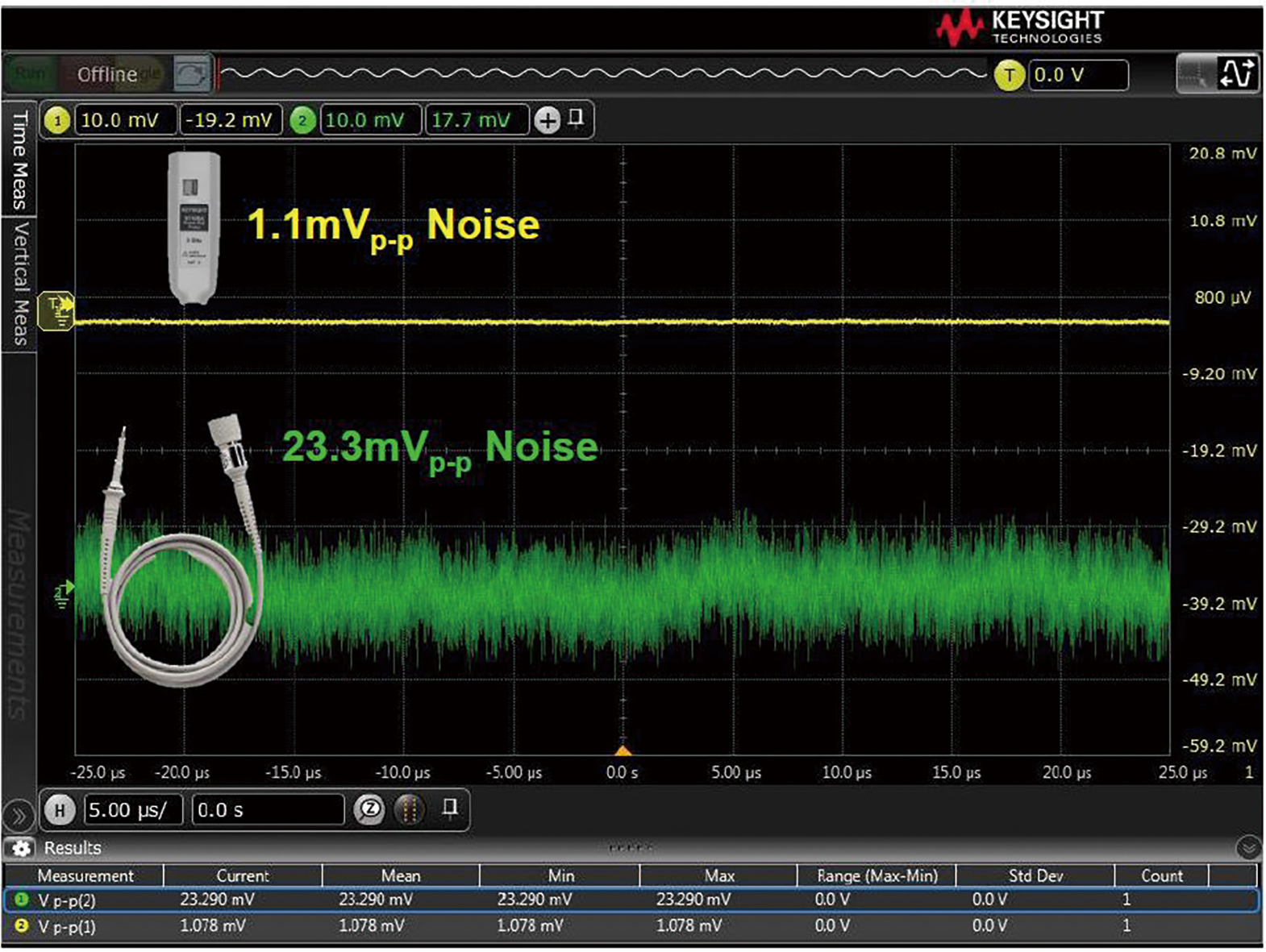

為了克服前述種種問題,針對次世代電源的設計除錯,是德(Keysight)推出了一系列對應解決方案。從探棒開始,對於電源軌的量測,是德就提供專用的N7020A主動探棒,其雜訊水準僅1.1mV,不到典型10:1被動探棒的5%(圖3)。同時,該探棒還具有2GHz頻寬,可以讓工程師在除錯時看到更真實的訊號。

圖3 N7020A探棒(上)與典型10:1被動探棒的雜訊水準比較

圖3 N7020A探棒(上)與典型10:1被動探棒的雜訊水準比較

至於在電流量測方面的挑戰,主要是跟物聯網(IoT)的興起有關。絕大多數的IoT裝置都是靠電池供電,為盡可能延長電池壽命,這些裝置都有十分複雜的低功耗與休眠模式設計。但在低功耗或休眠模式下,系統從電池汲取的電流是非常微小的,典型的電源量測方案很難準確捕捉到這些微小的電流。

例如通用型示波器本身的雜訊水準,往往就比休眠狀態下的電源訊號要來得高;數位萬用電表雖然有很低的雜訊水準,但取樣率又太低,頻寬也不夠,導致工程師無法靠萬用電表量測到真實的波形。

針對這些以電池供電的系統,是德提出的解決方案是CX3300系列電流波形分析儀,其雜訊水平可低至150pA,同時又有200MHz頻寬與1GS/s的取樣率,並內建完整的分析軟體,可以協助工程師捕捉到細微的電源訊號,並加快分析作業的速度。

合封技術助攻 氮化鎵電源設計更容易

至於在近年屢屢成為熱門話題的寬能隙電源方面,美商旭升半導體(Elevation Semiconductor)研發經理王瑞乾(Alien Wang, 圖4)指出,要讓這類新技術的滲透率進一步提升,合封(Co-packaging)技術會是非常重要的一環。

圖4 美商旭升半導體研發經理王瑞乾認為,氮化鎵功率元件的效益,必須要靠合封技術才能完整發揮

圖4 美商旭升半導體研發經理王瑞乾認為,氮化鎵功率元件的效益,必須要靠合封技術才能完整發揮

合封技術能為氮化鎵(GaN)電源帶來的好處,主要表現在易用性、可靠度與性能的提升,以及簡化系統設計複雜度這幾個面向上。眾所周知,基於氮化鎵材料的場效電晶體(FET),其驅動方法跟需要注意的設計考量,和矽MOSFET是不一樣的。因此,將控制器與GaNFET整合在同一個封裝裡,最直觀的好處就是電源設計工程師可以不用處理這些細節,因為元件供應商已經把這些問題處理好了,而且系統所使用的零件數量也跟著減少,有助於改善成本結構、縮小尺寸。

性能提升也是合封技術能為氮化鎵電源帶來的優勢。氮化鎵元件的開關頻率遠高於矽,因此電源系統中的變壓器尺寸可以明顯縮小,讓電源變得更輕、更小巧。但若使用分立元件(Discrete)來實現,氮化鎵元件的開關頻率必須降低,變壓器的尺寸亦隨之放大,等於是限制了氮化鎵電源的發揮空間。

此外,將控制器與GaNFET整合起來,電源轉換的效率也會明顯提升。如果是用分立元件,電源轉換效率通常會在88%~92%之間;使用整合元件的轉換效率則可以提升到90%~95%。以旭升所提供的參考設計跟評估板來看,典型的轉換效率都落在91~94%之間。

總結來說,氮化鎵電源是非常有潛力的新技術,不僅可以提升電源密度,同時還具備十分優異的轉換效率。但要將氮化鎵電源的效益發揮到最大,必須提升元件整合度。透過合封技術將開關與控制器整合在一起,能為電源應用的開發者帶來許多好處,尤其是追求極致小型化的應用,使用合封元件會是最理想的選擇。

因應高頻切換時代 變壓器設計要有新思維

在寬能隙電源已成為未來趨勢的情況下,如何因應寬能隙功率元件普遍具備的高頻切換特性,成為變壓器設計上的最大考驗。 台科大電子系特聘教授邱煌仁(圖5)指出,提高開關頻率固然可以讓變壓器的尺寸明顯縮小,進而讓電源開發者實現功率密度更高的設計,但在開關頻率變高的同時,如果繼續沿用現有的變壓器,在變壓器上的損耗將明顯增加。如何降低變壓器的損耗,已成為目前電源產業跟學界研究的重點課題。

圖5 台科大電子系特聘教授邱煌仁表示,電源設計工程師如果要拉高開關頻率,如何減少變壓器的損耗,是必須優先解決的課題

圖5 台科大電子系特聘教授邱煌仁表示,電源設計工程師如果要拉高開關頻率,如何減少變壓器的損耗,是必須優先解決的課題

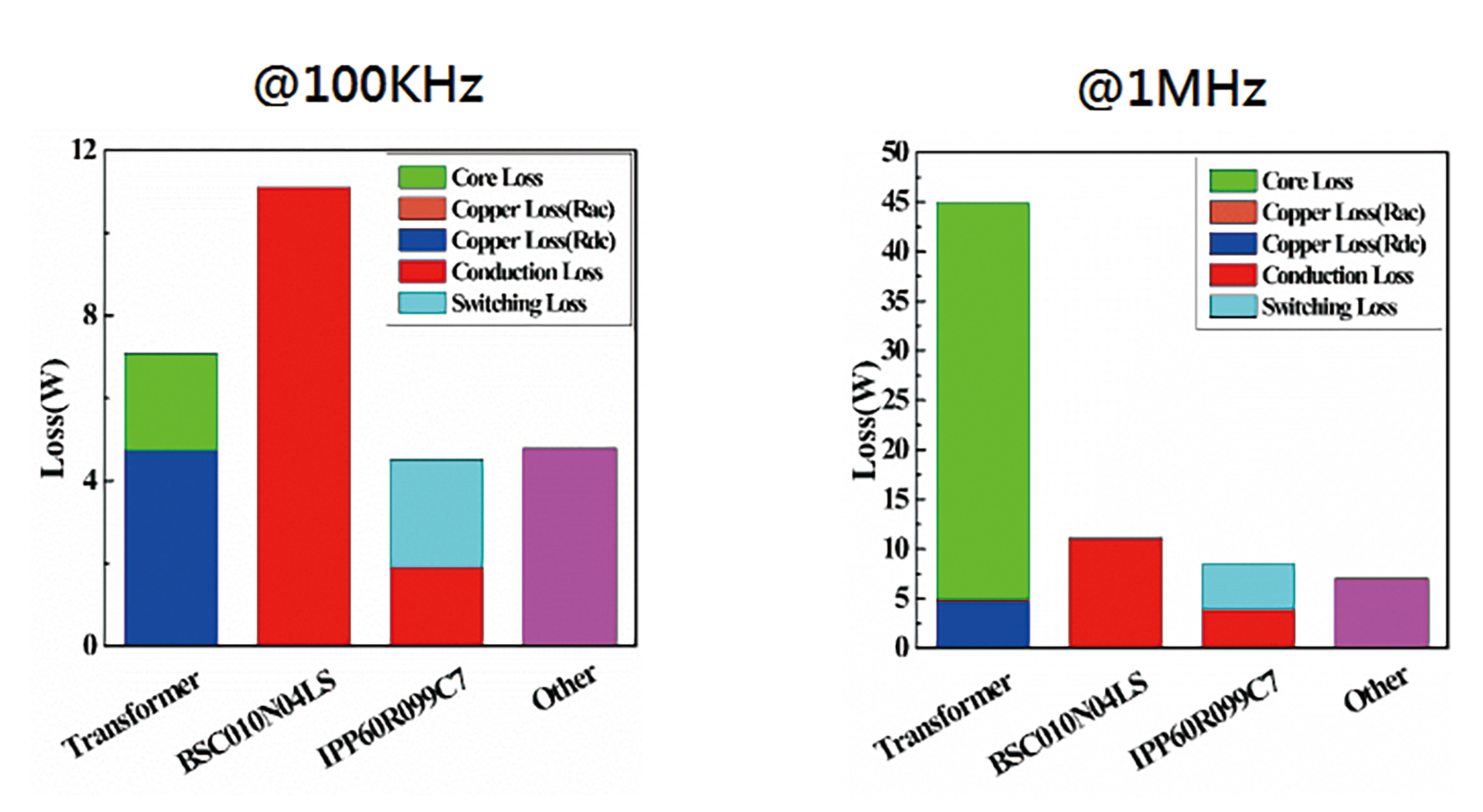

邱煌仁指出,以一個380伏特(V)輸入、12伏特輸出,功率1000瓦(W)的LLC電源轉換器為例,當開關頻率從100KHz拉高到1MHz時,變壓器上的損失(Loss)會增加37.65瓦(W),切換損失(Switching Loss)則會微幅增加2.05瓦(圖6)。由此就可看出,如何降低變壓器的損失,是電源設計工程師在拉高開關頻率前,必須設法解決的問題。

圖6 同一個LLC轉換器在100KHz與1MHz頻率下的損耗比較

圖6 同一個LLC轉換器在100KHz與1MHz頻率下的損耗比較

進一步分析變壓器上的損失,可細分成核心損失(Core Loss)與銅損(Copper Loss)兩種類型。要改善核心損失,關鍵在磁性材料的特性改良;銅損則可以藉由修改繞組(Winding)設計來抑制。

銅損的產生,主要是來自集膚效應(Skin Effect)、鄰近效應(Proximity Effect)與邊緣效應(Fringing Effect)這三個物理現象。台科大電子所的研究團隊在Ansys的Maxwell 2D工具上進行過多種模擬,最後得出以PCB線路(PCB Trace)結合全交錯繞組(Interleaved Winding),最能有效抑制集膚與鄰近效應的結論。至於邊緣效應的嚴重程度,則取決於氣隙的位置跟繞組的形狀。

最終,研究團隊實作出一款基於PCB板的Quarter-Turn變壓器設計,不僅體積小,效率峰值亦可高達97.01%。