3D IC的問世直接喚醒了業界對封裝技術的重視,且邁向立體化的架構也吸引包括通訊終端裝置、消費性電子產品等硬體製造商的興趣。但要將立體堆疊技術推上舞台,不但射頻干擾、測試與散熱問題亟須解決,更重要的是,有意在此產業發展的業者必須深入了解產業生態,方能站穩腳步。

回顧過往晶片歷史發展,從來沒有一項技術的問世如同三維晶片(3D IC)般引起市場騷動。3D IC當紅的原因並不僅在於它的立體堆疊技術--雖然這項技術確實打破了傳統封裝的範疇,但3D IC幾乎遍及半導體產業鏈的突出角色,也讓業界人士對其留下深刻印象。而系統級封裝(SiP)也因為往三度空間移動,可望帶來更多元的變化。

應用環境未臻成熟 射頻晶片3D化慢飛

|

| 圖1 愛美科事業發展經理李宗正認為,雖然可攜式通訊產品與消費性電子是推動3D IC技術起飛的重要應用,但受限於技術發展腳步,射頻元件要導入3D IC尚需時間。 |

儘管3D IC在近期掀起陣陣旋風,不過由於技術門檻與應用環境尚未成熟,預期射頻(RF)晶片大幅採用3D IC的封裝技術還要等上兩年。

比利時技術研究單位愛美科(IMEC)事業發展經理李宗正(圖1)指出,雖然3D IC具有縮短內部連接線、縮小晶片尺寸、高度整合與低廉成本等多項優勢,但由於受限於射頻訊號容易互相干擾、應用環境尚未成熟,以及業界對3D IC認識程度仍不足等多項挑戰,要看到射頻晶片走向3D IC的道路,恐怕至少還要兩年。

3D IC係採用矽穿孔(TSV)技術,讓原始矽晶圓進行穿孔,並將導電物質充填其中,而完成訊號傳遞。這項技術的好處雖可大幅降低晶片尺寸,有助縮小終端產品外型,但也因晶片間距離縮短,導致訊號干擾問題變得更加棘手。因此,李宗正認為,3D IC初期應用將聚焦在如動態隨機存取記憶體(DRAM)、快閃記憶體等類型產品,也有一定比例為互補式金屬氧化物半導體(CMOS)影像感測器(Image Sensor),以及一部分的微機電系統(MEMS)產品。

根據市調單位Yole的報告,記憶體類型產品在2009~2012年將占3D IC主要應用之五成以上;而2015年全球記憶體市場也被預期有超過25%會以3D IC為主要封裝技術(圖2)。

|

資料來源:Yole

圖2 2006~2015年3D-TSV技術應用預測 |

另外,李宗正強調,3D IC雖具多項優勢,卻仍有諸多關鍵理念須要考慮。例如,當業者開始導入3D IC時,必須審慎思考應用於記憶體或是射頻、採用客製化或是既有裸片(Die)、如何設計堆疊、採用哪類技術、如何封裝以及如何測試等議題。李宗正指出,在不同應用、技術與環境下,3D IC及其變化均極為多元,因此勢必須要慎選,才能發揮最大效用。

而除了3D IC以外,目前亦有不少業者陸續投入在射頻晶片與系統級封裝(SiP)之整合。一般認為,由於3D IC尚屬先進技術,因此多半要等到射頻元件大量普及在SiP應用後,才有向上發展的空間。

SiP時代來臨 測試/散熱瓶頸依舊

|

| 圖3 創意電子系統封裝專案總監林崇銘認為,SiP固然是大勢所趨,但現階段SiP設計流程中,還有不少細節須業界攜手合作才能突破瓶頸。 |

做為全球晶片設計服務領導廠商之一,創意電子在封裝技術的投入深度也不容小覷。從多晶片模組(Multi-chip Module, MCM)、並排式SiP封裝到堆疊式SiP封裝等技術均已研發完成,且儼然成為公司營收的一大主力。然而,在亮眼營收的背後,SiP封裝從前期裸片測試、散熱規畫到成品驗證等環節,至今仍存在眾多挑戰。

創意電子系統級封裝專案總監林崇銘(圖3)表示,從2008年起,該公司的總營收中已有高達三成和SiP有關,每四款新晶片設計中,就有一款晶片最終會以SiP的形式出貨給客戶。從普及率的觀點來看,SiP封裝無疑是相當成熟的技術,但若由技術角度觀之,SiP的整個設計環節仍處處充滿瓶頸與挑戰。

林崇銘進一步分析,SiP之所以能在近年來獲得以日系為首的客戶青睞,最大的原因之一在於其可用非常精簡的空間完成異質整合,且有助於提升訊號完整度的特性。如由於乙太網路(Ethernet)的實體(PHY)元件不適合以奈米製程實現,因此終端產品研發團隊若要導入乙太網路功能,仍需兩顆晶片。事實上,除乙太網路外,通訊應用中很多解決方案都有類似狀況,例如被動元件/射頻收發器、處理器/電源晶片及處理器/記憶體等組合,都存在這種製程無法相容或不適合整合成系統單晶片(SoC)的情況,因此可攜式產品採用SiP元件的比例已相當可觀。

然而,當封裝設計團隊進行上述異質整合設計時,不同類型元件的裸片挑選就是一個非常棘手的難題。例如射頻元件或類比元件,相關供應商仍對提供電性參數模型(SPICE Model)有非常多顧忌,因此封裝設計團隊很難預先挑選出功能正常的裸片(Known Good Die, KGD)來進行SiP封裝。對SiP封裝而言,KGD等於是上游原物料,若此一瓶頸不突破,SiP技術要用來進行數位/類比的異質整合,就必須以迂迴的方式來解決問題。

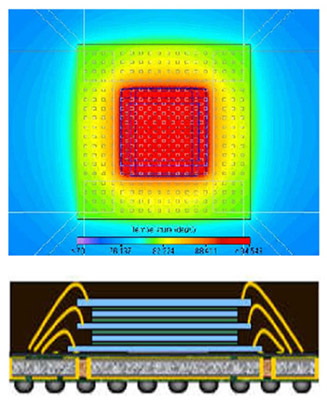

眾多晶片堆疊在一起連帶衍生的散熱問題(圖4),則是業界困擾多年的老問題,且在相關分析工具發展牛步的情況下,目前SiP封裝設計仍必須仰賴大量人工計算來土法煉鋼,才能做到散熱最佳化。例如創意便曾經接觸過一個非常複雜的SiP設計專案,光是解決散熱問題,就耗費工程團隊兩個多月時間。

|

| 圖4 晶片立體堆疊後所衍生的散熱問題,至今仍缺乏有效率的分析工具來協助工程人員改善。 |

因此林崇銘認為,SiP產業若要在現有的基礎上進一步普及,儀器、電子設計自動化(EDA)工具及晶片供應商的思維都必須與時俱進,才能加速SiP設計流程,讓SiP快速上市的優勢發揮到淋漓盡致。

廣結善緣方可縱橫SiP產業鏈

|

| 圖5 鉅景科技總經理王慶善認為,SiP封裝設計服務是一門必須廣結善緣的行業。唯有取得各方信任,才能為有設計需求的客戶提供更好的解決方案。 |

同時提供SiP封裝設計服務與多種記憶體SiP標準產品的鉅景科技則認為,SiP的應用範疇若要持續擴展,除須克服各種技術挑戰外,相關供應商的工作流程與看待SiP的心態均須有所改變。

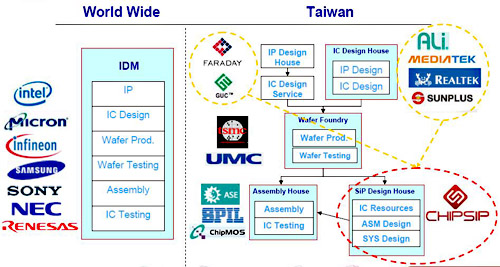

鉅景科技總經理王慶善(圖5)指出,SiP的產業鏈上下游關係相當複雜,除了少數幾家整合元件製造商(IDM)大廠有足夠資源完成所有SiP相關環節外,其他業者若想開發SiP產品,均須出面整合晶片設計、晶片設計服務、晶圓製造、封裝測試與封裝設計等各種不同族群(圖6)。這是一件相當龐大的工程,且SiP設計常須用到被視為機密的參數資訊才能完成。因此不可諱言的是,直到現在,仍有許多晶片設計業者或晶片供應商對SiP業務充滿疑慮。例如上述的電性參數模型,就是部分晶片業者始終不願開放的機密資訊。

因此,SiP事業可說是一種「信任」的事業。上游供應商必須信任封裝設計服務業者,願意提供足夠資訊,封裝設計業者才能設計出最佳化的SiP方案。鉅景近年來一直推廣專業SiP設計服務的理念,且該公司在股東結構也做出調整,因此目前已有許多晶片供應商,特別是記憶體晶片業者願意和鉅景分享資訊。

王慶善表示,目前該公司已掌握全球各主要記憶體晶片供應商的晶圓參數,且該資料庫仍在持續擴充當中,除記憶體外,如邏輯晶圓、封裝廠製程參數等,也都已經有一定掌握度。這些參數資料是鉅景最寶貴的資產之一。

|

| 圖6 台灣強調垂直分工的產業生態使SiP設計將牽涉到大量第三方供應商,讓供應商管理變得相當棘手。 |

事實上,專業SiP封裝設計服務應該被視為一個資源的整合者,甚至在某種程度上可被視為加值代理商。王慶善透露,例如近來某日系消費性電子大廠便來台探詢鉅景是否有合作意願,欲在日後的SiP設計中導入該公司所研發的嵌入式被動元件技術。也有不少系統廠客戶與晶片原廠接觸過後,再回頭找鉅景進行整合封裝設計的例子,因為晶片原廠所提供的解決方案,有時整合度還略顯不足,須要透過SiP技術提供加值,系統廠商才容易導入。

另外,嵌入式被動元件意外成為詢問焦點,顯然台灣對此有興趣的業者不在少數。因此王慶善特別針對嵌入式被動元件做進一步分析。他認為,在SiP領域,除了堆疊或併排封裝,及尚未完全成熟的TSV技術外,嵌入式被動元件也是一個值得注意的發展趨勢,特別是在無線通訊整合方面,將晶片周圍的被動元件嵌入到封裝基板中,可進一步縮小模組封裝尺寸。例如該日系廠商的嵌入式被動元件技術,現階段就應用在自家的一款知名可攜式產品上。

不過,由於成本效益的緣故,目前此技術的應用產品也只局限在該系列可攜式裝置,因此這家日商找上鉅景,是希望能透過鉅景接觸到更多潛在客戶。只是王慶善認為,嵌入式被動元件要普及化,一方面良率問題仍有待解決;另一方面投入廠商不夠多也是一大障礙。台灣的印刷電路板或封裝基板業者必須投入研發資源在嵌入式被動元件研發上,才能促使嵌入式被動元件產業鏈加速成熟。