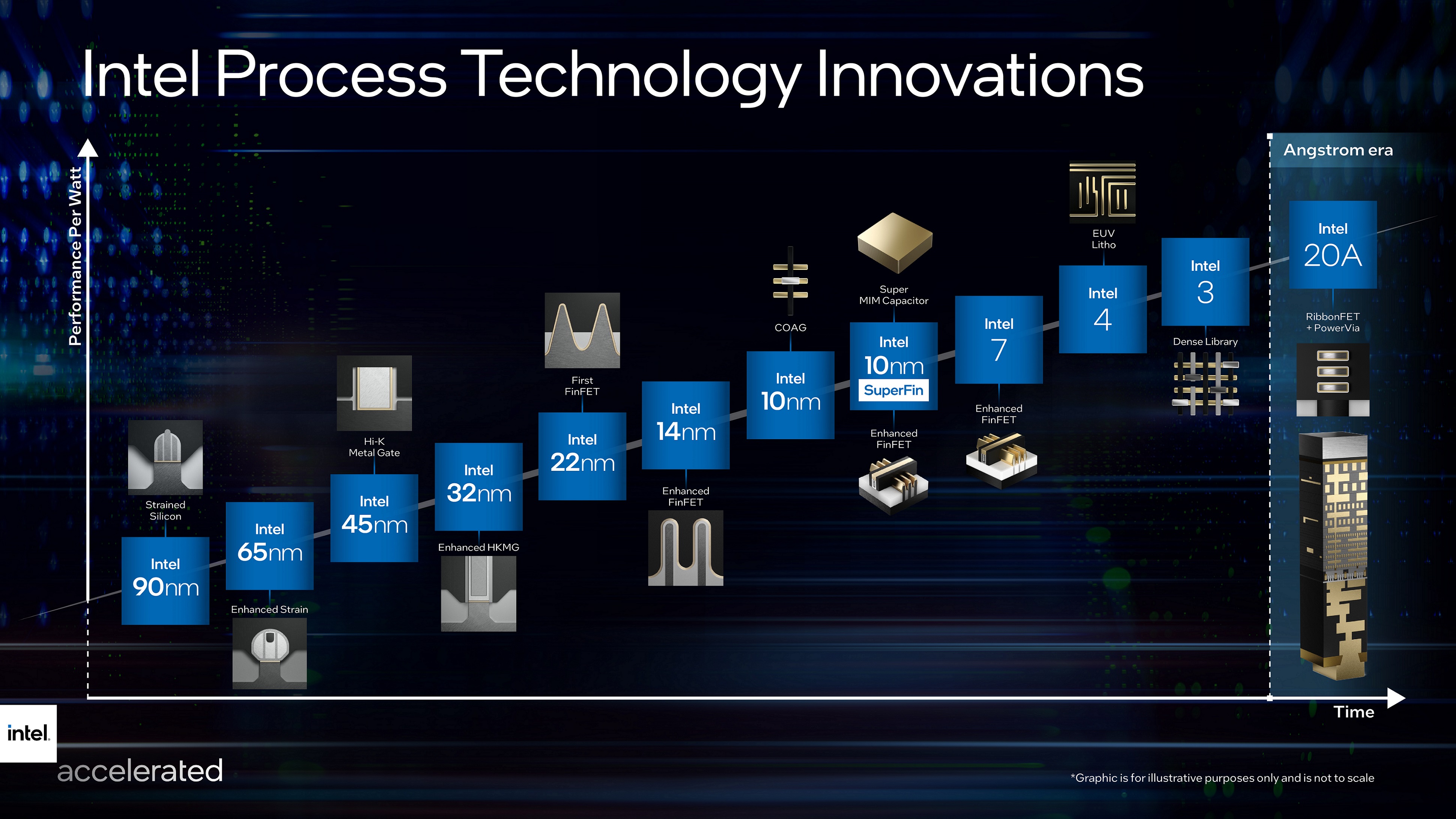

英特爾積極規劃新世代產品製程並詳盡揭露其製程與封裝技術,同時宣布一系列基礎創新,為2025年及其之後的產品注入動力。除了首次發表全新電晶體架構RibbonFET外,尚有稱作PowerVia的背部供電方案。英特爾亦強調迅速轉往下一世代EUV工具的計畫,稱之為高數值孔徑(High NA)EUV。導入Foveros Omni和Foveros Direct 3D封裝技術。同時透過新的製程命名方式,帶領半導體進入埃米(Angstrom)時代。

目前以奈米為基礎的製程節點命名方式,並不符合自1997年起採用閘極長度為準的傳統。英特爾公布其製程節點全新的命名結構,希望創造一致性的製程節點認知。

· Intel 7:植基於FinFET(鰭式場效電晶體)最佳化,相較Intel 10nm SuperFin每瓦效能可提升大約10%~15%。Intel 7將會使用在2021年的Alder Lake產品,以及2022年第一季量產的Sapphire Rapids資料中心產品。

· Intel 4:全面使用極紫外光(EUV)微影技術,透過超短波長的光,印製極小的形狀。伴隨每瓦效能提升約20%以及面積改進,Intel 4將於2022下半年準備量產,2023年開始出貨,client用戶端Meteor Lake和資料中心Granite Rapids將率先採用。

· Intel 3:進一步汲取FinFET最佳化優勢與提升EUV使用比例,以及更多的面積改進, Intel 3相較Intel 4約能夠提供18%的每瓦效能成長幅度。Intel 3將於2023下半年準備開始生產。

· Intel 20A:以RibbonFET和PowerVia這兩個技術開創埃米時代。RibbonFET為英特爾環繞式閘極(Gate All Around)電晶體的實作成果,亦將是自2011年推出FinFET後,首次全新電晶體架構。此技術於較小的面積當中堆疊多個鰭片,於相同的驅動電流提供更快的電晶體開關速度。PowerVia為背部供電,藉由移除晶圓正面供電所需迴路,以達最佳化訊號傳遞工作。Intel 20A預計將於2024年逐步量產,相當於2奈米的該製程,也預計將追上台積電的製程進度。英特爾也公布Qualcomm將採用Intel 20A製程技術。

· 2025與未來:Intel 20A之後,改良自RibbonFET的Intel 18A已進入開發階段,預計於2025年初問世,將為電晶體帶來另一次的重大性能提升。英特爾也正在定義、建立與布署下一世代的EUV工具,稱之為高數值孔徑EUV。英特爾正與ASML合作,確保這項技術能夠超越EUV。

在英特爾IDM 2.0策略之下,AWS將是第一個採用IFS封裝解決方案的客戶,該公司同時發表先進封裝藍圖規劃。

· EMIB:自2017年產品出貨開始,以首款2.5D嵌入式橋接解決方案持續引領產業。Sapphire Rapids將會是首款量產出貨,具備EMIB (embedded multi-die interconnect bridge) 的Intel® Xeon®資料中心產品。它也會是業界首款具備4個方塊晶片的裝置,提供等同於單一晶片設計的效能。Sapphire Rapids之後,下一世代的EMIB將從55微米凸點間距降至45微米。

· Foveros:汲取晶圓級封裝能力優勢,提供首款3D堆疊解決方案。Meteor Lake將會是Foveros在client用戶端產品實作的第二世代,其具備36微米凸點間距,晶片塊橫跨多種製程節點,熱設計功耗從5至125瓦。

· Foveros Omni:採用晶片與晶片連結與模組化設計,提供不受限的靈活高效能3D堆疊技術。Foveros Omni允許混合多個頂層晶片塊與多個基底晶片塊,以及橫跨多種晶圓廠節點的分拆晶片(die disaggregation)設計,預計將於2023年準備大量生產。

· Foveros Direct:為降低互連電阻,改採直接銅對銅接合技術,模糊了晶圓製造終點與封裝起點的界線。Foveros Direct能夠達成低於10微米的凸點間距,提升3D堆疊一個量級的互連密度,為原先被認為無法達成的功能性晶片分割開啟新頁。Foveros Direct是Foveros Omni的補充技術,同樣預計於2023年問世。