AI模型的參數規模來到百億、千億等級,對資料中心帶來運算壓力。為了高效運用有限資源,資料中心需要盡可能提高資料傳輸速度及記憶體使用效率,而PCIe和CXL身為伺服器元件互連的主要技術,其標準演進受到業界關注。

速度快還不夠 資料中心記憶體亟需改革

(承前文)PCIe持續在高速傳輸的路徑上穩步前進,而在考量資料中心整體運算效能提升時,除了資料速度,記憶體資源的使用效率也不容忽視。Yole Intelligence資料顯示,HPC和AI/ML模型對於記憶體容量要求高,例如自然語言處理(NLP)模型的參數量每年成長幅度便有14倍之多。面對如此龐大的資料量,資料中心勢必需要對其記憶體資源配置方式進行改革。

根據Yole Intelligence分析,由於處理器發展速度比記憶體快,過去十年記憶體和邏輯元件之間的性能差距越來越明顯;伺服器的運算核心數量增加,導致每個核心分配到的記憶體頻寬下降。與此同時,記憶體和儲存裝置之間顯著的延遲及容量落差、處理器運算時未使用的記憶體資源浪費,也是資料中心亟待解決的問題。

為了改善處理器和記憶體單元之間的資料傳輸,過去陸續出現Gen-Z、OpenCAPI、CCXL互連標準,而針對記憶體和儲存裝置之間的性能落差,則有由美光(Micron)和英特爾(Intel)主推的3D XPoint技術。然而,上述互連技術並未真正獲得廣泛採用;2022年,英特爾也繼美光之後宣布結束基於3D XPoint的Optane業務。在經歷諸多嘗試之後,資料中心記憶體終於在2019年看到希望曙光:Compute Express Link(CXL)正式誕生。

CXL前來救援 記憶體靈活存取效率UP

CXL自2019年推出採用PCIe 5.0的1.0標準,近年快速演進至採用PCIe 6.1的CXL 3.1版本,其標準組織CXL Consortium陸續與Gen-Z、OpenCAPI及CCXL宣布技術轉移,顯示資料中心記憶體漸趨統一的趨勢。CXL以CXL.io、CXL.cache及CXL.memory三類協定組合形成三種主要裝置(Type 1/2/3),優化資料中心的記憶體存取機制,被視為應對AI龐大資料量的關鍵技術。

CXL採用成熟的PCIe架構作為實體層,其中包含邏輯子區塊(Logical Sub-block)和電氣子區塊(Electrical Sub-block),邏輯子區塊起初運行PCIe模式,接著根據替代協定協商(Alternate Protocol negotiation, APN)切換至CXL模式,而電氣子區塊則持續遵循PCIe規範。透過PCIe實體層,CXL能夠將傳輸速度隨著PCIe標準演進提升,進一步提高記憶體效率。

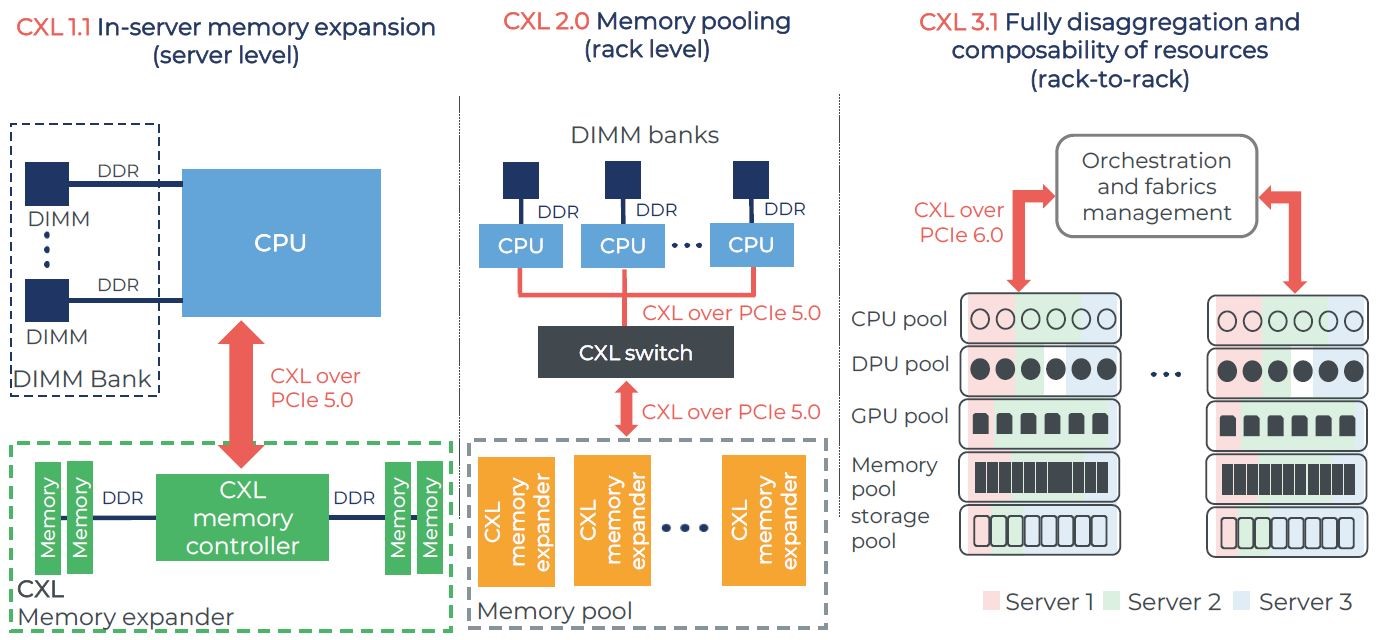

除此之外,CXL最大的特色便是將記憶體池化(Memory Pooling),實現處理器和裝置之間的記憶體資源共享,協助資料中心突破多年來的記憶體效率瓶頸。CXL 1.1首先在CPU(Host處理器)和其他CXL裝置記憶體之間建立同調(Coherent)記憶體空間,讓CPU和裝置能夠分享資源,並在相同的記憶體區域運作。如此一來,可減少資料移動需求並降低軟體堆疊的複雜度。

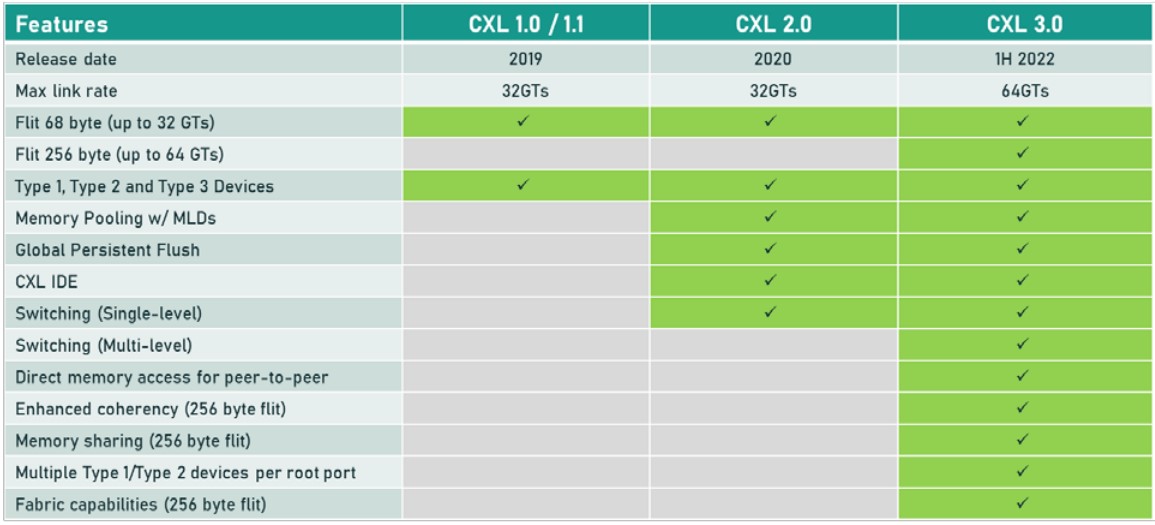

從2.0開始,CXL正式踏入記憶體池階段,支援單一層級(Single-level)交換器(Switch),在多個Host之間形成記憶體池,記憶體可以在不同伺服器之間被彈性配置(Allocated)及解除配置(Deallocated)。CXL 3.0更進一步在記憶體池化之外,導入記憶體共享(Memory Sharing)概念,使用硬體同調性(Hardware Coherency)讓CXL記憶體能夠在各個Host之間同調共享;與記憶體池不同,記憶體共享讓特定區域的記憶體可以同時被多個Host存取,同時確保每個Host都能看到最新資料。此外,CXL 3.0也支援Fabric能力,不再受限於傳統的樹狀拓撲,可以依照需求更彈性地架構運算和記憶體元素(表2)。

表2 CXL歷代標準支援項目 (圖片來源:CXL Consortium)

表2 CXL歷代標準支援項目 (圖片來源:CXL Consortium)

CXL持續朝實現整體資源最佳運用效率的目前邁進,從伺服器內部開始推動記憶體資源連接,接著於後續標準將互連範圍拓展至機架層級,甚至對傳統系統進行解耦,將有助資料中心以新架構應對多種多樣的AI/ML運算挑戰(圖3)。現在陸續可以看到記憶體、交換器、控制器業者推出支援CXL 2.0的產品,甚至開始邁向CXL 3.x。CXL整體市場蓬勃發展,根據Yole Group資料,2023年CXL市場達1,400萬美元,並預計將於2028年快速成長至160億美元。

圖3 CXL歷代標準示意圖 (圖片來源:Yole intelligence;資料來源:CXL Consortium)

圖3 CXL歷代標準示意圖 (圖片來源:Yole intelligence;資料來源:CXL Consortium)

資料需求只增不減 高速傳輸標準持續奧援

展望未來,隨著大型語言模型的應用發展,AI模型的參數規模將繼續倍數成長,資料中心需要追緊最新技術的腳步進行升級,才能滿足AI時代下的運算需求。

在資料中心提升運算效能的過程中,處理器和周邊元件的互連將影響資料處理速度,而PCIe作為穩定翻倍成長的成熟標準,將持續支援伺服器相關元件間的高速傳輸;當PCIe換代速度無法盡如人願時,CXL將以共用各元件、儲存裝置記憶體資源的方式,藉由改善記憶體效率提高運算性能。接下來,預期PCIe與CXL將攜手應對快速變化的AI應用需求。

AI巨量資料湧進資料中心 PCIe/CXL分進突破傳輸極限(1)

AI巨量資料湧進資料中心 PCIe/CXL分進突破傳輸極限(2)