過去25年,現場可編程邏輯閘陣列在無線基礎架構的開發與部署上已扮演不可或缺的角色。而當低成本的毫微微蜂巢式基地台出現,以及其能夠處理數百萬單位的預期潛能,現場可編程邏輯閘陣列也走完了它的歷程。

毫微微蜂巢式基地台(Femtocell)是為了要將基地台放入屋內,同時還可以支援單一個家庭或是大量電話用戶而設計的小尺寸基地台。有許多種部署方案,其中包含鄉村、郊區以及都會住宅環境的設定,以這些同時也被稱作是存取點基地台(Access Point Base Station)的迷你基地台加以構思。

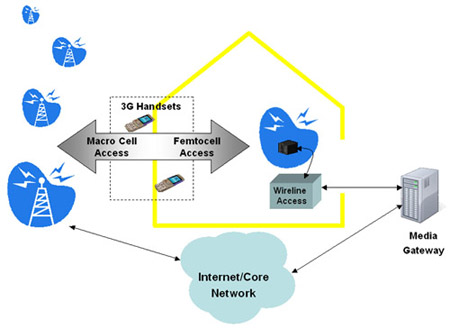

Femtocell已經準備好要成為無線基礎架構擴充 的最佳傳送工具(圖1),其原因在於可支援既有的3G行動電話,且可在本地端依據所需而加以擴充。除此之外,電信業者可將資本支出(CAPEX)成本轉移至消費者身上,並可避免回傳動作的瓶頸。由於Femtocell具備以上諸多好處,因而使得此一技術的發展飽受電信業者的關注。

|

| 圖1 Femtocell拓撲 |

利用這個經過簡化的定義可以清楚看到,Femtocell必須能夠支援如同傳統式基地台一樣高的位準以及功能方面的特點。此外,對於加值特點,例如真實的高品質聲音、較快速的資料、音樂下載中心、家用內部通話系統等的提供,家庭被視為最理想的位置。這些設置於家中的基地台具有龐大的潛能,可讓廣告商針對訂閱者傳送具有高鎖定性的訊息與活動。所有的因素都在強調建構Femtocell時對於彈性的需求,尤其是在這種最初的部署階段。

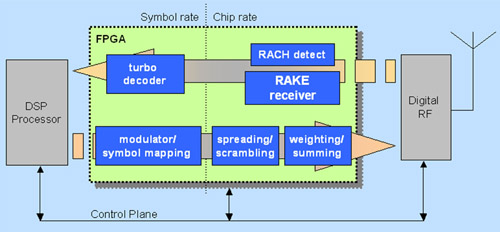

家用環境中確實可以將Femtocell的部分需求予以簡化,而為了實現這些特色,在裝置位準上會衍生出數個選項。首先,單一個Femtocell被設定為只能夠支援數量有限的使用者,而這將會大幅減少總體的系統處理需求。其次,不同於支援快速移動車輛中之終端使用者的傳統基地台,Femtocell只能夠支援在住家附近走動的人,這可大幅簡化用來找出與支援使用者的搜尋演算法則。兩項主要的差別使得Femtocell只使用少量的晶片(圖2)就能加以完成。

|

| 圖2 經過簡化的Femtocell方塊圖 |

更細微觀察這項令人振奮的全新部署架構,可以很快釐清此架構的複雜性,並且開始顯露為何FPGA仍然是成功的關鍵要素。首先,消費者會使用的回傳技術會是哪一種(FTTx、乙太網路、ATM、DSL),而這將會對Femtocell的設計造成什麼衝擊?其次,有哪些無線介面標準是必須支援的?雖然這裡大多針對3G蜂巢式網路(WCDMA)/高速封包存取(HSPA)以及分碼多重存取(CDMA)/EV-DO討論,然而在支援此標準同時,獲得大量使用的GSM技術也須要加以探討。假如全球微波存取互動介面(WiMAX)與無線區域網路(WiFi)的Femtocell設計較具有吸引力,那麼這些標準也需要受到支援嗎?同時,家中設置基地台牽涉到的某些複雜性,像是安全性、存取控制與大型基地台的干擾、分發與傳遞等都須加以解決,所有的變數突顯建構Femtocell彈性化的需要。

家庭設置Femtocell面臨成本壓力

由於預期Femtocell將設置在每個家庭中,將面臨成本最小化的壓力。完整的Femtocell目標價格,範圍介於100~200美元之間,這些價格點遠低於目前具有完整功能之旗艦級現場可編程邏輯閘陣列(FPGA)成本。

幸好,相對較新的基地台架構會在低成本的FPGA架構快速成長至相當普及化後才開始崛起,並且成長至其目前聲稱大約整體市場的25%。FPGA供應商已開發出具有嵌入式特點,像是數位訊號處理器(DSP)區塊、嵌入式記憶體,甚至犧牲部分完整特點而能夠支援無線基頻處理所需性能的高速串列器/解串列器(SERDES),還有高階FPGA等低成本的FPGA結構。

Femtocell應用領域持續發展 DSP/FPGA共生關係

無線應用領域中,FPGA以及DSP多年來一直都是協同處理的夥伴。隨著低成本、具有豐富特點的FPGA以及針對無線應用領域而特別開發之處理器出現,這種共生關係對於預期中大量Femtocell應用領域而言,仍然可以持續發展。這些將尺寸縮小的處理器具有能夠支援較小型基地台所減少之需求的必要功能,而且比起經過高度整合的同類型產品要便宜許多。表1所列舉的是處理器以及FPGA之間區隔選項的彙整。

| ◎表1 處理器及FPGA之間的區格選項的彙整 |

| 範例功能 |

實現時的選擇 |

| 基頻符碼率(Symbol Rate)的處理 |

| Turbo編碼器、Turbo解碼器、區塊插入(Block Interleave)、符碼定標(Symbol Puncturing) |

FPGA(特別是Turbo解碼器)、通訊處理器/DSP |

| 基頻晶片速率處理 |

| 耙型接收器(Rake Receiver)、高速搜尋器(High Speed Searcher)、解碼器、解展頻器(De-spreader)、調變器 |

FPGA/ASIC |

| 基頻RF介面 |

| 並聯或串聯I/O介面 |

FPGA/ASIC |

| 上轉換/下轉換 |

CIC濾波器

抽樣(Decimation)濾波器

內插(Interpolation)濾波器

數值控制振盪器 |

FPGA/ASIC

類比/混合訊號 |

當傳統的無線基礎架構被建立完成後,表1所列的許多功能就從FPGA與通訊處理器中移植到ASIC中,這個過程歷經了多年,而不使用ASIC來進行初期的部署仍是十分普遍的現象,一般預料,早期的Femtocell部署也將會依循相同的歷史軌跡。因此,有許多表中所列出的ASIC功能在初期不是以低成本的FPGA,就是以特殊規格的通訊處理器加以執行。舉例來說,基頻晶片速率處理可被分割,如此一來像是耙型接收器(Rake Receiver)、RACH偵測器、擴展(Spreading)、雜湊(Scrambling)、以及通道加權/加總等的功能,都可以從處理器上予以卸載並轉移至硬體上執行。此外,針對硬體加速的部分,像是Turbo解碼、調變、以及符碼映射之類的符碼率處理功能也是可以實行的選項。FPGA元件像是LatticeECP2M家族的成員,能夠使以硬體為基礎的解決方案,成為低成本的高度整合單一元件。藉由提供傳統、高階、具有豐富特點的功能性,如嵌入式DSP、記憶體區塊以及高速串聯介面等,以及讓系統設計工程師能夠與Femtocell市場中極具價格競爭性的價格點,前述的方式將可以實現。

耙型接收器是接收訊號品質關鍵

在無線通訊當中,耙型接收器是將已接收訊號的品質予以最佳化的關鍵要素,特別是與寬頻分碼多工(W-CDMA)有關聯時。在必須處理多重路徑介面以及訊號時強時弱的室外環境下,耙型接收器上就會需要有更多分支(Finger),以確保通話的品質,否則就得使用更為複雜的接收電路。相對的,對於在家庭環境中,具有較少對抗性與固定機動性的Femtocell而言,前述的這些需求就能予以簡化。接下來,在與實現這些特點有關的裝置位準上,就會產生出幾個選項。這些必須加以考量的架構選項中,其中一項就是減少耙型接收器所需的分支數量,因為這可以簡化其設計,更重要的是能以較低的成本予以實現。對於在特定Femtocell環境中所需的分支數量,目前還在熱烈討論中,在此只會強調彈性化、低成本、以硬體為基礎之執行方式的價值。

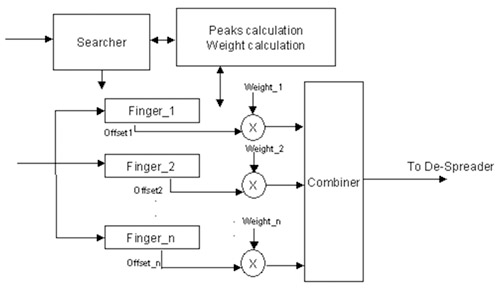

最大比率組合(MRC)是一種可將來自不同路徑的訊號能量加以組合的常用耙型接收器執行方式。此訊息用來決定應該要分配給特定使用者的分支數量,以及計算初始延遲或是分支的偏移。每一個分支都會以經過加權的小型關聯器(Correlator)方式加以執行,乘以分支的輸出,然後加以組合並提供MRC輸出。圖3中所示為此MRC的功能以及在FPGA中的執行方式。

|

| 圖3 耙型接收器架構範例 |

可編程能力成為優點及必要特性

對於特定應用積體電路(ASIC)、獨立的特定應用標準產品(ASSP)、以及FPGA其相對的優點,可以透過主要的無線基礎架構供應商進行較深入的了解。針對牽涉新興規格的應用領域,或者是需要客製化邏輯電路的情況,可編程能力對於設計工程師而言,就成為關鍵性的優點與必要特性。可編程能力讓系統設計工程師能夠設計出可以包含特定供應商之邏輯電路的單一硬體平台,同時也可用來提供多重地區的解決方案。

由於小型尺寸的基地台能夠支援主流無線手機,很明顯的Femtocell也須要能夠支援來自於3G以及其對於4G之發布(HSDPA/Adaptive Antennas/MUD/PA Linearization)的相同路徑。此外,Femtocell還會增加獨特的加值特點,此特點來自其設置於家庭環境中所獲得的優點,許多特點將會針對全球各地的特定地區加以制定,而且也還在進行定義當中。

由於以用戶端設備(CPE)為基礎的有線與無線網路會匯聚到相鄰的Femtocell中,在Femtocell回傳動作上,乙太網路將扮演關鍵性角色。

因此,選擇FPGA時的關鍵考量就是有無晶片內建的嵌入式高速乙太網路介面。最重要的是,操作者已經說明過Femtocell必須要能符合特定的成本目標才足以成功,能夠提供必要的SERDES以及可編程的邏輯電路與DSP功能,以便支援在特定價格點上之Femtocell的實現,這是早先以高階FPGA或是ASSP/FPGA之組合所無法達成的。這些低成本的FPGA包含有可編程的邏輯電路以及嵌入式特點,像是DSP區塊、嵌入式記憶體與SERDES等。對於Femtocell執行方案而言,全新的低成本元件與特別製作的處理器相互結合,將是極具吸引力的解決方案。

Femtocell是無線架構創新之示範

無線設備供應商須要仰賴FPGA實現多重的功能。Femtocell代表另一階段,也是無線架構創新的示範,此創新乃是受到現今低成本FPGA架構所提供之彈性的優點所賜。這些優點包括有快速的上市時間、適應規格變化以及將多重功能整合至單一晶片等,所有優點依然能夠支援高容量低成本部署的成本點。

(本文作者任職於萊迪思)