微電子裝置的效率及電源消耗,是電力電子應用的主要問題。工程人員每年都必須設法提高功率密度,並降低應用的耗電量,才能將最高溫度控制在規格範圍內。如此的情況使得工程人員須要持續縮小封裝,並提升效率。

傳統提升直流對直流(DC-DC)同步降壓轉換器的方法,包括透過低RDS(ON)裝置減少金屬氧化半導體場效電晶體(MOSFET)的傳導耗損,以及透過低頻率運作降低切換耗損。然而,RDS(ON)逐漸提升會降低效益,低RDS(ON)裝置則有極大的寄生電容,而無法發揮提升功率密度所需的高頻率運作。

矽晶片及封裝技術的進展,使得封裝縮小的產品需要更高的效率和更多的電量,例如德州儀器(TI)的NexFET Power Block結合這兩種技術達到更高的效能,而所占空間只有離散式MOSFET的一半。本文將說明這些新技術,並重點解說其中的效能優勢。

有效降低切換耗損

在一般的同步降壓轉換器中,MOSFET開關的主要耗損包括切換耗損、傳導耗損、本體二極體耗損和閘極驅動耗損。這些切換耗損主要是由於裝置結構內形成的寄生電容所致,而傳導耗損是裝置的電阻(RDS(ON))所導致的結果。另外,本體二極體耗損是正向電壓及反向復原(Qrr)的功能,閘極驅動耗損是由MOSFET的Qg所決定,因此寄生電容及RDS(ON)會決定裝置的效率。

|

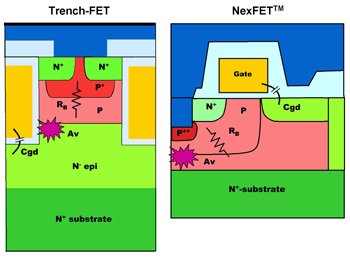

| 圖1 MOSFET結構比較 |

現今低電壓MOSFET中最常用的技術是溝槽式場效電晶體(Trench-FET)(圖1)。Trench-FET能夠達到極低的電阻,然而,大區域的溝道壁不利於縮小內部電容的體積。其中產生的高電容,促使設計人員必須在可優化效率的低運作頻率,與功率密度較佳的高頻率之間做出抉擇。

NexFET可達到類似於Trench技術的特定通導電阻,但是相關的寄生電容減少約50%。NexFET裝置採用橫向擴散金屬氧化物半導體(LDMOS),並結合垂直電流達到高電流密度。仔細查看結構(圖1)可看出閘極下方的區域,存在著源極與汲極區域的最低限度重疊,有助於縮小內部電容的體積。電容縮小之後,開關裝置所需的電荷(Qg、Qgs、Qgd)即減少,裝置開關的速度因此加快,使得MOSFET的切換耗損降低。由於驅動電路所需的電源減少,因而降低驅動器的耗損。

減少空間與寄生阻抗

|

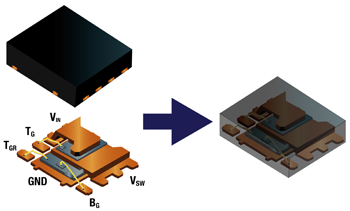

| 圖2 電源配置的橫截面圖顯示獨特的封裝方式 |

為了充分發揮一般同步降壓轉換器的效能,須將封裝中的寄生電感和電阻降至最低,而透過電源配置的創新技術即可達到如此的效果。其中,MOSFET是以兩個銅夾堆疊於接地引線框架(圖2)。最終形成的電源配置封裝具有電力電子產品業界中相當獨特的特性,能夠發揮小體積、極低寄生效應、絕佳散熱效能及穩定可靠性等四項主要功用。

為達到小體積及最低寄生效應,電源配置封裝設計採用堆疊拓撲。來源抑制矽晶片技術能夠讓高端晶粒堆疊於低端電晶體,以便透過簡單且符合成本效益的方式,實作同步降壓轉換器拓撲。

|

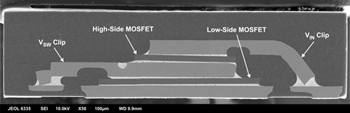

| 圖3 來源抑制技術使得MOSFET能夠予以堆疊。 |

低端晶粒接在引線框架的主墊片,可供MOSFET組的接地連接(圖3)。低端汲極透過形成裝置切換節點(VSW)的粗銅夾連接於外部。在粗銅夾頂端,一顆晶粒焊接於同樣採用來源抑制技術的高端MOSFET。最後,另一支粗銅夾將高端汲極(降壓轉換器的VIN)連接於裝置的外部接腳。閘極連接是以二條Au連接線(TG及BG)進行,TGR是IC驅動器的頂端閘極回歸。TGR是切換電壓節點偵測訊號,能夠使IC驅動是將高端MOSFET閘極適度偏壓。

達到最高效能與密度

|

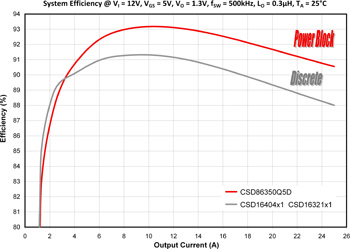

| 圖4 NexFET 5毫米×6毫米電源配置提升效率的效果明顯優於類似的離散式MOSFET。 |

來源抑制NexFET技術及堆疊晶粒封裝技術能夠大幅降低相關的寄生效應,並且讓同步降壓電源配置能夠在效能方面超越離散式MOSFET電晶體。相較於類似傳導及切換特性的兩組離散式NexFET,在25安培(A)的條件下,5毫米(mm)×6毫米電源配置(CSD86350Q5D)的效率高出2%(圖4)。效率最高可達93%以上,在25安培時達到90.7%。效能提高,表示功率耗損減少20%以上。功率耗損減少有助於提升散熱效能,並降低系統運作成本,另外也可達到更高的頻率運作,而提升功率密度。

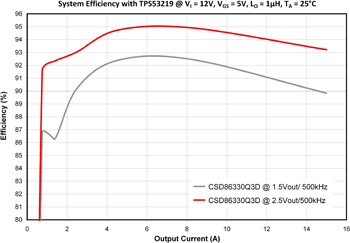

以3毫米×3毫米電源配置(CSD86330Q3D)結合TPS53219脈衝寬度調變(PWM)控制器為例,如何的組合讓僅20毫米×20毫米印刷電路板(PCB)區域就能夠達到高效能。控制器可使用D-CAP模式,因此不需要外部補償網路也能夠達到絕佳的暫態響應,可減少外部元件數,並且進一步提升負載點(POL)功率密度。

|

| 圖5 NexFET 3毫米×3毫米電源配置結合3毫米×3毫米PWM控制器達到高效率和功率密度。 |

再仔細檢視圖5的效率曲線,可看出TPS53219與3毫米×3毫米電源配置的組合以15安培輸出電流將12伏特(V)轉換為2.5伏特,效率高達93%、95%。即使輸出電壓達到1.5伏特,在15安培下測得的系統效率也達到89.8%,峰值效率可達92.5%。

除了提升效能及電路板空間比離散式MOSFET縮小50%外,NexFET Power Block也有助於加速開發。在離散式實作中,必須在連接兩組裝置時注意配置以降低電感,如今這不再是問題。

另外,接腳輸出的設計適合用來放置離散式元件,包括靠近封裝放置輸入電容,以及輸入電容與PWM控制器IC的封裝另一端,有雜訊產生切換節點的輸出電感。NexFET Power Block的接地引線框架,也有助於提升散熱效能,並降低電磁波干擾(EMI)。這些特性能夠讓設計人員在第一次使用NexFET Power Block進行設計時,就獲得成功的結果。

(本文作者任職於德州儀器)