汽車電子業界現已開始採用智慧圖像處理,來將多個攝影機採集來的資料進行同步,有效地為車輛提供「看」和「識別」周圍環境的能力。新一代圖像識別處理器(ICP),可讓智慧車輛更易實現,並為駕駛創造更安全的行車體驗。

|

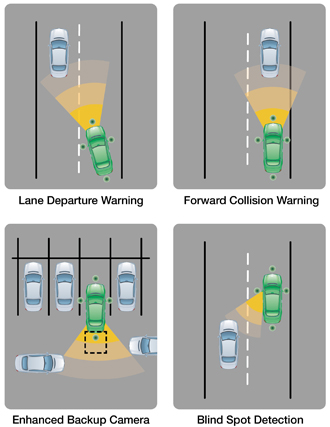

| 圖1 進階駕駛輔助系統 |

圖像識別處理器可以在智慧視覺系統中實現即時的嵌入式圖像和視訊分析相關的應用,例如具有物體檢測和圖像校正的增強智慧後視攝像頭(EBC)、車道偏離警示系統(LDW)、碰撞緩衝技術(CAS)、盲點檢測(BSD)等(圖1)。

進階駕駛輔助系統設計挑戰大

基於圖像識別的進階駕駛輔助系統設計的挑戰,在於如何設計一個平台,可持續地提供足夠的處理效能,來滿足計算密集類應用的需求,又能提供低功耗來避免散熱的問題。在提供高性價比的低成本解決方案同時,讓系統設計者設計出比較細小尺寸的封裝。這樣的智慧系統可能還須要整合圖像感測器單元與智慧攝像頭互聯(若有需要的話)。

基於此種整合了圖像處理功能的圖像感測器,所搭建出來的智慧攝像頭系統,可以被用在車內多個不同的場合,例如安裝在後保險桿做為可進行物體檢測的增強型智慧後視攝影機,可安裝在側後鏡來進行盲點檢測、安裝在後視鏡後面來進行前向的防撞檢測和車道偏離檢測,或者搭配其他的攝影機模組來實現360度環視效果。另外,這種分散式的智慧攝影機模組不會增加車輛中央控制台的負擔,更不需要額外的系統資源開銷。

市場分析報告顯示,進階駕駛員輔助系統(ADAS)應用的增加將非常迅速,若干年後不僅是在高階車輛上,甚至在更多普通低階的車輛上都會安裝這樣的應用。另外,考慮到以上提到的每個應用都需要越來越多的計算效能,需求也非常地類似,目前也有趨勢是越來越多的ADAS應用將採用同樣的硬體平台。於是,目前就出現了數位訊號處理(DSP)和現場可編程閘陣列(FPGA)的方案是否適合的問題呢?

DSP演算法執行的最大的瓶頸之一,在於須要從外部的記憶體區載入資料,才能保持對資料的讀寫存取。傳統的DSP僅提供有限的平行處理機制,而且為了滿足處理能力的需求,通常需要的主頻也越來越高。當時脈頻率提升得越來越高時,系統的功耗也會越來越大,同樣導致散發出的熱量也越來越多。

FPGA提供相對於DSP更多的平行度,但是通常編程也會變得越來越困難,而且經常必須採用一個精簡指令集運算器(RISC)對資料進行後續處理。FPGA功耗更大,封裝尺寸也更大,在系統的總體成本上也相對更高。

圖像識別的未來 有賴多核平行處理

|

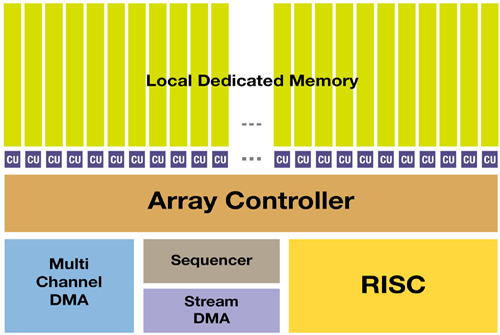

| 圖2 可編程的平行架構 |

基於多核平行處理機制的圖像識別處理器恰好彌補了DSP和FPGA的缺點。圖像識別處理器在單位面積僅毫瓦(mW)功耗的情況下提供更多的效能,並且結合低功耗、高效能、小尺寸、完整軟體發展平台等眾多特性,為開發者提供了非常有競爭力的低成本方案。

以飛思卡爾(Freescale)的圖像識別處理器為例,其核心APEX(圖2)即是一個多核的架構,由一個標準的RISC內核和一個矩陣處理引擎(APU)組成。RISC主要負責非平行的演算法的處理並且管理演算法的執行。APU則側重於處理大量平行的單指令多資料(SIMD)的矩陣運算,通常是指圖像處理和分析演算法中比較底層並且運算量大的平行運算。

除了RISC和APU外,APEX架構中配備直接記憶體存取(DMA)以便於進行高效能的資料搬移,另外還提供一個序列器來自動高效地按照順序執行作業來實現效率的最佳化。而應用層的程式則完全運行在圖像識別處理器中的第二個RISC內核,該內核是獨立運行於APEX之外。

APEX靈活可擴展,能透過增加處理單元(具備專用記憶體之計算單元的組合)的數量而線性地增加APU平行處理的能力。這樣做不僅可以在較低的時脈頻率下增強運行效能和平行作業度,而且還有利於降低功耗,減少熱量的產生。處理單元是由計算單元(CU)組成的,每個計算單元都有各自專用的記憶體。一旦圖像資料被從外部記憶體即系統記憶體取出,並按照資料流程的方式存入APU的記憶體內,則這些資料將一直存在內部記憶體中,所有的圖像作業也將是基於這些內部的記憶體資料進行作業,直到所有的處理都完成後,才會將這些資料按照資料流程的方式存回到系統記憶體中。

透過這種將記憶體與APU的執行單元進行綁定的方式,大幅減少圖像處理中對外部記憶體的存取次數,在不須要提升系統之時脈頻率的情況下,就能滿足計算效能的要求,而且對降低功耗和提升效能也有非常大的幫助。

另外,APEX模組與圖像識別處理器的其他模組耦合較弱。也就是說APEX內核的運行頻率和SoC的其他部分的運行頻率是無關的,因此系統的其他部分可以運行在更低的時脈頻率下,以便進一步節省系統的功耗。晶片採用堆疊技術將外部記憶體也封裝在內部,因此整個晶片的封裝尺寸做得更小。得利於晶片的小封裝和低功耗,整個板級設計尺寸也可以做得很小。

透過平行處理器內核,以及獨特的軟體可編程之資料流程框架,圖像識別處理器能夠輕鬆調度複雜的向量運算,並且將資料的搬移最小化。若在DSP執行同樣的作業,則將占用更高的外部資料存取頻寬,導致更高的功耗,產生更多的熱量。

|

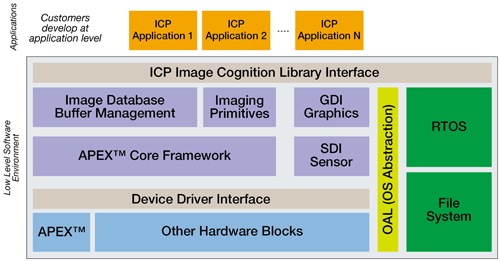

| 圖3 圖像識別處理器軟體架構 |

利用單指令多資料和軟體框架(圖3),APEX能夠達到FPGA一樣的平行度,與DSP相同的編程的靈活性。透過運用軟體框架內已經過優化的圖像識別庫中現有演算法的應用程式介面(API),APEX能夠更有效地利用演算法本身所具備的自動流水線的特性來減少演算法的複雜度,並且多核系統的均衡及多核的同步等複雜問題,對於開發者來說也被隱藏起來。APEX的可編程特性也允許使用者添加自定的演算法至現有的演算法庫中。

完整開發平台/SDK 加快專案上市時程

圖像識別處理器的高平行度,及具備高頻寬算術邏輯運算單元(ALU)的架構,確保了這樣的平台可以提供足夠的空間和效能,在同樣的硬體上可以實現多種不同的應用程式。靈活的開發平台和軟體發展套件(SDK)使客戶能夠更方便地對APEX進行程式化,來實現更具有競爭力和差異化的應用。這樣的多核平行的架構平台之所以受到開發者的青睞,不僅是因為表面可見的效能、功耗和尺寸的優勢,更是因為在將來的圖像處理應用的開發中,現有代碼的重複使用,將確保專案開發可以更快速更便捷。

(本文作者任職於飛思卡爾)