對PCIe Express 3.0(PCIe Gen3)機箱間的連接應用來說,光纖技術可提供優於同軸電纜的更佳替代選擇。

雖然串列解串列器(SerDes)轉換技術原本的設計是在個人電腦(PC)主機板上承載PCIe Gen1/Gen2匯流排訊號,但也可簡單應用到同軸電纜上做為資料中心與伺服器機箱間的互連介面。不過,銅纜的通道特性將會因PCIe Gen3更高通道頻率而大幅度劣化,因此長距離的銅線互連技術將面臨無法滿足導入8Gbit/s PCIe Gen3技術產品對成本、效能、尺寸與重量的要求。

光纖技術為高通道數PCIe Gen3介面提供非常具有吸引力的替代方案,例如大幅延長的連線距離、更小的尺寸、更輕的重量、更低的功耗、更高的效能,以及更具競爭力的成本。雖然採用光纖的PCIe Gen3互連標準尚在初期制訂階段,但市面上已有做為過渡方案的產品。

本文將介紹PCIe Gen3電氣標準,以及將目前商用光纖技術應用到低成本PCIe Gen3的挑戰,並將使用由PLX和安華高(Avago)共同開發的解決方案探討PCIe Gen3光學連線的效能、成本、模組外型、尺寸,以及製造上面臨的問題,並提出PCIe Gen3端對端光纖連線的設計架構,描述光纖解決方案如何用來支援商業PCIe應用的全64Gbit/s(雙向128Gbit/s)通訊容量。

PCIe Gen3傳輸速率翻倍成長

PCIe匯流排是提供中央處理器(CPU)與相關周邊,如繪圖顯示卡、記憶體、磁碟機和外部輸入輸入(I/O)介面卡等連接的高速串列技術,最初由英特爾(Intel)開發,目前已逐漸成為大部分桌上型電腦、工作站及高階伺服器的互連標準,同時也逐漸在一些較大型系統中成為被動式背板互連的技術。

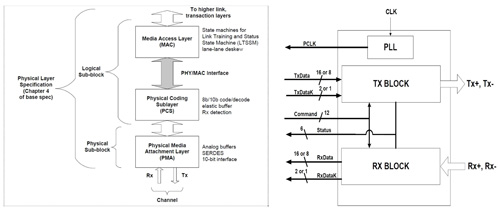

在實體層(PHY Layer)上,PCIe以兩個端點設備間單一或多個點連接實現,稱為通道(Lane),每個通道都由兩個低電壓交流耦合差動訊號對組成,形成兩個連線端點設備間的高速全雙工位元流(Bitstream)。位元流中使用8b/10b編碼方法嵌入資料時脈達到超高資料傳輸率。為滿足更高的容量,PCIe通道可經過組合形成二、四、八及三十二通道的多通道連線,並透過通道傳送封包資料。

當PCIe Gen1標準於2003年推出時,每個通道的連線速度定義為2.5Gbit/s,所採用的8b/10b線路編碼法會降低有效容量20%;PCIe Gen2則將速度加倍為5Gbit/s, 帶來三十二通道的PCIe連接器支援,達到高達160Gbit/s的總位元率。圖1所示為PCIe Gen1與Gen2實體層功能分工。

|

圖片來源:英特爾

圖1 PCIe Gen1與Gen2實體層功能分工(左)與方塊圖(右) |

2010年底定的PCIe Gen3規格則再一次將通道容量加倍,並以稱為「打散(Scrambling)」的技術取代Gen1與Gen2使用的8b/10b線路編碼方式,可降低通道負擔約1.5%。

光纖延伸PCIe介面連線距離

由於PCIe技術的高頻訊號須額外利用阻抗受控通道,減低訊號雜訊,且連線距離相對較短,因此比較適用於CPU與周邊位置接近的連接。

先不論技術上的挑戰,業界已對使用電子與光纖纜線延伸PCIe連線到機箱間應用具高度的興趣。伺服器、交換機及儲存設備間透過PCIe連接時,並不需中介傳輸通訊協議或是相關的電子零組件,除可降低系統延遲並提高傳輸效率外,使用PCIe還具降低整體系統複雜度、成本及耗電的優點。

為支援這些應用,業界也制定外部PCIe(External PCI Express, ePCIe)規格,可將PCIe Gen1的2.5Gbit/s訊號傳輸延伸到數公尺長的同軸電纜,目前已被應用於包括儲存系統、高效能運算電腦,以及其他需要高容量、多機箱系統互連的產品,例如高階影音系統等。

雖然更快的訊號會因更長的纜線導致衰減、對參考時脈抖動更為敏感,以及其他訊號完整性問題限制,無法實現較長的纜線距離,業界目前已針對ePCIe Gen2的纜線規格進行解決方案的開發,而這些問題在PCIe Gen3 8Gbit/s傳輸速率時,將更加複雜,且需更昂貴的等化與時序解決方案。事實上,光纖是PCIe Gen3晶片與纜線業者研發產品時,要使產品兼具較長連線距離與更高容量彈性設計較佳考量,促使光纖成為延伸現有PCIe匯流排到多機箱互連的銅纜替代方案。

值得注意的是,當PCIe Gen3開始量產時,光纖纜線將比銅纜解決方案耗電更少且成本更低,這些特性使採用光纖的PCIe成為目前應用於資料中心連接伺服器、交換機及其他儲存設備其他傳輸介面的良好替代方案。在整個輸出輸入連接使用PCIe還可減少甚至免除通訊協定轉換晶片的需求,從而降低整體系統成本、功耗及避免通道延遲的問題。

光纖版PCIe Gen3過渡方案現身

雖然PCIe-SIG發表使用光纖的PCIe Gen3標準還需幾年時間,但目前已有商用產品做為過渡方案,使用市面上可取得的PCIe Gen3元件及平行光收發器模組,可大幅加速特定應用光學互連產品的開發,滿足無法等待PCIe SIG提出Gen2/Gen3光纖規格的市場。

由於PCIe的媒體存取控制(MAC)與PHY層的介面非常簡單並擁有良好的文件說明,因此可非常容易使用市面上現有的PCIe Gen3交換器,或其他端點元件推動平行光收發器模組,而非PCIe Gen3規格中定義的多通道電氣SerDes驅動器。對PCIe Gen3最適合的高效能應用,較保險的做法是假設它們需要至少八個平行通道容量。

多通道端點可使用目前市面上多個供應商的產品實現,包括平行光發射/接收模組中的垂直腔表面發射雷射(Vertical Cavity Surface Emitting Laser, VCSEL)陣列。採用VCSEL技術的平行光學模組可支援多達十二個平行通道,每通道以8Gbit/s或更高速度運作,並提供150公尺的纜線。

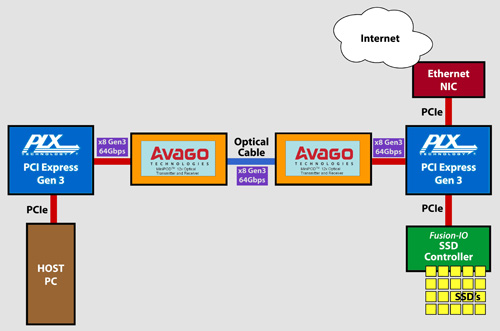

為評估使用商用產品的可行性,本文建立一個概念驗證展示系統(圖2),由內含四十八通道PCIe Gen3交換器介面卡的主控電腦組成,交換器推動十二通道10Gbit/s MiniPOD光學模組,並使用八個光學通道,另四個則未使用。

|

| 圖2 概念驗證光學PCIe連線展示系統方塊圖 |

光學PCIe連線設計挑戰多

本文架構概念驗證系統的一個主要理由是,提供使用商用零組件做為光學PCIe連線應用的可能性證明。此外,原型系統開發與測試也會找出幾個必須解決的問題,特別是在光學領域的PCIe通訊協定支援上,這些問題包括:

| ‧ |

|

| |

平行光收發器模組並未提供由PCIe發射器用來偵測連線存在的50歐姆(Ω)阻抗電氣介面。當適當的負載存在時,發射器會觸發,並以在元件接收端所偵測到的模式運作,特別的是,它會做為開始傳送一系列線路探查訊號的佇列,以便讓接收器計算並做為等化電路設定的參考,在使用標準PCIe MAC元件支援光學連線的應用中,發射器線路探查與等化功能必須被關閉。 |

| ‧ |

|

| |

PCIe電氣介面包含在無資料傳輸時將連線變成節能待機(Electrical IDLE, EIDLE)模式的功能,不過採用光纖連線時這個模式可能會造成問題,原因是收發器較長的暖機時間可能會產生線路跳動或不適當的偏壓,帶來錯誤的EIDLE偵測或跳離EIDLE狀態。 |

| ‧ |

|

| |

由於大部分光學PCIe連線並不會在相同機架間有兩端點的連接,因此本文須假設它們不會使用相同的重置或系統時脈訊號,在這些應用及本篇文章提供的範例中,並無法在連線上實現同步重置或時脈,因此端點必須能夠支援非同步時脈運作。 |

| ‧ |

|

| |

在大部分應用中,PCIe連線的遠端光學介面卡會在主系統前供電,因此遠端電路卡在設計上須能在電源啟動時進行自動重置程序,以便在主控端啟動時能完全初始化並開始進行連線。另一個做法是若作業系統能完全由使用者控制,那麼系統就能以任何順序啟動,雖然這種方式並不常見,但對客製化應用軟體在系統中定時檢查連線狀態非常需要,在這樣的組態下,在兩方系統確認完成傳輸準備後,作業系統便可啟動標準的系統列舉與程序動作。 |

| ‧ |

|

| |

目前針對同軸電纜定義的PCIe外部纜線規格,存在光學解決方案無法承載的額外訊號,例如100MHz的纜線參考時脈(RefClk)並不需要,原因是時脈可由PCIe收發器的資料串流中取得。此外包括SB_RTN單端邊頻帶訊號的回返電氣訊號接腳、CPRSNT#安裝的纜線/下傳子系統上電、CPWRON上傳子系統電源穩定通知、CWAKE#喚醒事件的電源管理訊號,以及CPERST纜線PERST#纜線平台重置等接腳,在使用光纖纜線時也無法使用。 |

選擇支援八通道組態元件

許多標準完成前的開發動作須實現商用產品尚未提供的功能,通常以使用現場可編程閘陣列(FPGA)及離散元件達成。不過在PCIe Gen3的例子上,市場上已有實現概念驗證系統所需功能的產品,雖然它們並沒有針對這類特殊應用最佳化。

選擇最適合的光學模組予本文測試應用範例,將包含幾個考量,包括通道數量、外型規格及相容性等。雖然PCIe規格允許二、四、八、十二及十六個通道,但光學模組通常以八或十二個通道組態提供,本文選擇八通道組態的原因是其經常使用於高效能PCIe 2.0的設計中,預計也會在PCIe Gen3標準受到歡迎。此外,標準化八通道PCIe端點產品也給設計團隊帶來豐富的元件選擇,其中,由於CXP與MiniPOD模組容易取得並擁有良好的效能特性,因此成為兩個最具吸引力的選擇。

MiniPOD模組機械設計較佳

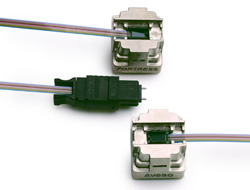

|

| 圖3 十二通道嵌入式平行光纖收發模組MiniPOD |

本文選擇MiniPOD的原因是其嵌入式平行光學組態可直接安裝到印刷電路板上,帶來更好的電氣與機械設計。MiniPOD光學模組的占用面積為18.6毫米(mm)×22毫米,並且可接受十二通道的扁平纜線或圓形纜線。扁平纜線的優點包括厚度低及模組可緊密堆疊;圓型纜線則提供更好的穩固度及更高彈性的彎折,圖3為透過扁平纜線耦合並使用業界標準MTP連接器MiniPOD光學模組。

和CXP模組使用的電路板邊緣安裝不同,MiniPOD光學模組可簡單安排在電路板中央,並提供高速驅動器連接,將承載8Gbit/s電氣訊號的電路板走線長度減到5吋,進而可將因電容表面效應造成的耗損與失真控制在最低。邊緣安裝解決方案的光學或電氣PCIe纜線可能達到12~20吋,或更長的走線長度,且還需特殊的電路板材料、發射器去強調、接受器等化及時脈數據回覆(CDR)等技術解決訊號完整性問題。

本文範例選擇四十八通道PCIe Gen3交換器做為兩個端點的PCIe控制器,原因是該元件整合用來支援光學領域運作的功能,此交換器可解決的問題,第一為交換器擁有關閉接收器偵測的功能,免除光學纜線提供50Ω阻抗的需求,在此模式,交換器透過對輸入資料串流解碼進行速度協商。

PCIe控制器第二個解決的問題是EIDLE,原因是該元件能被設定為忽略可能引發電氣待機狀態的資料串流變化,在此模式下,PCIe控制器持續追蹤提供對連線速度協商要求的特定資料符號,因此光學連線能進行列舉及連線情況、通道和速度資訊的通訊,達到完全運作頻寬。

不過由於此交換器經過修改的EIDLE功能無法允許進入或跳出動態電源管理(Active State Power Management, ASPM)狀態,因此還是存在一個小問題,但可透過實體上解除並重新啟動動作連接來初始化連線的維持能力加以解決,然而暫存器管理,如資源重新配置、BAR編程、端點的可能註冊重新編程及訊息遮蔽等就需另外的處理常式。

第三個可由PCIe控制器解決的問題是,交換器支援資料回覆用的非同步時脈模式,允許PCIe光學連線的兩端能夠獨立運作。不過這個非同步模式將不支援用來降低印刷電路板上承載PCIe訊號走線輻射電磁干擾的系統展頻時脈(Spread Spectrum Clocking, SSC)。

利用收發器/光纖控制器實作光纖版PCIe

本文提出的概念驗證展示的電路板(圖4)包含內建四十八通道PCIe Gen3交換器介面卡的主控電腦,以及一個搭配交換器的光發射器與接收器模組子板,在光學連線的另一端,另一個包含光收發器與接收器模組的交換器介面卡位於電路板上,藉以提供快速周邊,如固態硬碟驅動及乙太網路(Ethernet)HBA卡的輸出與資料整合。

|

| 圖4 搭配MiniPOD模組的介面卡 |

實體連線的每一端都使用PCIe Gen3交換器晶片進行終端,包含時脈/資料回覆以及每個高速連接埠的發射/接收等化。由於交換器晶片的收發器選用非同步模式運作,因此在光學模組中並不須進行時脈與資料回覆,可進一步保留PCIe的低延遲優勢。MiniPOD光學模組在電路板中央位置的設計,電路板走線較短,也可讓交換器晶片的Tx與Rx訊號直接與光學模組介接,因此只須在兩者間加入交流耦合。

實現30公尺光纖PCIe Gen3纜線

上述的實作電路板成功實現在OM3的低成本多模光纖上,實現超過30公尺的PCIe Gen3八通道纜線。這個光纖纜線支援非同步運作(無原生SSC,但提供SSC隔離)、僅L0動作狀態(受控作業系統的連線啟動與結束控制)、PCIe普通連線速度協商與PCIe標準連線寬度安排功能。

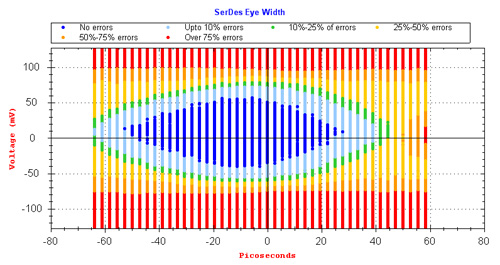

但礙於先前所討論的技術問題,此一光纖纜線目前並無法具備PCIe動態電源管理、帶內同步重置(僅支援帶外獨立重置)功能。由圖5眼圖可說明接收器驅動30公尺纜線時,擁有良好的訊號完整性及無錯誤的資料回覆。

|

| 圖5 PCIe Gen3交換器在30公尺光纖資料傳輸眼圖 |

在本文實作範例中,MiniPOD光學模組可支援PCIe Gen3以每通道8.0Gbit/s的速度運作,但實際上可支援1G?10.3125 Gbit/s的寬廣傳輸速率,因此這些光學元件可在5.0Gbit/s的PCIe Gen2及2.5Gbit/s的PCIe Gen1運作,不須更改組態也不會犧牲效能。此一傳輸速率範圍不僅可讓工程師加速實現PCIe Gen3光纖纜線連接,也可做為未來特定應用產品多重速率光學連線向後相容的基礎。

(本文作者任職於安華高)