5G新無線電(NR)網路的設計目的是與現有網路實現多年共存。在世界各地,營運商已投資數十億美元建設2G/3G/4G網路,用於無線電設備和選址。因此,營運商有強烈意願在5G網路建設中繼續利用現有的基礎設施,加快5G網路的部署速度,同時降低相關成本,這包括共用現有的4G核心網路、回傳擴充容量、在現有的無線電塔上擴建。

在多部無線電彼此接近的共置部署下,5G新無線電必須能夠在現有無線電產生的高功率干擾下正常執行且不干擾自身。

5G新無線電可以與多種不同類型的現有無線電共置,其中包括下列無線電存取技術(RAT),如5GNR分時雙工(TDD)、5G分頻雙工(FDD);4G長期演進計畫(LTE) TDD、4G LTE FDD;3G、2G RAT,如GSM、UMTS、CDMA等。

例如,一部5GNR TDD基地台收發器(BTS)可以與另一部5GNR FDD BTS共置,或者一部5GNR TDD BTS可以與一部4G TDD共置。共置的無線電在收發時時段可同步,也可不同步。

在接近現有無線電布置時,5G無線電設計上應注意避免向相鄰無線電的接收頻段(UL)發送過大功率。此外,5G無線電的接收器必須能承受來自相鄰無線電的超強輸入功率,同時也能從使用者設備(UE)接收超低功率訊號。

3GPP對共置的要求

為了使共置部署可行,3GPP TSG RAN4工作組已在BTS無線電規格[1]中發布對5G無線電共置的進一步要求。表格6.6.5.2.4-1中規定了在發送方向時對1-C型和1-H型5G NR BTS共置的每個BTS頻段的最大輸出功率限值的規格。

其中,1-C型是執行在FR1上的NR基地台,其要求只包括在單一天線連接器上定義的執行要求[1]。1-H型是執行在FR1上的NR基地台,其要求包括在單一收發器陣列邊界(TAB)連接器上定義的執行要求以及針對無線覆蓋功能(RIB)定義的無線傳播效能(OTA)要求[1]。而表1列出的是共置使用的前十大無線頻段。

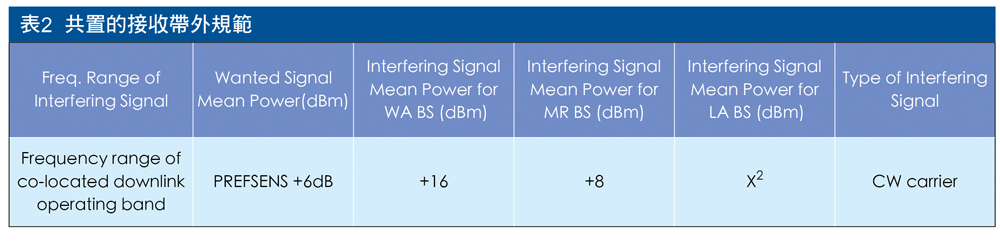

例如,當5GNR BTS與一個執行在PCS1900頻段上的廣域基地台共置,那麼其發送器輸出功率在1,850MHz到1,910MHz頻率範圍上任何時候都不得超過-98dBm/100kHz。這是表1中規定的基本限值。對於擁有許多天線埠的mMIMO系統還有細化規定。在接收方向,5G接收器必須符合表2規定的動態範圍。具體來說,對於廣域基地台,當接收器的連接器上出現+16dBm帶外連續波(CW)訊號時,接收靈敏度下降幅度不得超過6dB。

雖然這是3GPP的合規規範,但大多數網路營運商傾向於5G接收器的靈敏度完全不下降。與發送方向一樣,這些規範對共置部署的要求比非共置部署的要求要嚴格得多。

這些共置要求的具體涵義,將從濾波需求和處理大動態範圍對接收器架構設計的影響兩個角度進行探討,具體將以近期在美國拍賣的C頻段為例進行分析。C頻段頻率範圍從3,700MHz到3,980MHz。透過此例可以看出,如果採用直接射頻(RF)取樣技術取代直接轉換收發器(RFIC),這些共置要求不會產生任何嚴重的追加濾波要求。

C頻段範例設計要求

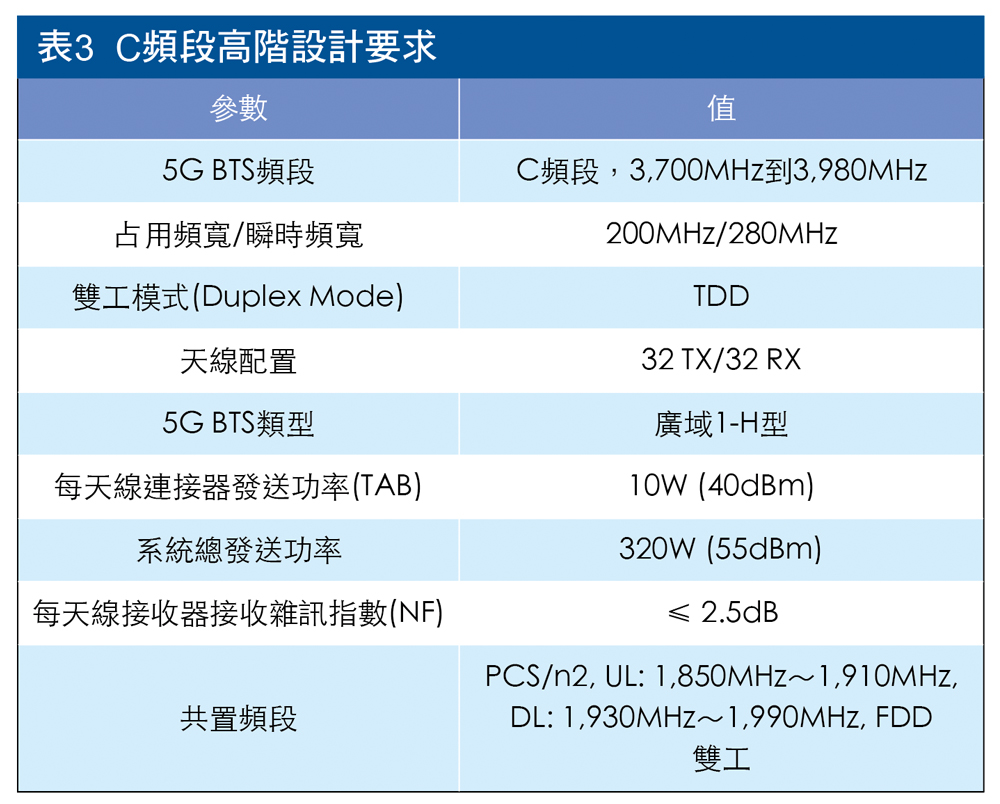

5G網路和中頻段頻譜(美國的CBRS頻段和C頻段)對於新型無線電單元(RU)的外形尺寸提出嚴格的要求。特別是,擁有32到64個天線的mMIMO系統有望大幅提高BTS在中頻段的容量和覆蓋範圍。這些mMIMO面板在美國的部署方法很可能是與現有的PCS頻段無線電或4G/5G n2頻段無線電共置。這兩種無線電的下行鏈路(DL)頻率都是1,930MHz到1,990MHz,上行鏈路(UL)頻率都是1,850MHz到1,910MHz。PCS/n2頻段是本案例的研究重點,因為該頻段訊號產生的二階諧波失真(HD2)和二階互調(IMD2)失真直接落在新的C頻段(3,700MHz到3,980MHz)內。UMTS/n1(2,100MHz)和700M/800M等其他共置頻段一般更容易設計,並且分析方法也一樣。

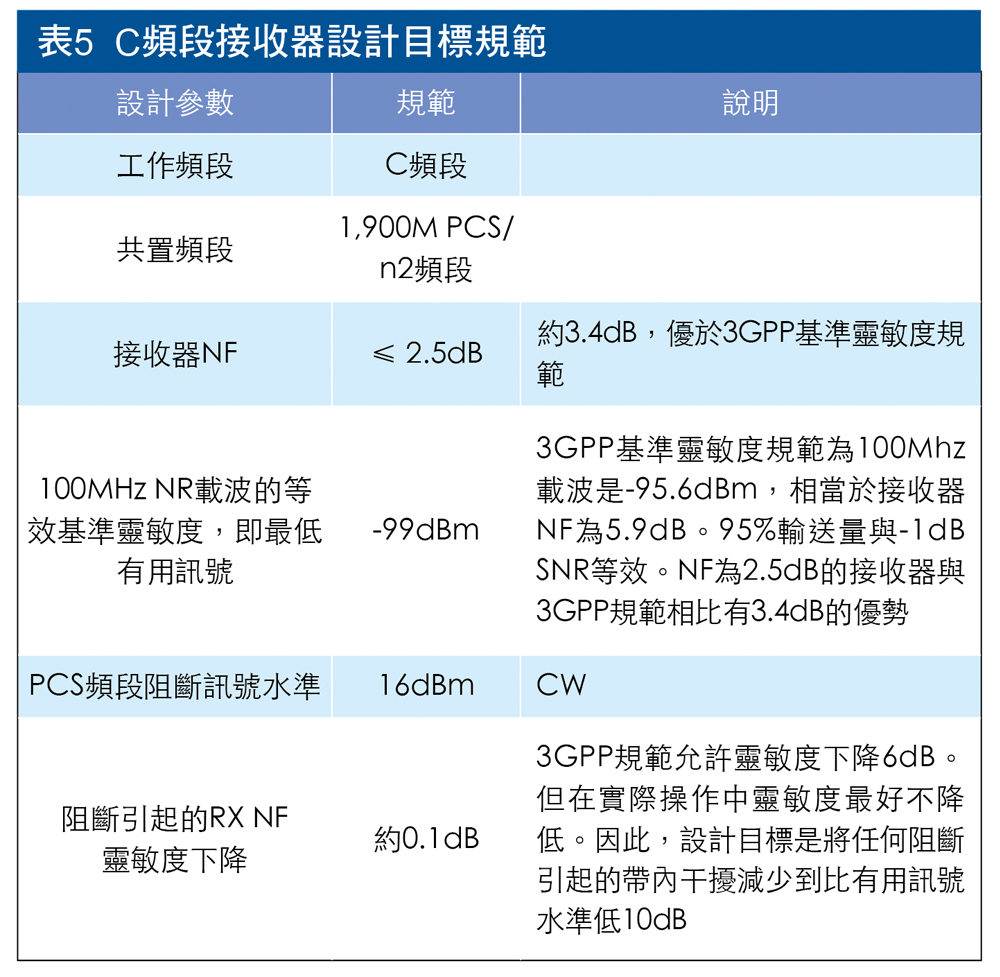

表3是針對C頻段系統的高層次設計要求的總結。

本文的分析主要聚焦於以上提到的共置要求。其他3GPP BTS要求(如TX SEM、RX窄頻帶阻塞等)未在本文裡直接探討,因為這些要求不涉及具體的共置考慮因素。

了解發送器的影響

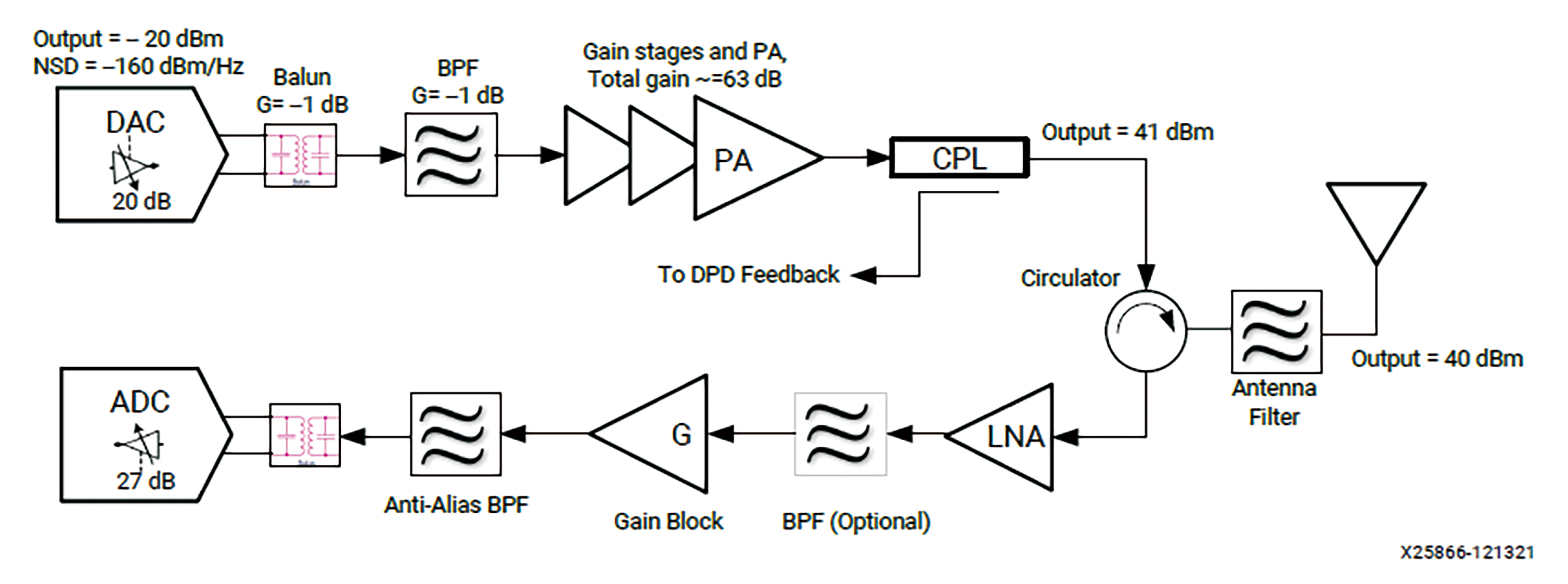

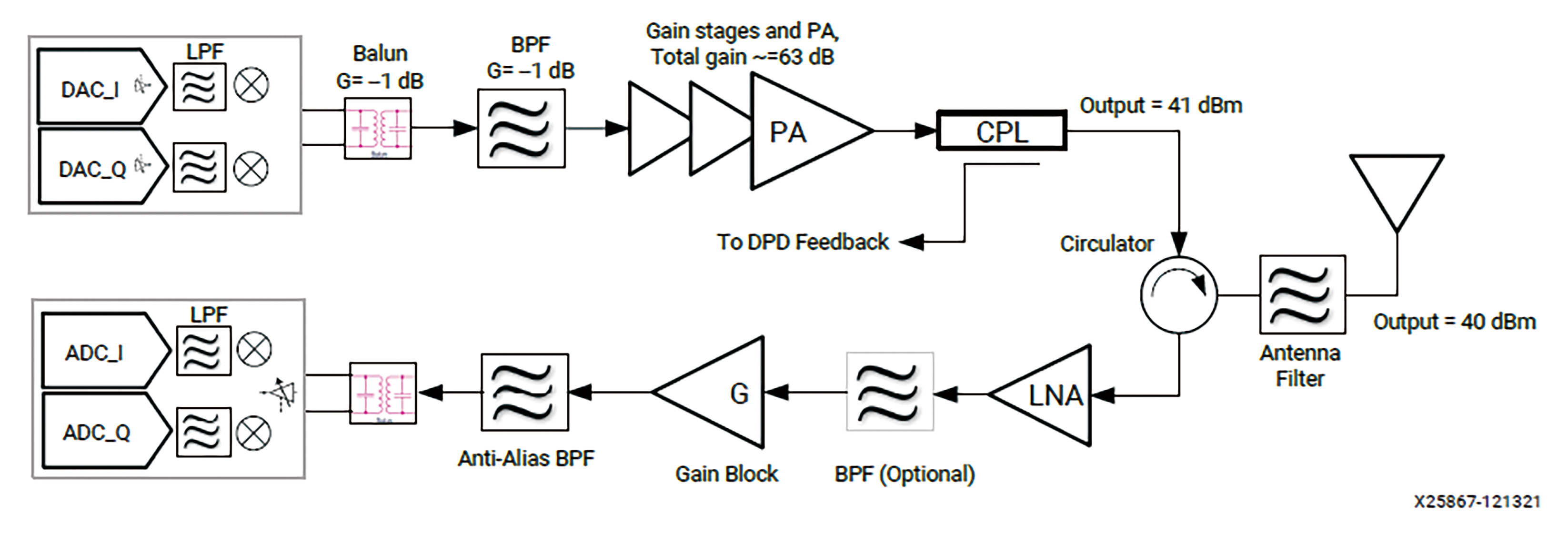

圖1和圖2分別體現採用直接RF轉換架構和ZIF(零中頻)轉換架構的收發器的典型RF訊號流程。兩種架構的RF元件十分相似,收發器的整體效能很大程度上取決於資料轉換器的動態範圍和損耗。除了常見的資料轉換器非線性諧波失真外,損耗也可能包括轉換器假頻產物、直流偏移和IQ失衡產生的影像。

圖1 採用RF取樣資料轉換器的典型收發器RF流程

圖1 採用RF取樣資料轉換器的典型收發器RF流程

圖2 採用零IF架構的典型收發器RF流程

圖2 採用零IF架構的典型收發器RF流程

對發送器的共置要求相當直接。根據表1,在發送方向設計必須確保1,850MHz到1,910MHz頻段上輸出功率密度小於-98dBm/100kHz。因為這是一個廣域1-H型BTS,可能裝配32個有效發送器,它必須符合[1]6.6.5.4細則對1-H型BTS的要求。具體而言,它必須考慮一個以上的發送天線的輻射。根據合規要求的第二項標準,輻射限值的運算是:

-98dBm/100kHz-10log10(8)= -107dBm/100kHz

對數項中的值8表示收發器陣列邊界(TAB)連接器發送最小單元組中統計的TAB連接器的數量[1]。

前圖中所示無線電架構裡的天線濾波器要承擔滿足這個帶外輻射要求的主要責任。接在DAC和巴倫輸出之後的帶通濾波器(BPF)能帶來幫助,但最多只能將PCS頻段雜訊濾除到低於-174dBm/Hz的熱雜訊水準。因為DAC輸出處的雜訊譜密度(NSD)大致在-160dBm/Hz,所以任何具備合理抑制效能的BPF都有效。廉價濾波器如採用0603封裝的Johanson 3750BP14D0900[2]或類似產品會是理想選擇。這類濾波器在PCS頻段中可抑制大於50dB。

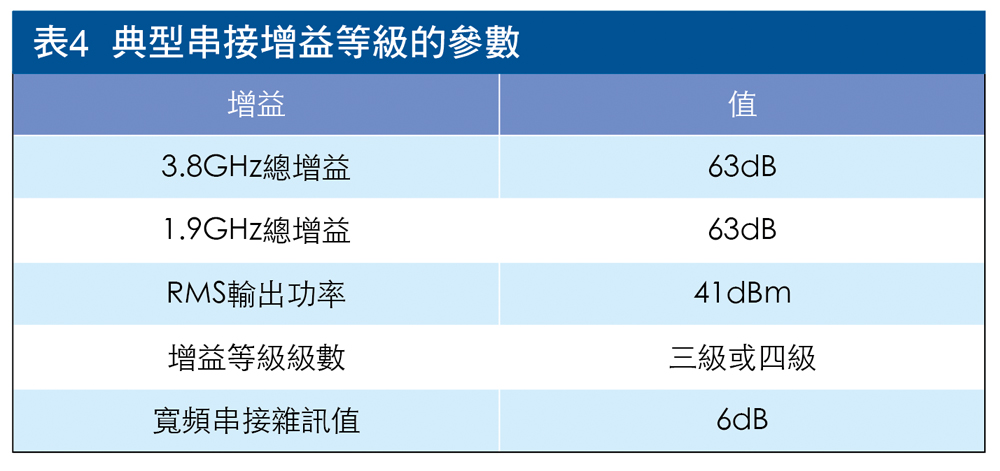

TX串接增益等級的典型值可透過商業管道獲取,具體如表4所示。

為具有普遍性,假設放大器級的總增益在1.9GHz和3.8GHz時相同,因為大多數低功率增益區塊在1.9GHz時的增益大於3.8GHz。這種情況恰與最終的功率放大器的情況相反。循環器後1.9GHz上的輸出雜訊水準(IL =-0.3dB)是:

-174dBm/Hz + 6dB雜訊值 + 62.7dB增益 = -105.3dBm/Hz或55.3dBm/100kHz

為了用10dB的設計餘裕滿足-107dBm/100kHz的要求,天線濾波器需要在PCS頻段上提供62dB (-55.3 - (-107) + 10)的抑制。由於PCS頻段距離C頻段的低端有1.8GHz,因此這種程度的抑制不是很難實現。商用天線濾波器的典型抑制值在75dB左右。與共置要求相比,天線濾波器的成本和複雜度受近載波工作頻段有害輻射(OBUE)的影響往往更大。

分析接收器的影響

共置要求對上行鏈路接收器設計的影響更為顯著,因為需要處理嚴重增大的輸入訊號動態範圍。訊號等級可以低至3GPP規定的接收基準靈敏度水準[1],高至來自共置PCS BTS的16dBm CW。3GPP規範允許在這種部署場景下將接收器靈敏度調低6dB。不過,在實踐中,透過正確的設計選擇可以避免調低靈敏度。此外,3GPP規範將CW視為需要阻斷的訊號,但實際部署中需要阻斷的訊號也可能是無線載波,如RMS功率相似、有多個發送載波的GSM、WCDMA、LTE或NR載波。

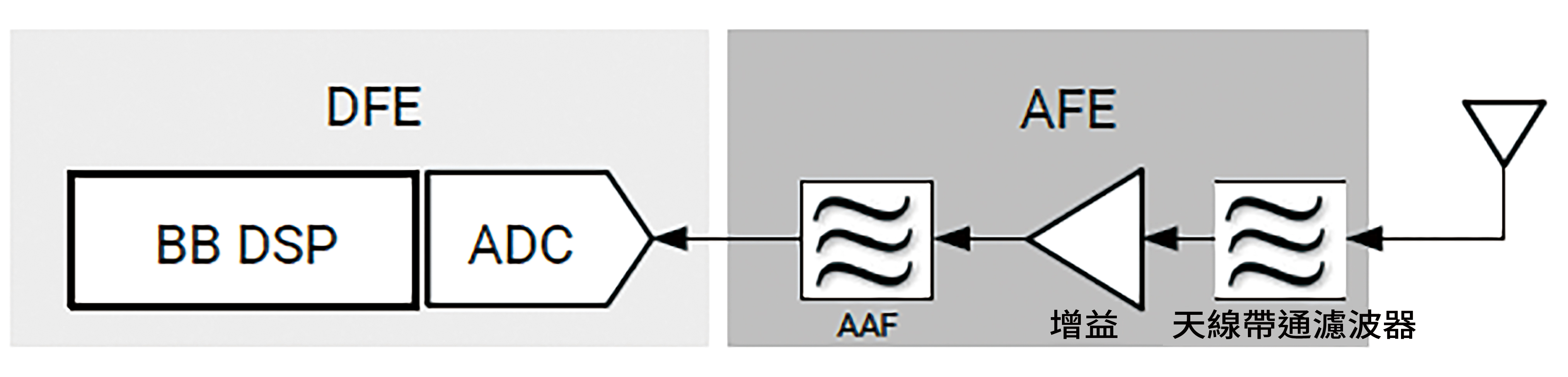

圖3總結採用RF取樣架構或ZIF架構的接收器高階原理圖。類比前端(AFE)由RF流程構成,數位前端(DFE)由類比數位轉換器(ADC)和基頻DSP處理區塊構成。AFE主要由濾波器和放大器構成。總增益一般在25dB到40dB,且能在一定範圍內調節,以實現所需的2.5dB系統雜訊值,同時滿足3GPP規範的帶內阻斷要求[1]。要提供如此高的增益,通常需要兩級放大器。兩級放大器可以是兩個單獨元件,也可以是單一封裝的元件,比如瑞薩(Renesas)供貨的F0473B或Qorvo供貨的QPB9348。

圖3 接收器高階原理圖

圖3 接收器高階原理圖

共置部署下的接收器設計目標是濾除這16dBm干擾和AFE中主動元件產生的任何非線性產物,使它們的水準在正交分頻多工(OFDM)符號解調前下降到遠小於有用訊號的最低水準。在這種情況下,有用訊號最低功率就是系統的目標基準靈敏度水準。透過在接收器鏈路裡綜合運用各種濾波器可實現濾波,這些濾波器包括天線BPF、選配BPF(參見圖1和圖2)、抗混疊濾波器以及DFE基頻DSP中的ADC頻段選擇數位降頻轉換器(DDC)和載波選擇DDC。每個濾波器等級的用途略有不同,抑制需求取決於元件選擇和接收器架構。

設計方法說明

接著,概述處理16dBm阻斷訊號的一般設計方法。

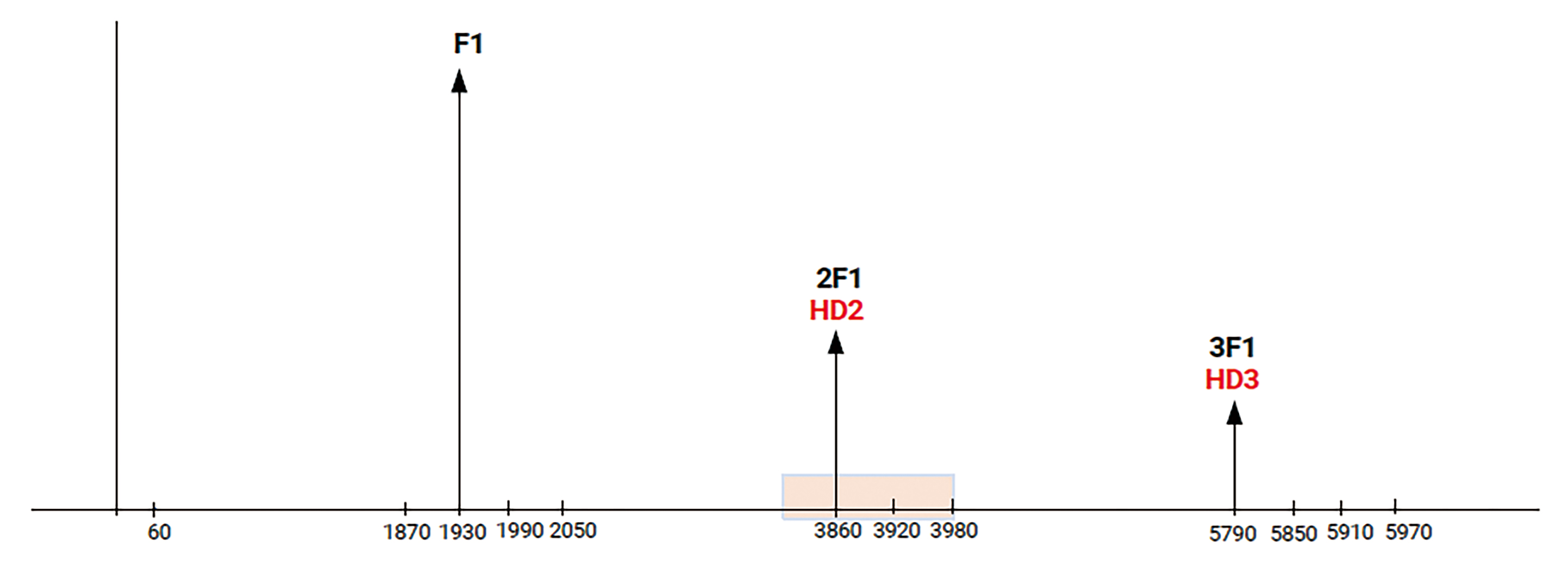

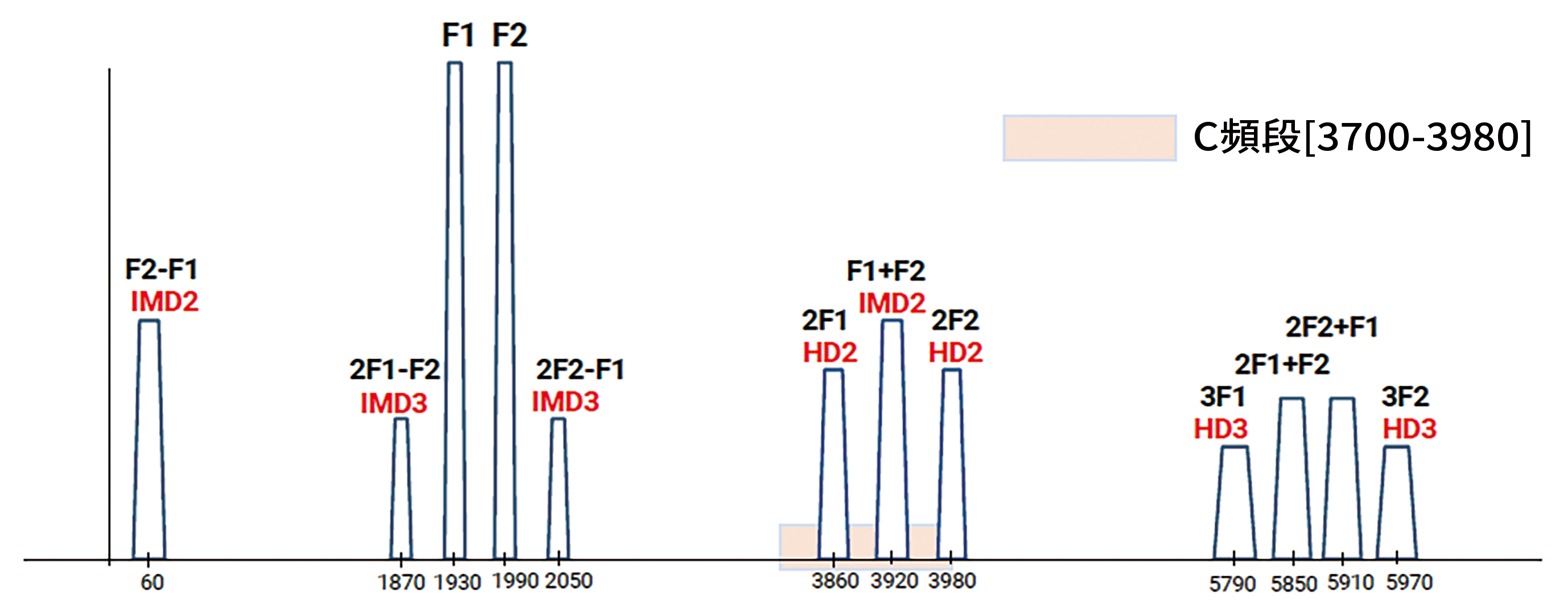

首先,天線BPF必須將阻斷訊號濾除到如下水準:一、不會導致AFE的第一增益等級(LNA)出現飽和/過度驅動現象;二、阻斷導致增益等級產生的HD2和IMD2產物遠低於有用訊號的功率,進而滿足3GPP要求的95%輸送量。如圖4和圖5所示,PCS頻段中訊號的HD2和IMD2產物直接落在C頻段上。儘管3GPP規範只採用CW阻斷的形式,但分析中也應該考慮多載波場景,因為產生的IMD2產物通常比HD2產物高6dB。這在對LNA的效能測試中可以看出,如圖6所示。

圖4 PCS頻段中連續波的HD2和HD3產物

圖4 PCS頻段中連續波的HD2和HD3產物

圖5 PCS頻段中兩個無線載波的諧波產物

圖5 PCS頻段中兩個無線載波的諧波產物

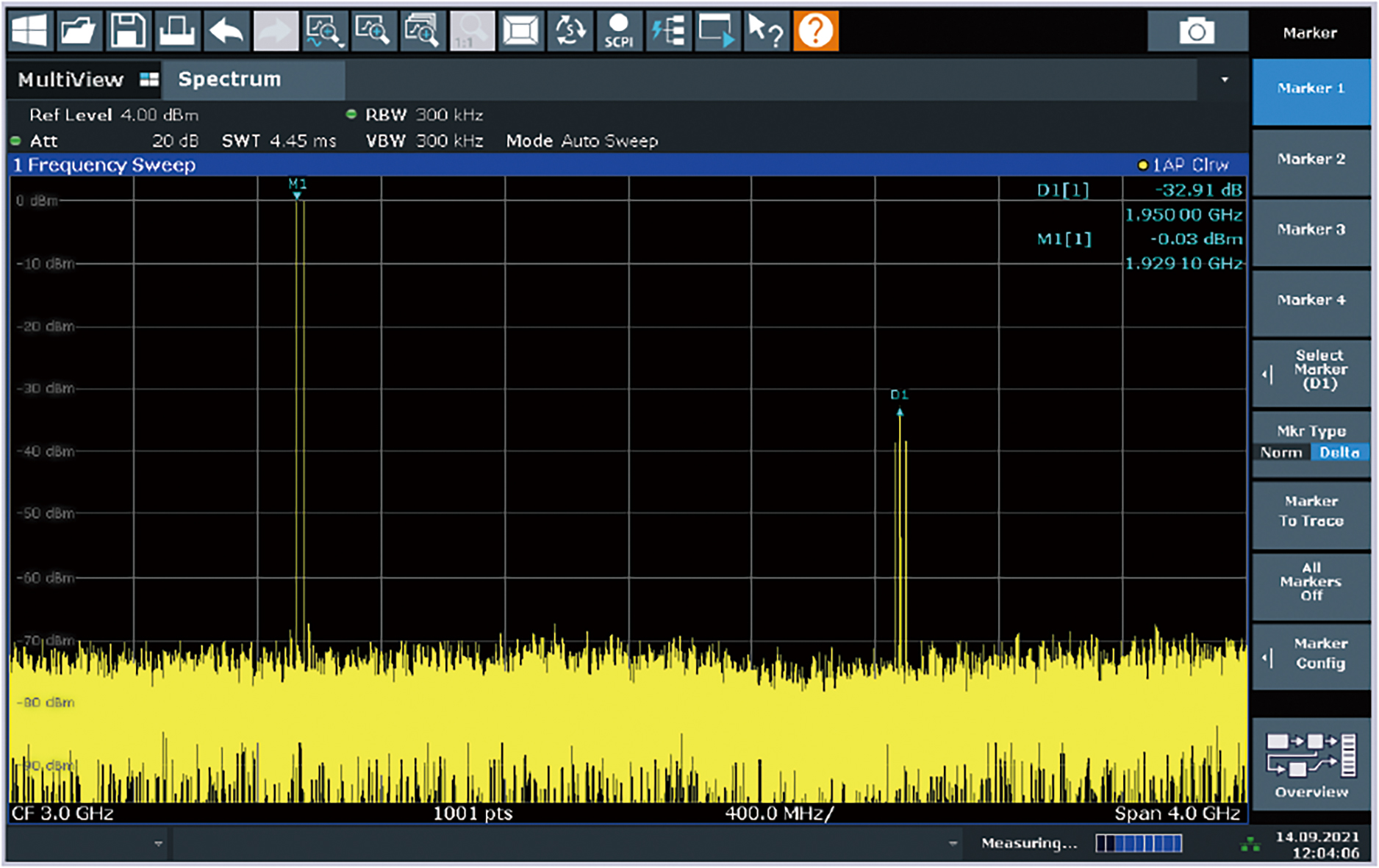

圖6 Qorvo QPL9058 (VDD=5.0V) LNA在0dBm輸出下的實際IMD2/HD2測量5VDD下,OIP2 = 33dBm;3.3VDD下,OIP2 = 29dBm。

圖6 Qorvo QPL9058 (VDD=5.0V) LNA在0dBm輸出下的實際IMD2/HD2測量5VDD下,OIP2 = 33dBm;3.3VDD下,OIP2 = 29dBm。

有關兩個增益等級間的選配BPF功能的具體介紹如下所示:

圖1和圖2所示的選配BPF功能是在天線濾波器抑制不足,無法防止第二個放大器產生可降低接收器靈敏度的IMD2/HD2產物時,強化對阻斷訊號的濾波。另外,BPF的成本和尺寸基本可以忽略不計,可以用來放寬滿足天線濾波器的要求,進而降低系統的成本與重量。和TX流程一樣,採用0603封裝的Johanson 3750BP14D0900[2]是理想選擇。

此外,RF取樣和ZIF接收器都需要抗鋸齒BPF,以獲得最佳系統NF。這個濾波器的作用包括:一、強化對阻塞訊號的濾波,避免它使ADC輸入飽和/過度驅動;二、提供對阻塞訊號的最後一級濾波,這樣即使阻塞訊號的ADC假頻落在有用的C頻段上,它也低於有用訊號,避免降低靈敏度。這個用途所需的濾波器抑制量通常較大。對於方便採用的2949.12 MSPS RF-ADC取樣速率,這屬於常見情況。然而,諸如Zynq UltraScale+ RFSoC DFE等元件(在5G方面最佳化更深入),在不利情況下向設計人員提供更豐富的頻率規畫選擇,消除對高抑制濾波的需要;三、提供對帶外雜訊和寄生訊號的濾波,避免其在ADC輸出的第一奈奎斯特區域產生假頻/折疊;四、對於ZIF接收器,這種抗鋸齒BPF也充當解調器中複雜混頻器之前的清除濾波器。現今的ZIF RFIC通常配備主動混頻器和增益等級,為ADC輸入資料。混頻器產生的高電平M×N乘積會降低接收器的靈敏度。

數位濾波器的用途說明如下:RFSoC DFE等先進元件沿資料路徑布置硬化的低功耗數位濾波器,進一步濾除干擾訊號的殘留。借助GHz等級的奈奎斯特頻寬和靈活的頻率規畫,設計人員能夠將阻斷訊號的假頻移出C頻段。在這種情況下,可使用數位濾波器在符號解調器前濾除阻斷訊號,簡化類比濾波。

採用Zynq UltraScale+ RFSoC DFE實現的接收器設計範例

在這個接收器設計範例中,為實現表5中對C頻段共置部署規定的設計目標,可將標準的目錄元件與Zynq UltraScale+ RFSoC DFE配合使用。這裡也對每種濾波器進行詳細分析。與其他頻段的共置部署可以採用相似方法進行分析。總之,接收器必須能夠在PCS頻段存在16dBm CW阻斷的情況下,接收-99dBm的NR 100MHz訊號。因此,任何阻斷引發的帶內干擾必須小於等於-109dBm,這樣才能獲得10dB或更佳的SIR。這裡補充說明一下,若要實現有用訊號的-99dBm目標,需要優於3GPP規範9.4dB(6dB靈敏度下降餘量,優於基準靈敏度3.4dB)。

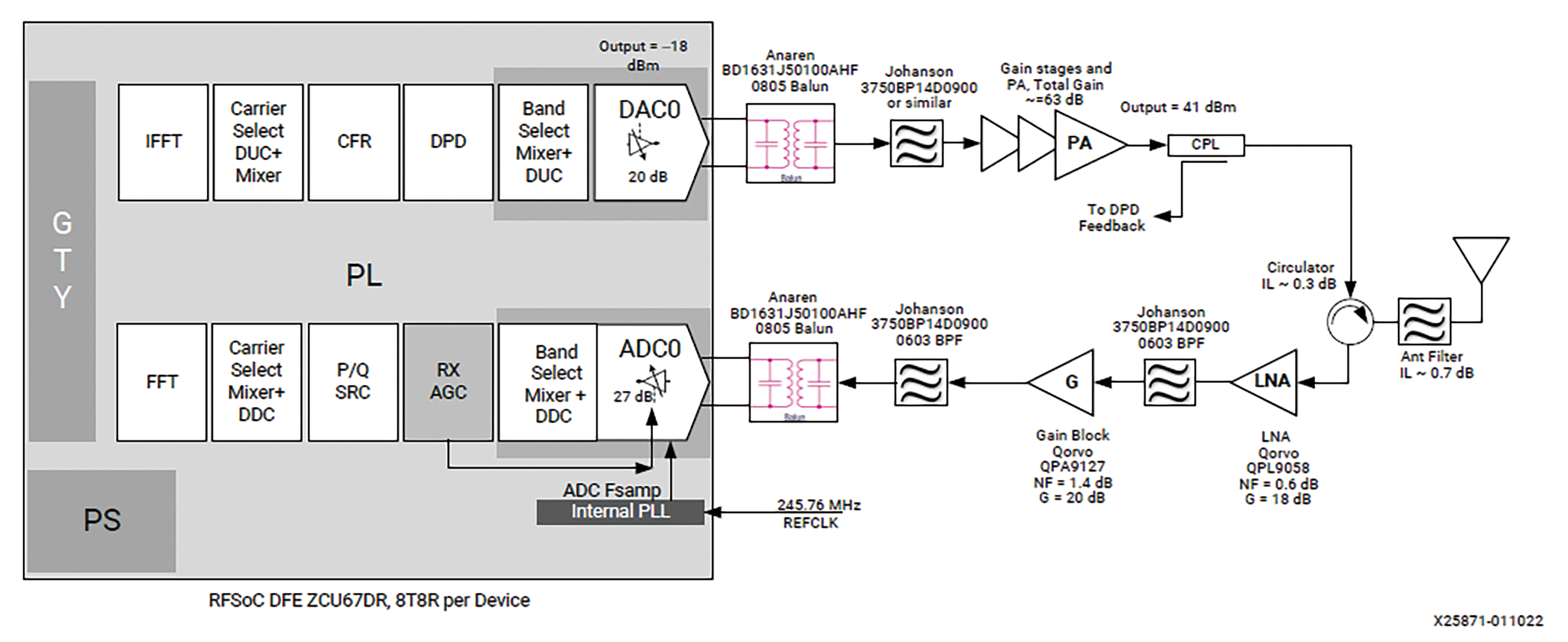

如果阻斷訊號的假頻直接落在有用的C頻段上,則模擬濾波在1,900MHz上的總抑制是16-(-109) = 125dB。如果阻斷訊號的假頻沒有直接落在C頻段上,則抑制要求可以降低。圖7的設計範例對兩種情況都進行研討,並評估沿RF流程分配濾波的最佳方式。 如圖7中的接收器流程所示,設計範例使用標準的目錄元件,滿足上表中要求的目標。對於mMIMO系統,因為尺寸和機械式管件嚴格由設計決定,天線濾波器通常是訂製零件,所以沒有指明具體零件。

圖7 接收器流程設計範例

圖7 接收器流程設計範例

天線濾波器必須將16dBm的阻斷強度濾除到以下水準:避免過度驅動LNA,以及以天線輸入為基準,LNA產生的HD2和IMD2低於-109dBm。

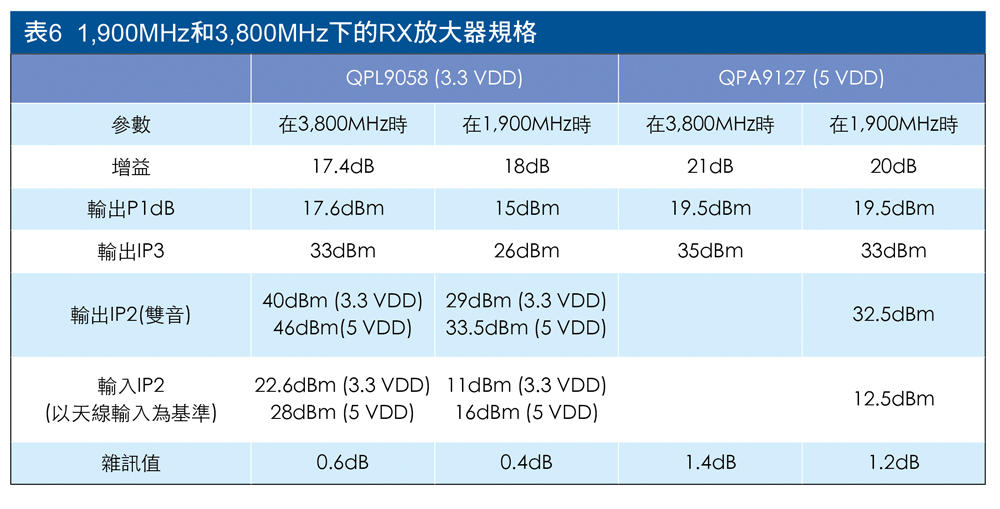

針對C頻段調校的LNA和增益塊通常在3,800MHz進行優化,在1,900MHz時以P1dB、IP2和IP3的形式衡量,動態範圍效能有所下降。Qorvo QPL9058(工作電壓3.3 VDD)和QPA9127的規格總結在表6中。產品說明書中未說明這兩個元件的IP2規格,因此所使用的值來自對使用對應評估套件的實際測量。

值得注意的是,在1,900MHz上時,儘管IP2/IP3嚴重劣化,但增益通常與3,800MHz相同。

QPL9058 LNA能使用5.0伏特(V)和3.3伏特兩種供電電壓。這裡使用3.3伏特VDD降低功耗,但代價是線性下降。除非另有說明,表6裡的資料針對3.3 VDD。

要實現10dB餘裕的1號目標,天線濾波器在1,900MHz時的抑制需要超過29dB,亦即:

16dBm + 18dB增益 - 濾波器抑制 (dBm) ≤ 15dBm - 10dB餘裕

為實現2號目標,即根據IP2公式,IMD2 = 2*Power_in - IIP

2*Power_in - 11dBm ≤ -109dBm → Power_in ≤ -49dBm

這要求天線濾波器在1,900MHz時的抑制需要至少有16dBm - (-49dBm) = 65dB。

這比1號目標更加嚴格,接近TX輻射濾波器62dB要求。這項要求與使用的ADC架構的類型無關,而且如前文所述,75dB抑制的濾波器供貨充沛。為具有一般性,在後面的分析中,假設天線濾波器在1,900MHz時的抑制是70dB。

這個設計的兩個增益級間的BPF是Johanson 3750BP14D0900[2]。它採用0603封裝,成本極低,而且在1,990MHz時可提供超過50dB的抑制。這是強化對阻斷訊號的濾波,以降低第二級放大器產生的IMD2/HD2的有效途徑。還是以天線輸入為所有運算的基準,第二級放大器後的IMD2/HD2產物如下(使用兩個濾波器):

阻斷功率(以天線輸入為基準)= 16dBm - 70dB - 50dB = -104dBm

QPA9127放大器產生的IMD2 = 2*Pwr_in -IIP2 = 2*(-104) - (12.5dBm) = -220.5dBm

通常情況下,HD2比IMD2小6dB,所以兩個指標都比-109dBm的目標干擾功率水準低得多。如果不加入這個BPF,根據上述公式,HD2/IMD2在大約-120.5dBm,同樣低於-109dBm這個目標水準。因此,在這個範例RF流程中,這個濾波器是選配。如果使用了不同的第二級增益放大器,導致二階產物較差,或設計人員希望為元件效能變化提供更大餘量,即可以選擇使用。

.抗混疊濾波器

抗混疊濾波器(AAF)選用與選配帶通濾波器相同的濾波器,因為它效能高、尺寸小、成本低。該濾波器對於濾除帶外雜訊至關重要,否則假頻將混疊到ADC輸出的第一奈奎斯特區域。RF取樣ADC的優勢之一是它能夠提供極寬的奈奎斯特頻寬(通常大於1GHz)。這允許進一步放寬抗混疊濾波要求。實際上,只要混疊雜訊不折疊在有用頻段上,AAF的通帶可以大至ADC的奈奎斯特頻寬,小至有用頻段。ADC中內置的DDC負責進一步的特定頻段選擇和抗混疊濾波。

共置部署下AAF的另一項功能是強化對阻斷訊號的濾波,防止接收器靈敏度下降。濾波量取決於在所選ADC取樣速率下,阻斷引起的ADC混疊的位置。存在兩種情況:情境A - 阻斷混疊直接落在有用的C頻段上,要求ADC輸入端的阻斷訊號必須≤-109dBm(以天線輸入為基準);情境B - 阻斷混疊落在有用的C頻段外,如果不造成ADC輸入飽和,則無需對阻斷訊號進行濾波。在這種情況下,透過適當的頻率規劃,直接RF取樣可提供更大的靈活性。

.情境A

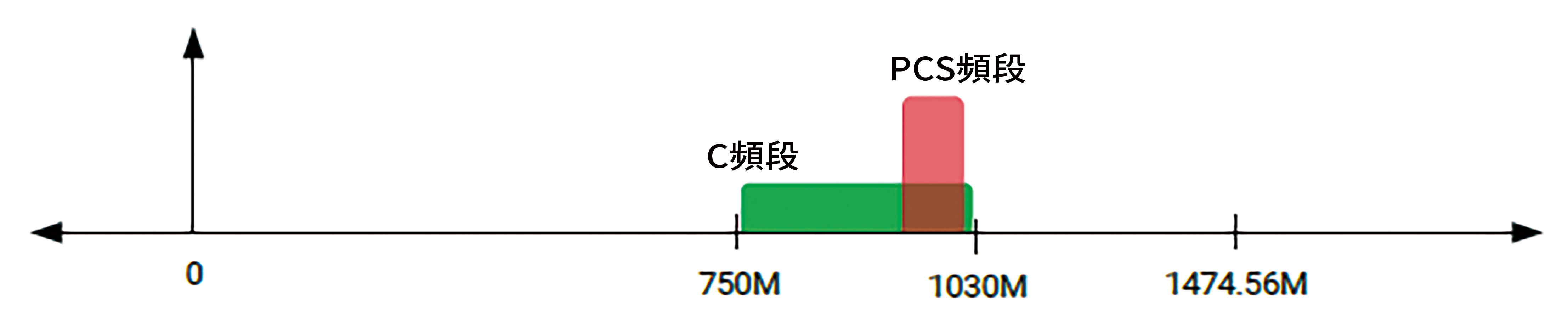

針對情境A,設計將ADC取樣速率設置在2949.12 MSPS。根據取樣理論,所有大於奈奎斯特頻率的頻率內容都會在第一奈奎斯特區域內產生混疊,因此ADC輸入端C頻段基頻頻率範圍為750.88MHz到1,030.88MHz、ADC輸出端PCS頻段基頻頻率範圍為959.12MHz到1,019.12MHz。

如圖8所示,PCS頻段落在有用的C頻段上。

圖8 Fs=2949.12 MSPS時,ADC輸出端的基頻頻率位置

圖8 Fs=2949.12 MSPS時,ADC輸出端的基頻頻率位置

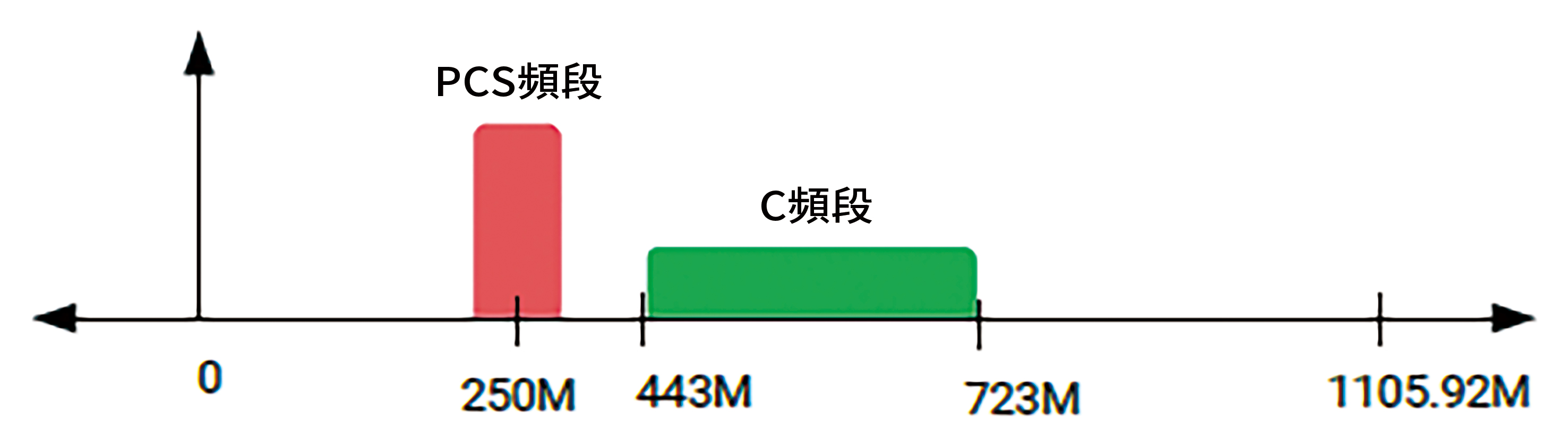

圖9 Fs=2211.84 MSPS時,ADC輸出端的基頻頻率位置

圖9 Fs=2211.84 MSPS時,ADC輸出端的基頻頻率位置

憑藉這種AAF的優異效能,ADC輸入端的16dBm阻斷訊號降低到(仍以天線輸入為基準。為簡化運算,這裡假設其他元件的總增益在1,900MHz和3,800MHz上相同):

16dBm - 70dB - 50dB - 50dB = -154dBm

這個數值顯著低於-109dBm的目標。正如分析所示,在採用低成本、高效能的陶瓷晶片濾波器後,最惡劣設計情況下的共置阻斷也能輕鬆地解決。沒有必要採用規格更高的高成本天線濾波器,因為在RX鏈路的後續階段對阻斷訊號進行濾波,效率要高得多。如果不使用選配BPF,則阻斷的混疊功率是-104dBm。雖然這足以滿足3GPP規範,但無法提供所需的餘量。在這種情況下,選配BPF雖然會略微增加成本,但可提供充裕的設計餘量。

.情境B

與基於ZIF架構的接收器不同,RF取樣轉換器可提供極寬的奈奎斯特頻寬,方便設計人員對阻斷訊號開展頻率規畫,使之落在有用頻段之外。因為ADC取樣速率需要是5G無線電基頻取樣速率(如30.72 MSPS)的整數倍,所以通常情況下RF取樣ADC只能使用幾種ADC取樣速率。為了放寬這種約束,RFSoC DFE等元件內建高效能、低功耗的分數重新取樣器,向設計人員提供更豐富的頻率規畫選擇。可用轉換速率包括2/3、3/4、4/5以及5/6,同時提供超過85dB的抗混疊濾波效能。

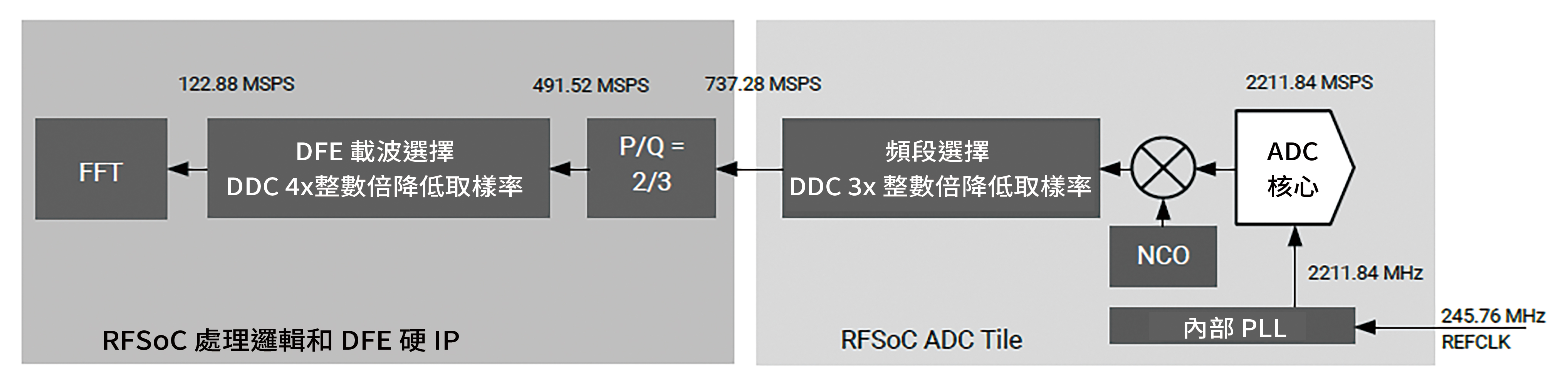

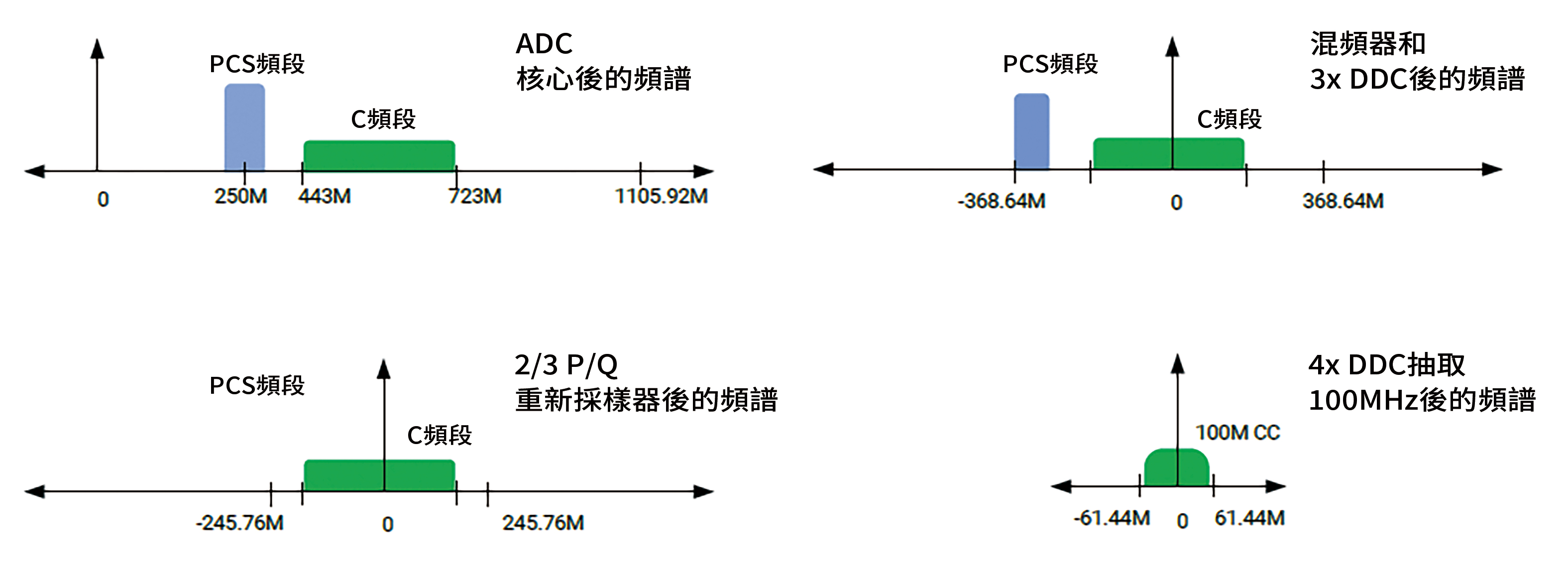

不採用情況A中的2949.12 MSPS(96×30.72M)ADC取樣速率,而是採用2211.84 MSPS的取樣速率,ADC就能讓PCS混疊頻段完全落在C頻段之外,如圖9所示。換言之,C頻段混疊到443.68MHz~723.68MHz,PCS頻段混疊到221.84MHz~281.64MHz。 如圖10、圖11所示,使用內置的2/3 P/Q重新取樣器將資料速率轉換回5G基頻取樣速率的整數倍。採用這種頻率規畫後,只要不造成ADC前端飽和,ADC輸入端的阻斷功率就可以放鬆要求。然後,透過ADC核心的帶選DDC、P/Q重新取樣器和DFE載波選擇DDC中的高選擇性數位濾波器將其去除。在這個設計中,ADC的全額輸入功率約為1dBm,相當於AFE增益為33.4dB時以天線輸入為基準的-32.4dBm。作為參考,天線濾波器提供的第一級70dB濾波已經足夠使用。因此,在選擇濾波器組合時,不需要考慮ADC上的阻斷混疊問題。在這種情況下,提供70dB抑制的天線濾波器加上AAF就已經綽綽有餘。沒有選配BPF不會造成任何負面影響。

圖10 每一階段的DFE取樣速率

圖10 每一階段的DFE取樣速率

圖11 DFE每一階段的基頻頻譜

圖11 DFE每一階段的基頻頻譜

Zynq UltraScale+ RFSoC DFE功能豐富,加上高速ADC取樣速率,為無線電架構提供大量處理共置部署的選擇(更複雜的共置部署也不例外)。其中之一是與多個干擾頻段共置。在這種情況下,設計人員可以選擇:透過頻率規畫,讓所有阻斷頻段在有用頻段外混疊。如果不可行,可以優先處理對濾波器設計影響最大的頻段(例如更靠近有用頻段的共置頻段)。

Zynq UltraScale+ RFSoC DFE靈活性強、效能高,與方便購買的低成本、小尺寸晶片濾波器配合使用,非常容易滿足共置要求。與非共置部署相比,無論採取何種ADC架構設計,天線濾波器處理這些要求的難度沒有顯著增大。

5G寬頻無線電接收器架構選擇/權衡取捨

到目前為止,研究重點主要放在3GPP規範對共置部署的補充要求對收發器設計造成的影響。使用RF取樣資料轉換器(比如RFSoC DFE中提供的),同時配合方便購買的低成本帶通濾波器,這些要求很容易得到滿足。實際上,還有共置之外的其他考慮因素和要求需要解決。特別是對於收發器而言,無線電設計人員在做出有關收發器架構的設計選擇時,還必須考慮帶內靈敏度和阻斷[1]要求。在3G和4G時代,因為無線電的窄頻性以及ZIF的RF影像濾波器需求容易解決,所以ZIF接收器成為了常用架構。但這種情況在5G時代不再適用,因為5G的寬頻性對ZIF收發器架構的主要缺陷發起嚴峻挑戰。

為了實現5G增強型移動寬頻(eMBB)使用案例的十億位元輸送量,分量載波的頻寬已從4G LTE的20MHz提升到FR1的100MHz乃至FR2的400MHz。無線電RF 工作頻寬往往在FR1覆蓋400MHz,在FR2覆蓋1,600MHz。無論是這樣的超寬RF無線電頻段,還是需要為多個頻段的載波聚合提供支援,非連續工作頻段也逐漸變得更為常用。隨著干擾訊號頻寬達到20MHz,3GPP合規要求對相鄰通道選擇性和帶內阻斷的要求也變得更加嚴格[1]。

也許ZIF最常見的問題是基頻輸出端的本地振盪器(LO)洩漏。LO洩漏同時包含靜態分量和動態分量。靜態分量在執行時不會有太大的變化,但會隨設備單元發生變化。動態洩漏分量與許多因素有關,例如溫度、輸入訊號、非線性失真、接收器元件鏈變化、類比混頻器、LO隔離等。實際上,接收器必須採用相當複雜的DC調零演算法,即時降低LO洩漏功率,避免它劣化有用訊號的訊噪比(SNR)。由於洩漏功率動態變化,調零演算法必須在追蹤速度、調零精度和實現成本之間進行權衡取捨,這樣很難將LO洩漏降低到不劣化接收器靈敏度的水準。實際上,將LO 洩漏功率降低到接近-109dBm(以天線輸入為基準)很難實現。

這個問題在4G LTE中並不嚴重,因為LTE載波在載波中心沒有子載波。因此,無線電設計人員可以使用次優演算法實現可接受的效能水準。而5G NR的分量載波不具備這個特點。載波的整個占用頻寬內都存在有效的子載波。這使得LO調零演算法進一步複雜化,這是因為難以區分有用訊號和LO洩漏。這種演算法的任何非零迴路頻寬都會對集中在DC周圍的有用訊號的子載波產生不利影響。 另一個廣為人知影響5G訊號的是偽訊號,亦即LO和混頻器在DC上產生的固有的1/f閃爍雜訊。這種雜訊不能使用LO調零演算法降低,因為將對接收器在相關頻段區域的靈敏度造成顯著影響。

ZIF接收器另一個為人熟知的難題是I通道和Q通道之間增益不平衡和相位不平衡產生的影像。影像是DC周圍訊號的鏡像,落在有用頻段內。0.2dB的增益不平衡和2度的相位不平衡,將產生相對於主訊號-39dBc的影像。通常情況下,未校準的ZIF IQ接收器的映射大小在30~35dB。I訊號通道和Q訊號通道上有許多存在失衡、影響影像水準的元件,包括ADC、低通濾波器、降頻轉換器/混頻器、I/Q獨立增益級、單獨調節I和Q及提供RX AGC功能的數位步進衰減器(DSA)、LO 90度移相器。

為了降低影像大小,ZIF接收器設計常採用IQ校正機制。運算IQ失衡度並提供補償的過程相當複雜,設計中需要增加支援校正的硬體。ZIF RFIC元件中的正交誤差校正(QEC)區塊在設計上一般採用單一複合校正分接頭,適合校正單一頻點或窄瞬時頻寬(iBW)上的IQ不平衡。這種方法一般足以應付載波頻寬和工作頻寬都較小的4G系統。對於頻寬更大的5G無線電,需要更複雜的QEC濾波器。這樣不僅增大功耗,也增大校正機制的運算複雜性。

因為IQ不平衡,影像在ZIF接收器上落在與有用訊號相同的頻段上。這種情況劣化靈敏度,特別是在相同頻段上一個載波的功率大於另一個載波的時候。

另一個IQ影像引起問題的工作狀況是相鄰通道選擇性(ACS)對不連續頻段的要求,會嚴重限制設計人員的頻率規畫選擇。

ZIF接收器的一個優勢是對RF影像濾波要求較低,因為IQ解調器和ADC之間有一個低通濾波器。雖然5G NR接收器也採用同樣的設計,但因為低成本微型陶瓷帶通濾波器的存在,這個優勢基本上不復存在。多家公司包括Johanson和村田製作所(Murata)現在將這種產品當作標準目錄濾波器,向每個NR頻段供應。與本分析中使用的Johanson C頻段陶瓷濾波器同等的產品是村田製作所LFB213G60CGUE234[3]。

雖然名義上ZIF接收器不需要抗混疊RF濾波器,但實際上仍會使用。AAF的主要功能是去除放大器級產生的帶外HD2和HD3產物,避免解調器中出現任何最終會落入基頻和有用的C頻段上的M×N混頻產物。例如,2×LO與HD2混頻以及3×LO與HD3混頻,將落在有用頻段的同一位置上。

(本文由AMD Xilinx提供)