在高性能高頻系統中,晶振的選型十分重要,低相位雜訊的晶振能夠使振盪器相位雜訊曲線的劣化程度最小化。本文透過比較理想時脈訊號與實際時脈訊號,講解相位雜訊的概念,接著介紹相位雜訊的兩個關鍵指標:誤差向量幅度(EVM)與壓控振盪器(VCO)阻塞,最後介紹該如何選擇低相位雜訊晶振。

很多高頻應用,比如鎖相迴路、5G應用,都離不開時脈訊號(Clock Signal)。這些高頻應用的相位雜訊往往是一個項目成敗與否的關鍵因素。本文透過比較理想時脈訊號與實際時脈訊號講解相位雜訊的概念,接著介紹相位雜訊的兩個關鍵指標:誤差向量幅度(EVM)與壓控振盪器(VCO)阻塞,最後介紹該如何選擇低相位雜訊晶振。

理想時脈訊號vs實際時脈訊號

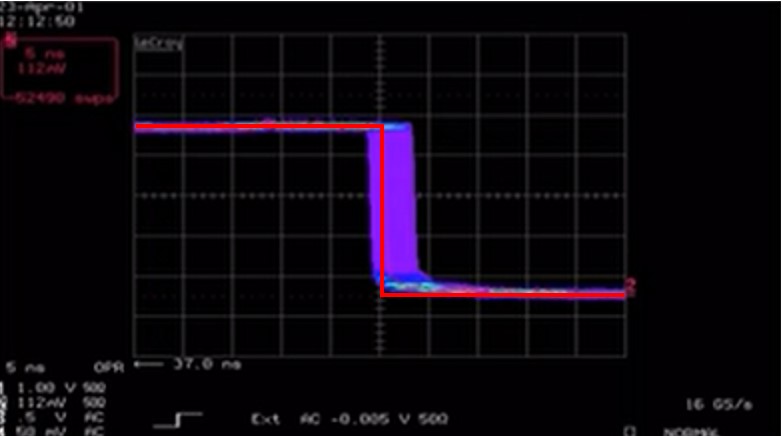

很多高頻應用都離不開時脈訊號,圖1是一個典型的時脈訊號的負緣(Falling Edge)。理想中的時脈訊號如圖1紅線所示,而實際的時脈訊號如圖1紫色線條所示。

圖1 典型的時脈訊號的負緣 (圖片來源:ADI)

圖1 典型的時脈訊號的負緣 (圖片來源:ADI)

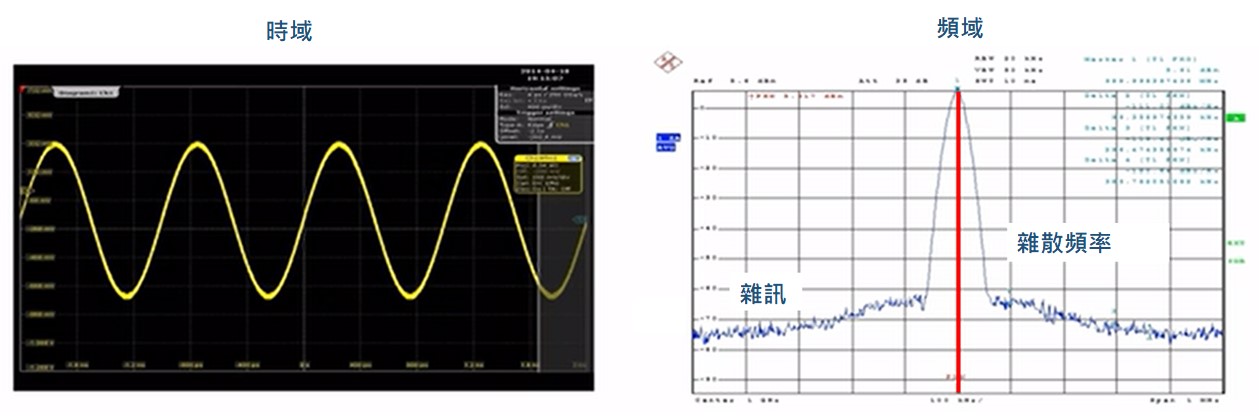

同樣對於正弦波來說,理想的正弦波在頻率下對應一個頻率訊號,如圖2紅線所示。實際上,由於雜訊和雜散頻率的存在,正弦波在頻域影像如圖2右邊藍線所示。

圖2 典型正弦波訊號 (圖片來源:ADI)

圖2 典型正弦波訊號 (圖片來源:ADI)

通常為了正確測量相位雜訊,我們常會用到的兩種儀器:

.頻譜分析儀:用於測量訊號的頻域圖。

.示波器:用於測量訊號的時域圖。

相位雜訊的概念

接下來以鎖相迴路PLL的局部振盪器(Local Oscillator, LO)輸出為例,看看相位雜訊的概念。相位雜訊是指當訊號到達系統接收端時,由於意外超前或滯後而產生的雜訊。

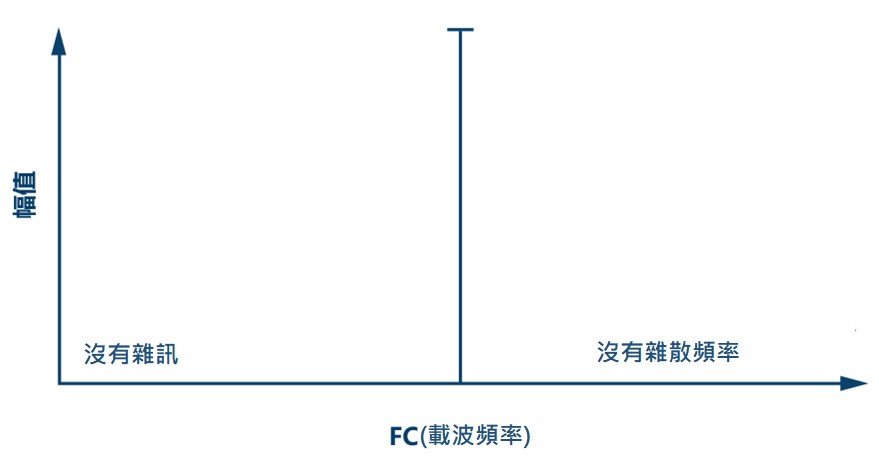

理想的LO輸出沒有雜訊或額外雜散頻率(圖3)。

圖3 理想LO輸出 (圖片來源:ADI)

圖3 理想LO輸出 (圖片來源:ADI)

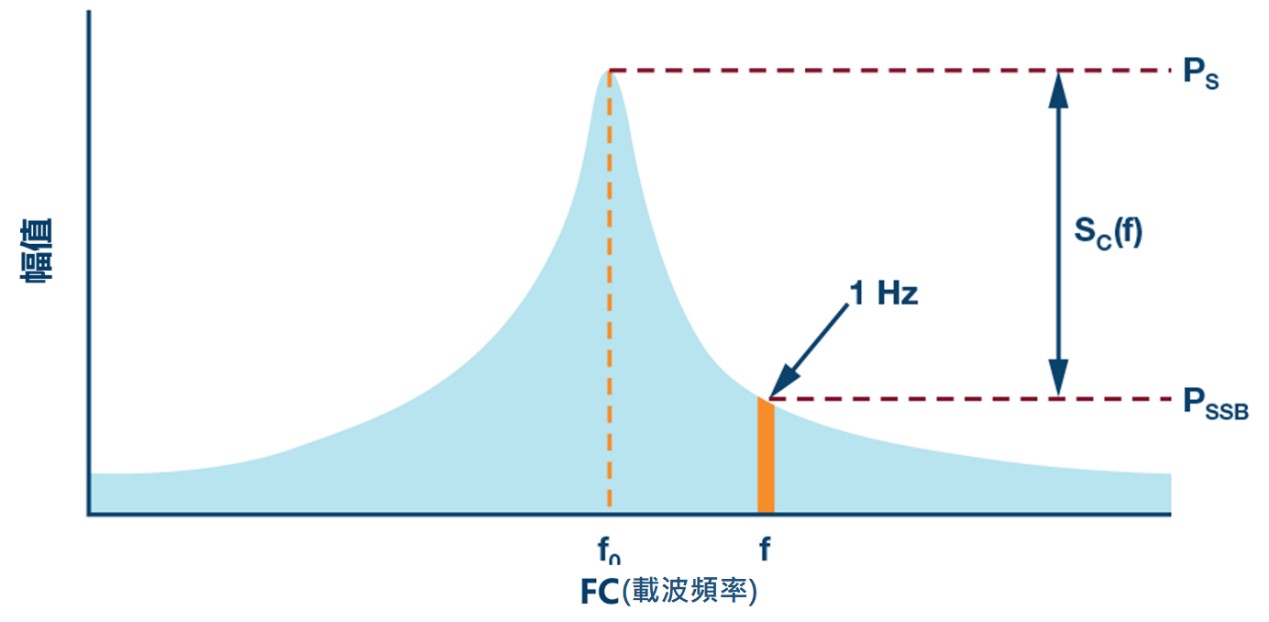

但在實際應用中,相位雜訊像裙擺一樣出現在載波邊緣,如圖4所示。

圖4 實際LO輸出 (圖片來源:ADI)

圖4 實際LO輸出 (圖片來源:ADI)

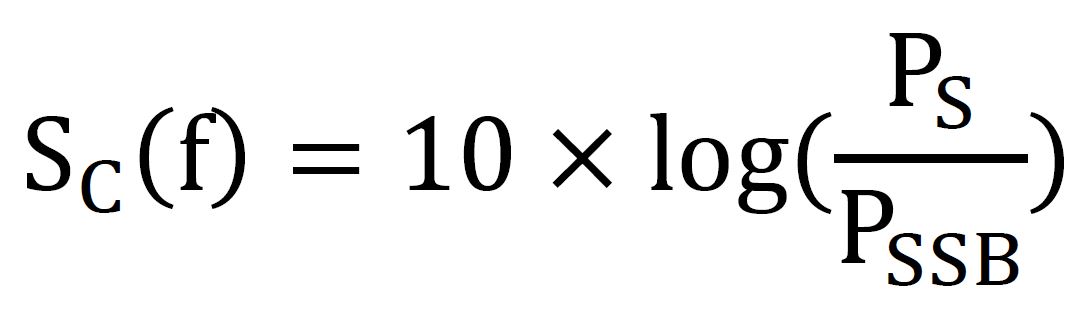

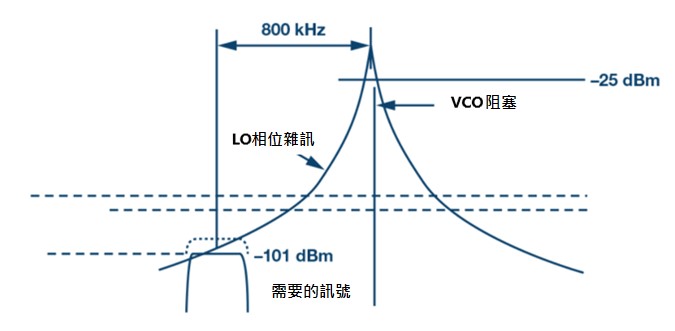

單邊帶相位雜訊的定義是:在某一偏移頻率處,在該頻率處1Hz頻寬內的訊號功率與訊號的總功率比值。單邊帶相位雜訊計算方式如公式1,單位以dBc/Hz表示。

我們可以將相位雜訊資料繪製到相對RF載波的頻率偏差中(圖5)。

圖5 相位雜訊繪圖方法 (圖片來源:ADI)

圖5 相位雜訊繪圖方法 (圖片來源:ADI)

除了單邊帶相位雜訊,對於通訊系統,從PLL角度來看,誤差向量幅度(EVM)和VCO阻塞也經常被使用。

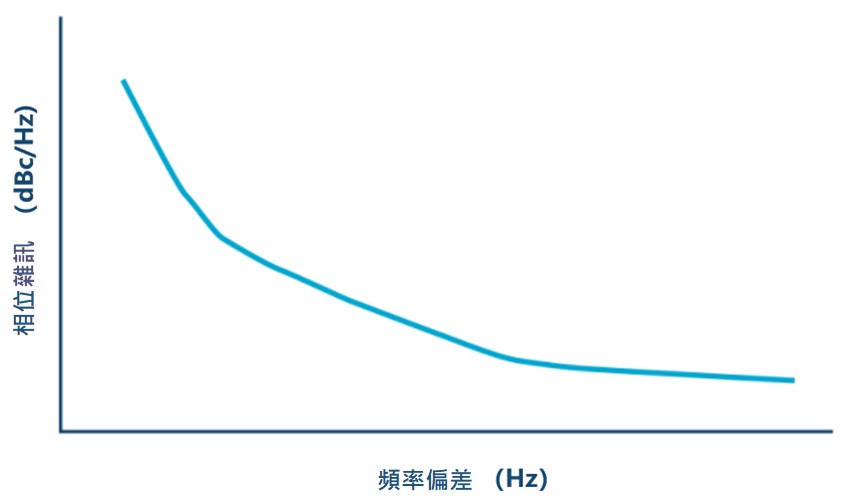

誤差向量幅度(EVM)

誤差向量幅度(EVM),定義為誤差向量訊號平均功率的均方根值與理想訊號平均功率的均方根值之比,並以百分比的形式表示。EVM越小,訊號品質越好。這個指標能全面衡量調變訊號的幅度誤差和相位誤差。EVM可被視為是理想調變訊號相對於理想點的性能降幅百分比(圖6)。

圖6 視覺化相位誤差 (圖片來源:ADI)

圖6 視覺化相位誤差 (圖片來源:ADI)

使用訊號分析儀可以有效測量EVM、積分相位雜訊、均方根相位誤差和抖動等。

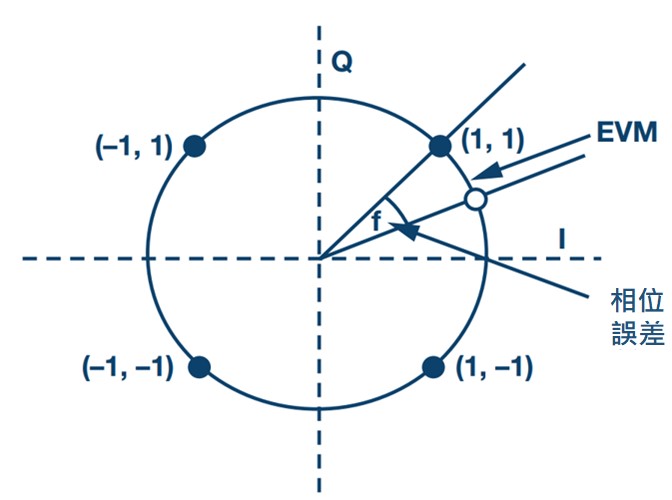

VCO阻塞

對於5G應用來說,VCO阻塞規範在需要考慮強發射的蜂巢式網路系統中非常重要。如果接收器訊號很弱且VCO雜訊過高,那麼附近的發射器訊號可能會向下混頻,淹沒目標訊號。

圖7展示了如果接收器VCO雜訊很高,附近的發射器(相距800kHz)以-25dBm功率發射時,是如何淹沒-101dBm目標訊號的。這些規範構成無線通訊標準的一部分。阻塞規範直接影響VCO的性能要求。

圖7 VCO雜訊阻塞 (圖片來源:ADI)

圖7 VCO雜訊阻塞 (圖片來源:ADI)

低相位雜訊晶振

在高頻設計中,我們所採用的晶振主要是石英晶體振盪器。一些外界因素(比如溫度),會影響晶振的穩定性。Digi-Key網站提供詳細的晶振參數作為篩選依據,篩選相位雜訊性能指標時,建議關注「頻率穩定性」參數(圖8)。

圖8 Digi-Key晶振選型頁面中的「頻率穩定性」參數

圖8 Digi-Key晶振選型頁面中的「頻率穩定性」參數

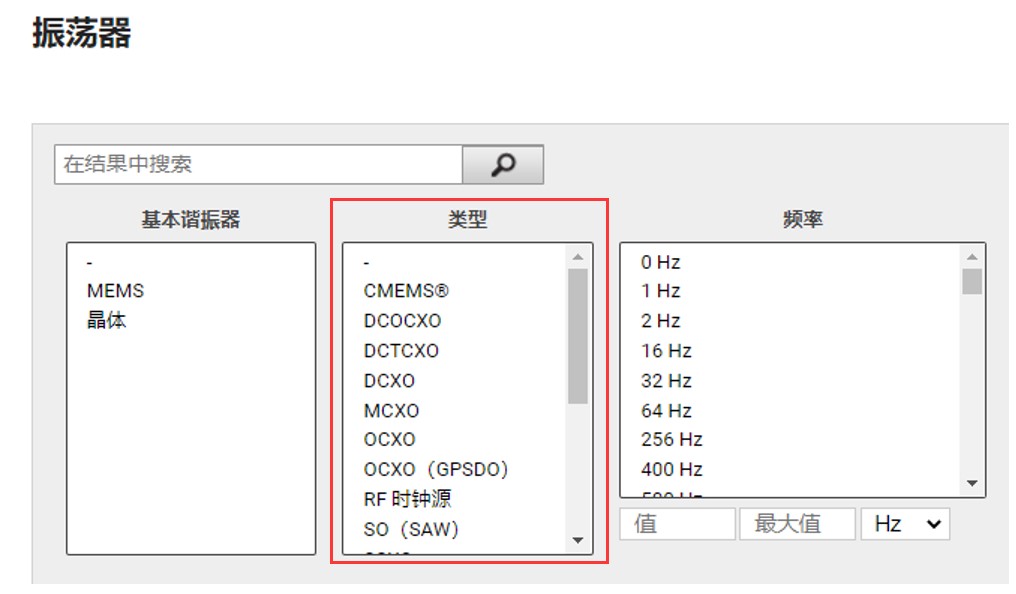

另外,晶振類型也是重要因素,如圖9所示。

圖9 Digi-Key晶振選型頁面中的「類型」參數

圖9 Digi-Key晶振選型頁面中的「類型」參數

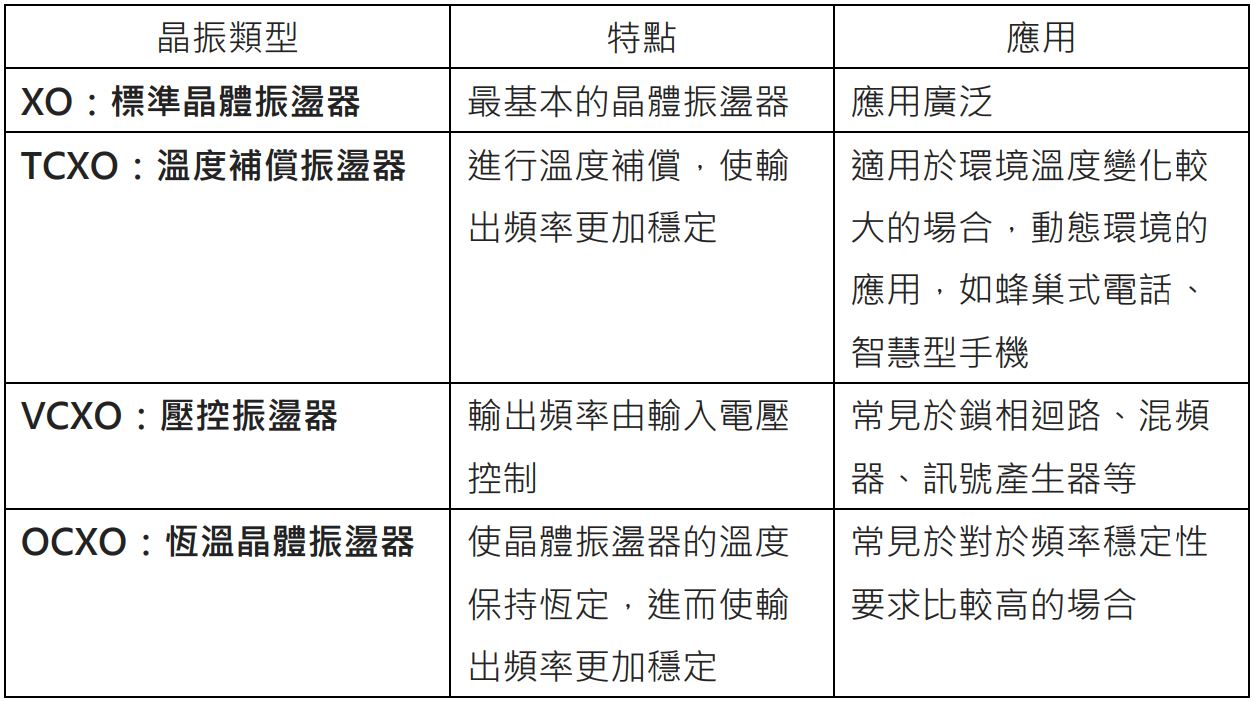

表1總結常見晶振類型的特性及應用。

表1 常見晶振類型

表1 常見晶振類型

從雜訊角度來講,訊號鏈的目標就是盡可能降低振盪器相位雜訊曲線的劣化程度。因此,在這些高性能系統中,對於晶振的要求也更高。為目標應用選擇合適的晶振,可以讓設計事半功倍。

(本文作者任職於Digi-Key)