行動電話、平板電腦和其他行動設備已演變成為能執行多種任務的微型多功能電腦,雖然這些設備提供了便利性,但它們幾乎處在連續不停使用的狀態下,因此容易受到靜電放電(ESD),而引起損壞。有鑑於此,目前有業者推出ChipSESD元件,為設計人員提供所需的尺寸和性能特性,能夠保護敏感電子裝置,避免因ESD所引起的影響。

事實上,行動設備使用者之需求日益複雜,使得可攜式產品的設計必須整合更多的輸入/輸出(I/O)互連,但是更高的電流密度和更小的電晶體尺寸,以及用於晶片保護的有限空間,都會增加電子元件對靜電放電等瞬態電氣過應力事件(Overstress Event)的敏感性。如果能把此類瞬態事件所產生的影響降到最低,不僅有助於防止設備在相互交談時產生資料損毀,還可進一步提升整體運作的可靠性。

靜電電位相異易引起ESD事件

事實上,兩個具有不同靜電電位的物體經由接觸、電離空氣放電或火花放電而進行能量轉移,便會引起ESD事件。材料類型、接觸面積、分離速度、相對濕度和其他因素均會影響摩擦充電產生的電荷量;一旦材料產生電荷,便成為靜電電荷,該電荷可從材料上轉移,進而發生ESD事件。

靜電的主要來源是絕緣裝置,通常是合成材料(比如乙烯基或塑膠工作表面、絕緣鞋、經塗層處理的木

椅子、膠帶、塑膠包裝(Bubble Pack)和帶有未接地接腳的烙鐵)。

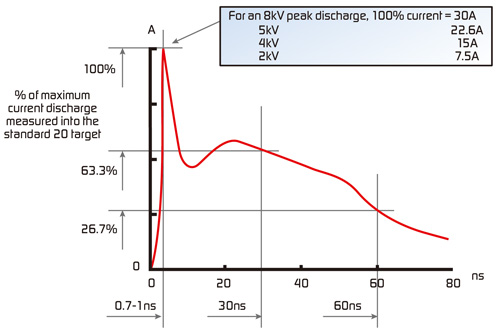

圖1所示為典型的ESD特性曲線,為了模擬接觸放電事件(Contact Discharge Event),ESD產生器在測試設備上施加一個ESD脈衝。這項測試的特性是短上升時間和低於100奈秒(ns)的短脈衝持續時間,這說明了它是低能量靜態脈衝,由於這些來源的靜電並非早已分布在其表面或者已傳導到其他物件,因此有可能會產生極高的電壓位準。

|

| 圖1 由ESD產生器所模擬的典型8kV ESD脈衝。 |

最常見的ESD來源包括:

| ‧ |

帶電的人體 |

| |

人體可能因為行走或其他動作而帶電,如果人體經由金屬物件(例如工具)放電,那麼造成的ESD損壞便會特別嚴重。 |

| ‧ |

拖過地毯的電纜 |

| |

如果一個帶電的電纜插入一個具有任何電荷來源的傳導觸點,便可能產生ESD瞬態。 |

| ‧ |

處理聚乙烯袋 |

| |

當一個電子設備滑進或滑離袋子或管子時,設備的外殼和/或金屬引線與容器表面發生多次碰觸和分離,便可能產生靜電電荷。 |

ESD事件與電子設備運作的環境有關。舉例來說,汽車系統、空運(Airborne)或艦載設備、太空系統、工業設備或消費產品之間的瞬態環境變化都有很大差異。

使用者頻繁地使用行動設備,很可能在連接或斷開電纜期間觸碰到I/O連接器接腳。在正常運作條件下,觸碰到暴露在外的埠或介面可能會產生超過30千伏(kV)的放電電壓。

小尺寸半導體元件可能會因為過多的電壓、高電流位準或二者的結合而受到損壞,高電壓位準可能引起閘極氧化層擊穿,而過多的電流可能引起連接點(Junction)故障和金屬化跡線熔化。

高速I/O介面ESD保護不可少

IC製造商一方面已經實現更高頻率的I/O互連,另一方面還在繼續縮小電晶體、互連產品以及元件中二氧化矽(SiO2)絕緣層的最小尺寸,使得在較低能階(Energy Level)上發生擊穿損壞的可能性也變得越來越大,從而使得ESD保護成為了設計時的一個主要考慮事項。

根據IEC61000-4-2國際標準,大多數電子設備必須滿足最小8千伏接觸放電電壓或15千伏空氣放電電壓的要求。然而,許多半導體元件卻無法承受這樣的電應力,有可能會受到永久性損壞,為了提高它們的可靠性,必須在系統中加進晶片外保護電路(Off-chip Protection Circuit)的設計。

設計高速I/O介面的ESD保護時,有兩個主要考慮因素。

| ‧ |

用於高速I/O介面的ESD保護電路必須足夠穩健,要能夠有效地保護內部電路的薄閘極氧化層,以避免ESD應力造成損壞。 |

| ‧ |

必須將ESD保護元件的寄生效應降到最低,因為它會讓高速電路性能退化。 |

分立元件小型化一直是業界持續努力發展的方向,但它卻也經常為設計人員帶來許多挑戰。舉例來說,像是工程樣品的構建變得更加困難和耗時,還有重做(Rework)的挑戰及製程控制的問題。

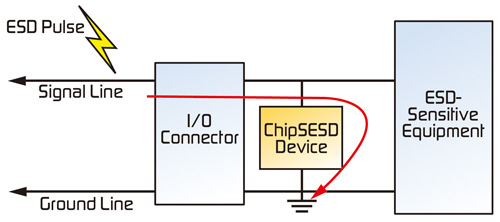

目前業界提出的ChipSESD元件不僅可以滿足高速I/O應用的必要要求,還有助於減輕元件和製造時所面臨的挑戰,該元件可以將可能有害的電荷導離敏感電路,以協助保護系統以避免發生故障,如圖2所示。

|

| 圖2 ChipSESD有助保護敏感電路,避免ESD帶來的損壞。 |

導入SMT被動封裝優勢 ESD元件實現輕鬆安裝

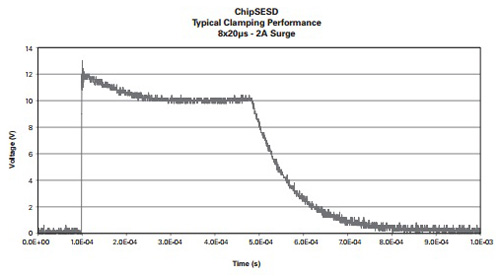

新款元件結合主動矽元件和傳統表面黏著技術(SMT)被動封裝配置的優勢,比傳統的半導體封裝ESD元件更容易安裝和重做;此外,在8×20微秒(μs)浪湧下具有2安培(A)浪湧額定電流和10千伏額定接觸放電電壓(圖3)。

|

| 圖3 ChipSESD典型的箝位性能 |

該元件的低洩漏電流(最大值1.0微安培)可以減少功耗,而快速的回應時間(小於1奈秒)有助設備通過IEC61000-4-2的Level 4測試。其具有的4.0pF和4.5pF輸入電容,適用於各式各樣的行動設備應用。

除了外形尺寸小(0201和0402尺寸),ChipSESD元件的雙向作業(Bi-directional Operation)特性讓它可以很容易地安置在印刷電路板(PCB)上,沒有方向限制,並且可以省去極性檢測。被動封裝讓元件可以在安裝在PCB後輕鬆地進行焊接檢測,有別於在元件底部使用焊盤的傳統ESD二極體封裝。

從廠區至使用者家中,電子設備隨時隨地都可能會受到因靜電引起的損壞。ESD瞬態現象可能會破壞設備的運作,或者導致潛在的損壞,而外形尺寸小的低電容元件是一款容易使用的高性價比解決方案,可協助工程師一一克服這些挑戰。

(本文作者任職於TE電路保護部)