全球衛星定位系統(GPS)功能的應用愈來愈廣,市場的競爭也愈來愈激烈,導致其接收器定位的效能表現、尺寸、功耗等都成了產品差異化的關鍵。今日的GPS接收器須支援輔助式GPS(A-GPS)、太空輔助定位系統(SBAS)、日本的天頂(QZSS)等系統,以提升首次定位時間(TTFF)的速度及準確性,進而改善用戶的使用經驗。此外,歐盟的伽利略(Galileo)衛星系統也正在積極布建中,GPS接收器相關業者也開始承諾要做到Galileo Ready,也就是至少要能支援Galileo的L1開放服務訊號以及其基本的功能,然而系統成本則不能因支援此項功能而增加。

此外,由於GPS已進入個人定位的應用領域,這對於GPS接收器是很大的考驗,因為了除尺寸微縮與成本降低的要求外,個人定位的使用環境遠不如行駛在開闊天空下的車子,要在衛星訊號微弱的巷弄或室內做到精確的搜尋及追蹤,接收器的設計上必然更為困難。在88期新通訊專欄中已介紹了GPS的基本原理與效能要求,以及系統架構上的差異比較,本文將進一步剖析GPS接收器的先進技術設計要領。

成本/尺寸決定設計好壞 效能/功耗互為拉鋸

由於GPS功能大多用於手持式設備,因此成本與尺寸是設備商錙銖必較的考量,而將不同功能元件加以整合則是最常見的開發途徑。以GPS接收器來說,其整合目標是盡量減少外部的元件,最佳狀況是只剩下一些被動元件須要附加,而關鍵性的低噪訊放大器(LNA)和記憶體,則應整合到晶片當中。要達到這個目標,就必須善用CMOS高階製程的優勢。

在尺寸方面,晶片的封裝應具有成本效益,並占有最少的尺寸,其中QFN封裝是理想的選擇。當然,減少外部元件數量除了能降低成本外,也能滿足不占用電路板太大空間的需求。此外,依據應用上的需求,此晶片應該要能與週遭的電路,如溫度補償石英震盪器(TCXO)或即時時脈(RTC)分享部分功能。

如何達成高效能和低功耗,則是兩個互相對立但又要不得不同時滿足的設計條件。GPS接收器的效能參數包括訊號搜尋時間、追蹤及搜尋靈敏度、如包括一般狀況及多徑干擾環境的定位準確度。理想的接收器要能做到不會受到鄰近訊號源,如電腦顯示器或無線收發器等的干擾,也才能穩定達成定位功能。

在功耗上,不論是在運作或待機狀態下,系統的功耗都須做到最低。在搜尋衛星的運作時,是功耗需求最大的階段,但供應電流仍必須有所限制;在待機狀態下,電池仍須對隨機存取記憶體(RAM)維持供電,以支援自主式熱啟動和暖啟動,這時就須要特別注意洩露電流的問題。

另一個設計需求,就是要滿足設備業者及早上市的需求,因此GPS功能的建置愈簡單愈好。具完善功能的GPS接收器能夠有效簡化電路板的布局規畫,除了核心晶片外,其他搭配選用的被動元件應該都是標準型元件。GPS系統的電源供應必須具有彈性和效率,也就是除了支援主電源的直接供電,也要能支援由外部先進電源管理控制器所提供的電源。此外,對外連結的I/O介面須採用業界的標準,而且須做到多樣化的支援。

SoC增加設計難度 SiP降低開發門檻

在獨立式、主處理器式和軟體式三種GPS設計架構中,以獨立式具有最佳的設計優勢。在獨立式方案的架構中,射頻(RF)與基頻(BB)單元是兩大基本組成。將完整的GPS接收器功能整合到一個單晶片中,看起來非常理想,事實上也有成功的例子,不過,此種作法未必是最佳的選擇,理由包括,能同時滿足系統中類比和數位基頻單元的製程技術必然更為昂貴;由於整合後的面積增加,良率議題也會更嚴重;在生產時必須進行混合訊號測試;由於設計複雜度增加,設計時程一般也會拉得更長。

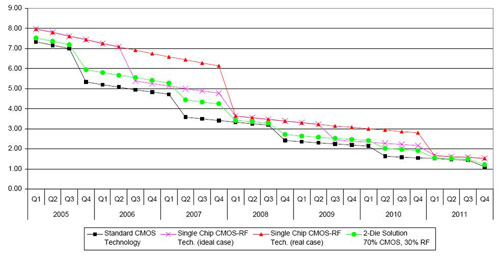

由上述的分析可以得知,今日無線技術在系統單晶片的發展上,因射頻與基頻適合的製程技術始終有發展腳步不一致的問題,因此仍未出現一種能整合兩種功能需求的最佳化、低成本製程技術。這也是為何有廠商的整合晶片仍選擇採用0.18微米RF-CMOS製程來設計射頻單元,並採用0.13微米CMOS製程來設計基頻單元,以得到最佳的成本效益及效能表現。然而,雖是不同的製程技術,但透過系統級封裝(SiP)的系統單晶片封裝,其實外觀和系統單晶片(SoC)單晶片並沒有什麼不同,開發的複雜度卻少了許多(圖1)。

|

| 圖1 2005~2011年單晶片與雙晶片隨時間的開發成本比較 |

GPS接收器運作複雜 組成單元牽一髮動全身

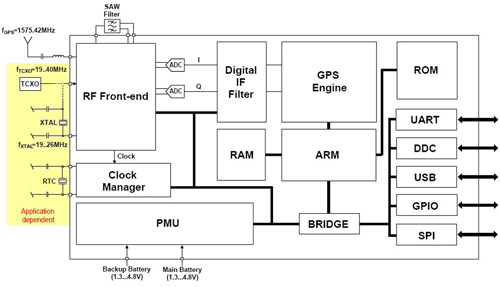

再來看看GPS接收器的組成架構。一個完整的GPS接收器包括天線、射頻硬體、數位基頻硬體、輸出介面和韌體等組成單元。如天線端可採主動或被動式天線;射頻單元包括射頻前端、LNA、頻率合成器(Fractional N Synthesizer)等,並須支援TCXO或XTO。在數位基頻,則包括GPS引擎、處理器核心、記憶體(ROM/RAM),並須支援即時時脈。

常見的輸出介面包括SPI、UART、USB 2.0、GPIO、DDC/I2C,若有使用外部的快閃記憶體,也須支援外部記憶體匯流排介面。

至於韌體方面,則包括搜尋(Acquisition)及追蹤(Tracking)衛星的演算法,以及導航(Navigation)的應用軟體。

以圖2的晶片方案運作為例,天線接收的GPS訊號通過一段LC電路後,進入已整合LNA的射頻單元,在這裏,接收到的高頻訊號會被降到約3MHz的中頻,之後再使用高解析度的類比/數位轉換器(ADC)轉換為數位基頻可處理的訊號,並送到相關器引擎進行電碼比對的工作。

|

| 圖2 GPS/伽利略接收器方案功能架構圖 |

此系統的控制核心為ARM7-TDMI微處理器,所有須用到的記憶體,包括儲存程式碼的ROM和用於暫存資料的RAM,都已被整合到此晶片中。此外,還有晶片上的一次可程式記憶體用來儲存用戶的設定,若須要儲存更多的組態,則可透過SPI或DDC介面來連結外部的串列式電氣式可抹除唯讀記憶體(EEPROM)。

這顆ARM核心除了與GPS引擎及記憶體相連外,也透過橋接器(Bridge)轉換對外溝通的介面格式,包括USB 2.0、SPI、RS-232 UART、GPIO、DDC等。在時脈的設計上,採用彈性的時脈產生架構,其基頻晶片和射頻前端各有一個分數型Sigma-delta鎖相迴路(Fractional Sigma-delta PLL),此鎖相迴路能產生各種需要的參考頻率。

此晶片中另一個重要的部分是電源管理單元(Power Management Unit, PMU)。基本上,此系統會需要兩個不同的供電,一個用於全速運作,另一個則是用來維持資料的有效性和讓即時時脈能在備用模式下運作。晶片中的PMU能支援下述供電需求:當系統需要直接與鋰離子電池相連時,PMU會產生所需的內部電壓;當1.8V-only的系統需要供電時,PMU中的低壓降穩壓器(LDO)會產生需要的電壓;此PMU可直接為射頻(1.8V)和基頻核心(1.2V)供電。

射頻前端直接影響效能表現 最佳化從抗干擾開始

由於GPS的訊號遠從太空中發射而來,到達地表時訊號強度已相當微弱,因此GPS接收器的射頻單元設計,是影響訊號接收效能表現的關鍵。要達到最佳化的設計,考量的因素很多,包括訊噪比(SNR)、接收器頻寬、動態範圍、整體系統整合和功耗等。此外,今日的天空中同時存在各種的無線通訊訊號,GPS射頻單元必須具備抗干擾(Jamming-immunity)的能力,同時也要能夠精確的追蹤GPS和伽利略訊號。

在存在多樣性干擾訊號的嚴峻環境中,在射頻段採用LNA的設計是必要的,這樣才能夠得到更佳的低噪訊表現,讓接收器在低供應電流、干擾嚴重的條件下仍能正常工作。而為了將外部元件需求降到最低,過去外掛的LNA、中頻濾波器和頻率合成器等元件也已一一被整合到射頻前端系統晶片當中。不過,TCXO仍是外掛的元件,它會與射頻前端相連。

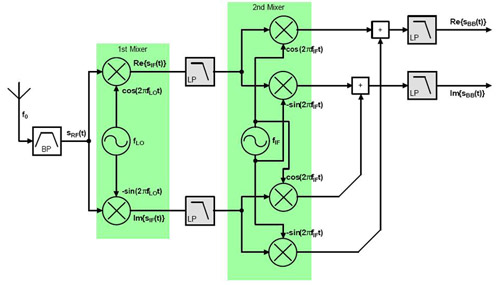

接收器的射頻段必須將1,575.42MHz的衛星訊號降頻到3MHz的中頻,才能再轉換為基頻可處理的低頻訊號。如圖2的晶片採用複雜混合器的二次降頻架構(圖3),在此過程中,GPS或伽利略訊號中的載波頻率及相位資訊必須被保留下來,而類比的降頻轉換程序將訊號轉換為ADC適用的頻率。

|

| 圖3 複雜混合器的二次降頻架構 |

事實上,每個衛星的載波頻率在傳輸過程中因受到都普勒效應的影響,到達接收器時頻率會發生改變。這是訊號誤差的主要來源之一,其他的誤差來源包括大氣影響(電離層、對流層)、衛星與接收器之間的時鐘偏差、多徑干擾及雜訊干擾等。精密的接收器要有能力針對這些誤差進行修正。

多徑干擾抑制提高定位精準度

在這些誤差來源中,多徑干擾抑制(Multipath Mitigation)已成為愈來愈重要的設計議題。所謂多徑干擾是指由於反射和繞射等效應,從發射器到接收器之間存在著多重的訊號路徑。在GPS系統中,需要的是透過直線路徑傳來的訊號,其他的訊號會扭曲所需的訊號,並導致計算上的誤差。在實際的運作中,包括直射、反射和繞射訊號都會被接收器天線接收,而所有的訊號會被加總起來做分析。如果接收器的硬體架構和訊號處理方法不佳,多徑訊號往往會大幅降低定位的準確度。

一般來說,多徑訊號走的路徑較長,因此會比直射訊號晚到達天線;此外,多徑訊號在反射時會造成訊號強度的衰弱,因此一般會比直射訊號微弱,不過當直線訊號遭到阻隔時,反射訊號也可能比直射訊號來得強。

今日的GPS設備常要在多建築物玻璃反射的市區中或騎樓、巷弄,甚至室內使用,這些環境中的多徑干擾嚴重,若無法做到最佳化的抑制,定位效果將差強人意。因此,採用先進演算機制及設計考量的射頻段,可以正確量測訊號失真的狀況,並加以還原。

基頻單元配置具彈性 相關器加速運算能力

基頻單元屬於數位設計,因此可以較彈性的配置功能及定義晶片尺寸,例如訊號搜尋和追蹤的需求可以獨立地做到最佳化。這對於一些應用來說是很重要的,以緊急救援電話為例,其關鍵的功能是訊號搜尋而非追蹤,因此可以減低這部分的硬體資源,進而能進一步縮小晶片尺寸。

但在移動式的定位應用中,就會要求提升訊號追蹤的品質;當訊號的搜尋並不困難時,那就可以提升追蹤的硬體處理能力,例如強化多徑干擾抑制的功能。此外,系統軟/韌體讓設計者能夠針對系統效能進行客製化的設計,例如針對功耗需求做調整。

同步支援GPS/伽利略 接收器門檻愈高

雖然伽利略衛星系統已發展出多種創新的載波頻率編碼技術,但L1的開放服務仍是最重要的大眾化頻率,因此目前已有GPS接收器支援Galileo L1的訊號擷取,並有能力將接收器的設計複雜度降到最低。伽利略訊號編碼的解碼機制與GPS相似,不過,多徑干擾的抑制需要不同的演算法。此外,對於伽利略的支援須具有延展性,也就是未來伽利略規範若有更動,可以透過韌體來升級因應。

今日的GPS接收器必須滿足高效能、低功耗、小尺寸、低成本等需求,而高度整合與採用先進製程是必然的手段,不過,由於類比射頻與數位特性的差異,採用不同的最佳化製程再進行SiP封裝是符合現實的作法。

在射頻前端的設計上,多徑干擾的抑制是改善用戶使用經驗的一個關鍵性技術,會成為產品性能區隔的決定因素。在基頻方面,除了相關器的數量與適性化的硬體布局外,對於GPS與伽利略兩大衛星系統的同步支援也是必然趨勢。

(本文作者任職於u-blox)