自2007年起,家電廠商所有的新設計都必須遵守IEC60335安全標準。為確保家電設備安全可靠,特別是設備故障不能威脅到使用者的人身安全,這套新標準涉及十分廣泛的內容,從機械系統到嵌入電子元件均有明確規定。

家電產品須符合安全規範

電子部分參照另一個標準,即適用於各種應用領域的IEC60730自動電子控制標準。對於嵌入式系統開發人員,附件H對於嵌入式系統開發人員尤為重要,因為該附件是關於可程式設計元件。白色家電通常使用多個微控制器(MCU):一個微控制器負責管理主控台,另一個管理閥門和馬達控制。

根據設備故障導致的危險程度,該標準將軟體分為A、B、C三類。如果家電安全不依靠軟體,則該家電屬於A類,如室內溫度控制器或照明控制器。相反地,倘若軟體用於防止安全隱患,如電子點火瓦斯爐歸為C類(本文不探討C類),電子控制系統防止不安全操作的家電多數屬於B類,如洗衣機,其安全隱患與電控門鎖或馬達熱關斷有關。

IEC60730附件H的表格H.11.12.7列出B類和C類軟體須測試的微控制器元件、須檢測的故障和接受的安全措施,檢測內容包括監視CPU(暫存器和程式計數器)、中斷(處理和執行)和時鐘頻率,檢驗隨機存取記憶體(RAM)、非揮發性記憶體(快閃記憶體和EEPROM)、外部通訊以及周邊設備。

RAM測試問題多如牛毛

這些檢測均在微控制器引導過程中,甚至在系統執行代碼前完成,主要原因是RAM測試具有破壞性,可導致初始化的變數損壞。

在RAM檢測中,標準要求B類設備定期做單一位元直流電(DC)故障檢測,如嵌入記憶體固定故障或耦合故障。因為多數入門級微控制器的靜態隨機存取記憶體(SRAM)無校驗位元,所以該檢測必須由軟體來完成。

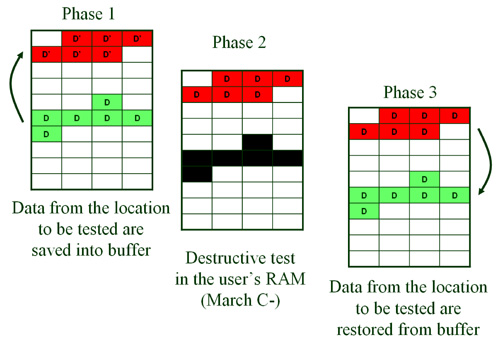

March演算法透過限定數量的測試來發現這些故障,March C測試最適合B類(使用10N次測試,N為被測試儲存位址的數量),但是March X(6N次測試)在某些特定情況也被測試機構接受。測試完成後,RAM記憶體內容被清除,因此又稱為破壞性測試。

重置後執行March測試,不會產生特別的問題。除略微降低開機速度外,沒有什麼實際缺點,因為嵌入式SRAM很小,開機速度降低甚至都不會被注意到。

相反地,如果在工作期間重複這個測試,可能會產生很大的問題。

首先,測試必須透明:毋須應用特定的協定即可處理RAM,就好像沒有測試一樣。

實際而言,這增加了下列兩個條件:第一,測試必須是一個中斷處理常式(ISR),且給予最高的處理優先順序,可禁止應用程式在測試過程中存取資料;第二,必須配備暫存,以便提前備份被檢驗的RAM內容,最後在應用任務重新執行工作前恢復RAM內容。顯然,也必須定期檢驗證暫存。

其次,應用任務暫停時間不宜過長。該測試通常分為若干個小測試,以限制占用頂層任務的時間。

一次測試的位址不得少於三個連續位址(這是耦合故障測試覆蓋率的硬性要求),這表示不少於三十次連續的March C演算法讀寫操作。

雖然實際應用證明該解決方案效果不錯,而且在業界十分流行,但還是存在不少的缺點。先從軟體工程角度剖析這些問題。結構化程式設計的優點略過,只分析相關的局限性問題:

| ‧ |

|

| |

C模組必須將部分內部變數提高至全域變數,不再接受編譯器參照跨模組存取進行的完整校驗。 |

| ‧ |

|

| |

測試對每個安全關鍵的軟體模組強制進行存取測試,使增加新功能變得更加複雜。 |

如果將資料損壞的機率與讀寫次數聯繫在一起,該解決方案的資料損壞風險會比較高。雖然逆向冗餘儲存安全關鍵變數可降低風險,但同時也會擴大記憶體B類測試的容量。

從微控制器資源角度看,測試代碼占用唯讀記憶體(ROM)和RAM空間,以及CPU頻寬,因為除正常處理任務外,如果內核臨時無法吸納測試負荷,就必須在家電工作關鍵階段終止測試。

最後,工作時RAM校驗會影響即時回應性(可能延遲甚至暫停其他中斷處理常式),並可能與低延時或緊急任務要求衝突。測試程式的代碼長度無法最小化,因為耦合故障測試對被測連續儲存位址的數量有下限要求。

如果軟體還必須管理位址解擾(Descramble),使其符合記憶體物理布局,則複雜度更高。圖1顯示軟體如何在工作時處理部分RAM測試。

|

| 圖1 軟體在工作時處理部分RAM測試 |

硬體校驗 另闢蹊徑

IEC60730標準另外提供一個由硬體校驗位元組成的解決方案。雖然這是一個標準的動態隨機存取記憶體(DRAM)流程,但很少用於通用微控制器。不過,先進的晶片製程節點使得該方法更具成本效益。

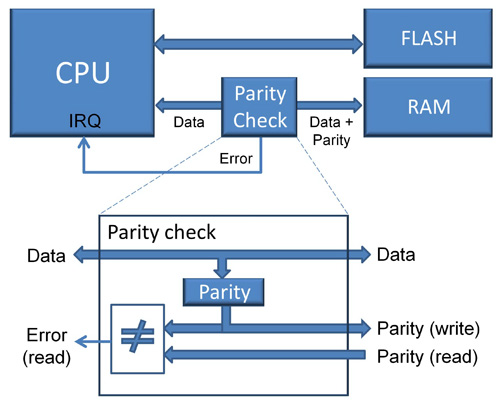

硬體測試解決方案的本質是在每個儲存位址增加一個校驗位元。記憶體每寫一次,就計算一次校驗位,並將校驗位元計算值與資料儲存在一起。當讀取資料時,同樣計算校驗值,然後與參考值對比(圖2)。

|

| 圖2 讀取資料時,會先計算校驗值,再與參考值對比。 |

如果數值不同,無論是資料損壞還是校驗位元損壞,中斷或異常訊號線都會被宣告。處理器內核將使用一個專用安全中斷處理常式處理錯誤,並關閉家電的電源。第二步,內核可能重啟應用(熱重置)或停止家電工作,同時顯示檢修代碼。

該解決方案的優勢十分明顯。B類RAM校驗變得完全透明,因為不影響軟體發展方法;不必開發某一個微控制器廠商專用的測試程式,只須開發一個在任何情況下都會出現的全域故障處理函數;無需專用的RAM分區和連結腳本;不占用CPU頻寬(校驗不會增加記憶體讀操作延遲);最好的即時性能。

最後一個優勢是該解決方案在啟動時毋須進行完整的RAM校驗,而且在上電重置後,奇偶校驗立即啟動,因此降低了前置時間。

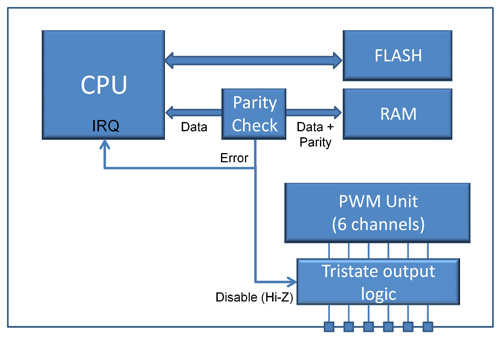

由於擁有高能效、靜音執行、高可靠性的特點,無刷馬達被廣泛用於家電,但需要複雜的控制演算法和專用的脈衝寬度調變(PWM)周邊設備,且須特別注意故障防護和安全關機。因此,RAM校驗機制可提高可靠性和回應性,不是用軟體管理安全關閉功能,而是直接向PWM周邊設備發送校驗錯誤訊號,自動觸發緊急停機功能,避免系統時鐘和軟體相關的延遲。圖3所示為一個實用的解決方案。

|

| 圖3 RAM校驗機制解決方案 |

此外,還必須注意系統的其他關鍵參數。電源監控系統可以設置電壓,如果Vdd電壓降至預設電壓值,系統將發出一個中斷命令。同樣地,時鐘安全系統檢查主時鐘工作是否正常,如果出現異常,則發出一個中斷命令。

再者,當發生硬故障、在非遮罩式中斷(NMI)處理常式內部出現錯誤或者在引導過程中發生匯流排故障時,Cortex內核進入鎖保護時態,在晶片級提供一個狀態顯示訊號。這三個事件以及校驗值合併,產生一個內部緊急關斷訊號,訊號本身與外部斷路(Break)輸入進行或運算。

IEC60730附件H規範還需要一個防失效時鐘電路。當晶振失效時,時鐘安全系統周邊設備(CSS)可以自動地將主時鐘切換到內部高速振盪器,從而實現部分防失效功能。

此外,還需要一個透過對比外部預計頻率與內部頻率來監視外部時鐘的方法。即時時鐘計時器可由LSI(內部低速)電阻電容振盪器驅動,以便精確地測量主系統時鐘,發現晶體副諧波引起的50%的變化。在系統級,這可節省50/60Hz電網過零檢測電路的成本。

IEC60730標準提出一個獨立的時隙監視方案,防止CPU在程式計數器故障時失控,這是看門狗計時器(Watchdog Timer)的職責,多數微控制器均內建看門狗。但是,標準規定看門狗必須完全獨立。

例如意法半導體(ST)的32位元Cortex-M STM32系列微控制器即搭載兩個看門狗,第一個視窗看門狗使用主時鐘,第二個看門狗使用獨立的內部振盪器,透過快閃記憶體內的選項位元組啟動。這種設計可確保在晶體失效時,無論時鐘電路配置如何,都能確保至少有一個看門狗維持在工作狀態。

最後,微控制器還內建一個32位元硬體迴圈冗餘校驗(CRC)計算器,可大幅加快快閃記憶體內容完整性檢查,同時將相關CPU負荷(在執行時占用的時間)降至可忽略不計的水準。

該周邊設備甚至可以用直接記憶體存取(DMA)控制器驅動。在微控制器工作期間,快閃記憶體資料完整性檢查可在後台進行。

硬體校驗長期以來只用於電腦DRAM模組和高可靠性系統,而今該方法已被引進嵌入式市場的通用微控制器,如基於Cortex-M0的STM32F0x產品,隨著系統監控和安全功能數量日益增加,該方案可簡化產品認證、安全開發的執行,最重要一點是使家電變得更安全。

(本文作者任職於意法半導體)