隨著設備互聯在物聯網(IoT)和機器對機器(M2M)通訊應用中越來越普及,基於快閃記憶體之FPGA可提供安全IP和硬體信任根(Root of Trust)以保護設計避免被入侵。

數位訊號處理器(DSP)的設計,如果本身沒有足夠的安全能力,便很容易受到入侵。在許多應用中,如果搭配FPGA來卸載DSP的部分工作,便可以實現先進的安全功能。而且,如果配合的FPGA使用快閃記憶體技術,在晶片上儲存結構中的配置位元流以及關鍵的安全金鑰資訊,便可以實現防止複製或仿製的固有安全性,自動保護設計以避免這些類型的剽竊。

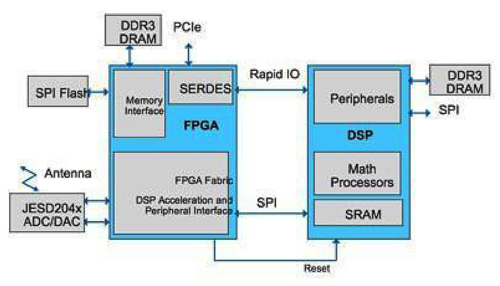

DSP和FPGA的系統結構

在使用FPGA或DSP的系統中,如圖1所示,DSP實施高等級的訊號處理演算法,而FPGA則實施前端降頻功能(Front-end Decimation Function)。高速串列RapidIO匯流排可連接FPGA和DSP;FPGA還會連接至PCIe匯流排,經由網際網路作為遠端接入管理埠。PCIe匯流排還可橋接進入和離開RapidIO匯流排的通訊量,以便將遠端系統管理的連接性擴展至DSP。FPGA控制外部DDR3 DRAM,後者可為進入和離開無線介面的資料封包充當緩衝器(Buffer),並可讓FPGA將DSP中任何低階的資料協定處理工作和緩衝管理功能卸載下來。

FPGA還負責從外部的SPI快閃記憶體引導(Booting)DSP,FPGA使用自身的SPI記憶體作為DSP的代碼來源,利用來自DSP的SPI埠的導引功能來映射引導過程。一旦代碼傳送完成,FPGA便會讓DSP開始執行。

|

| 圖1 使用FPGA和DSP的無線通訊系統 |

硬體信任根

如果系統並未對引導過程提供保護,侵入者便能夠以自己的代碼取而代之,然後成功劫持整個系統,這可能會使得系統受到破壞,引起重大的財務損失甚至法律責任。我們必須使用安全的導引過程將這類攻擊減至最少,而硬體信任根(Root of Trust)就是實施安全導引過程的必要條件。

硬體信任根支援系統資料完整性和保密性的驗證,並可將這種信任擴展至內部和外部實體。硬體信任根可避免系統被侵入或修改,也能夠查驗更高等級功能,而且是安全的起點。在嵌入式系統中,信任根與其他系統元件共同工作,以確保主處理器僅使用經過授權的代碼來進行安全的導引,從而將信任的區域擴展至處理器及其應用。

硬體信任根必須在安全的FPGA上構建,其配置位元流必須受到保護,以免不懷好意的入侵者成功進行複製或反向工程,使得信任根被破壞。所以,保護FPGA元件的IP是保護嵌入式系統其餘部分的必要條件。

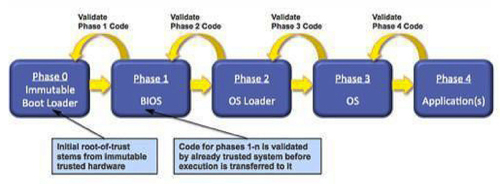

多級導引過程的安全要求

從其他部分進行嵌入式處理系統的初始化,需要安全的導引過程,以確保過程中所執行的代碼是可信任及不受惡意內容或洩漏影響。圖2說明了安全導引過程為充分保護嵌入式系統的初始化而必須經過的各個不同階段。每一個階段都必須由先前的成功階段來驗證,以確保直到頂層應用層的信任鏈(Chain of Trust)。不可修改的引導載入程式(階段0)代碼可嵌入在FPGA元件中,並且透過安全的信任根使用受保護的安全金鑰和相關的安全演算法進行驗證,以確保代碼的完整性和真實性。把代碼執行和轉移至安全導引的每一順序階段前,這些階段都必須經過先前可信任系統(Trusted System)的驗證。

|

| 圖2 多級安全導引過程概述 |

實施安全的嵌入式系統

配置位元流是在上電時使用(就像基於SRAM FPGA的配置位元流),而保護這些配置位元流的一種常用方法就是將位元流資料加密,這使得攻擊者難以在配置啟動過程中僅經由觀察來捕獲位元流。解密金鑰儲存在FPGA之中,用於在配置FPGA之前用來將資料解密。為了在失去電力時還能保留安全金鑰的資訊,因此通常須要使用電池。

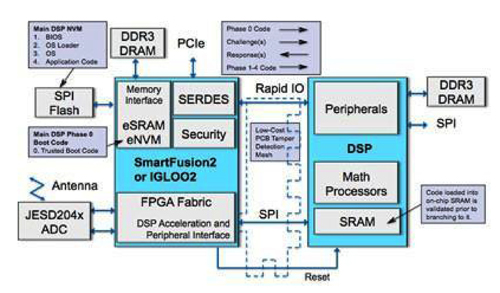

另一種保護FPGA配置位元流的方法,是使用非揮發性記憶體將其完全儲存在晶片上,以免在啟動時洩露。市場上有一些FPGA元件,比如美高森美的SmartFusion2和IGLOO2系列,在製造期間進行程式設計時將位元流加密,提供了額外的保護功能;這還可保護設計不會被不道德的代工廠進行複製或反向工程,以免所需的硬體信任根遭到破壞。

一旦創建了安全的FPGA,下一個主要的要求就是實施硬體信任根。FPGA必須保護安全金鑰和晶片上不可改變的初始階段(Phase 0)導引載入程式,使得惡意侵入者無法以任何方法攻擊或修改它們。如果使用基於快閃記憶體的FPGA將不可改變的代碼和安全金鑰儲存在晶片上,還可經由配置過程來載入配置位元流以獲得安全性。安全金鑰只是整個設計中的一小部分,但對於保護設計避免其它形式的攻擊卻是十分重要的。

阻止攻擊

一種常見的攻擊方法是使用側通道(Side-Channel)分析來試圖找出晶片上的安全資訊,比如觀察安全金鑰相關運作期間的功率或定時簽名。這種側通道方法類似保險箱竊賊不斷操縱鎖具和偵聽機心的雜訊來找出保險箱組合的方法。在這種情況下,側通道就是通過物理方法實施安全「功能」所造成的聲音。實施耐受側通道攻擊的解密演算法,也可以耐受更先進差分功率分析(DPA)形式的側通道攻擊。

如果不使用耐受DPA技術,觀察者便能測量到該設計在處理金鑰和演算法時所使用的功率。此外,頻繁改變安全金鑰也可限制攻擊者針對統計分析所進行的測量次數,使他們難以利用這類方法入侵。而且預充電的暫存器和匯流排等電路設計技巧也可限制入侵者所能夠利用的「雜訊」。

既然已保護了FPGA IP的安全,設計也建立了信任根,所以便能夠更詳細地檢視整個嵌入式系統的實施方案。圖3所示為安全的嵌入式系統的實施方案,其中描述了安全導引過程的不同元件。不可改變的導引代碼與金鑰儲存在晶片上,外部SPI記憶體儲存剩餘的DSP代碼(包括任何所需的OS載入程式和OS代碼,以及應用程式碼),全部均使用由信任根所管理的安全挑戰和回應系統(Challenge and Response System)來驗證。過程結束時,安全的代碼被載入DSP晶片上的SRAM,FPGA便讓DSP開始運作,確信只會執行經授權的代碼。此外,使用FPGA I/O可實現低成本PCB篡改檢測方案,以檢測任何鑽孔或切割跡線意圖,並採取保護措施。

|

| 圖3 使用SmartFusion2或IGLOO2 FPGA的安全實施方案 |

當完成了安全導引,FPGA便能夠實施系統所需的其它功能,比如橋接PCIe和RapidIO介面、連接JESD204x匯流排、利用FPGA模組預處理無線訊號,以及控制DDR3緩衝記憶體。當需要額外的演算法處理能力時,SmartFusion2具有晶片上處理器可供選擇;而當FPGA模組足以實施所需的控制功能時,也可選擇使用IGLOO2。

基於快閃記憶體的FPGA可提供安全IP和硬體信任根,可用於構建更高等級的安全功能,如安全導引等,以保護設計避免被侵入。未來的安全需求將以這些功能為基礎,例如傳送安全資料和授權安全設備將成為新興物聯網和機器對機器通訊應用的主要需求,這些應用將是許多新DSP相關設計所鎖定的目標。這將需要數種額外的設計安全層以保護嵌入式系統設計IP。

(本文作者為美高森美策略行銷總監)