由於TSV技術可實現3D IC異質整合的架構,將TSV鑽孔用作異質晶片訊號傳導媒介,因此在消費性電子產品訊號處理特性與尺寸縮小需求下,CMOS影像感測器成為率先導入3D IC的元件,並可開發更多新應用。

過去1年受到金融海嘯的衝擊,各家半導體公司經濟狀況不好,於是更有時間專注於新世代的技術開發,各家公司研發設計功力可謂大躍進,直接跳到下一世代的製程設計。2009年可說是3D IC的元年,而2010年各家廠商在3D IC產品的呈現將會出現爆炸性的成長。

本期針對3D IC其中的一個重要應用,也就是互補式金屬氧化物半導體影像感應器(CIS)加以討論。這是因為3D IC的其中一個優點即異質整合,也就是可將不同的晶粒(圓)堆疊起來。在目前所有的消費性電子產品中,因訊號處理特性與尺寸縮小需求,就以CIS最適合應用3D IC技術實現。

CIS應用漸趨多樣化

CIS或稱為單片主動式光點感測器(Monolithic Active Pixel Sensor, MAPS),影像感測器的市場起始於數位相機與錄影機,但目前最大的應用卻是在手機市場,另外,影像感測器也有些熱門應用,如線上會議系統、網路照相機、企業應用、安全監控相機。除此之外,其應用範圍至少包含以下幾個方面:

| ‧ |

|

| |

微飛行器(MAV)/無人飛行器(UAV)為無人駕駛飛機上用於偵測地面影像,或者透過影像偵測高度與避免載具前進時與前方物體如山或牆壁碰撞。MAV/UAV通常搭配兩個影像感測器,分別是前方感測器(Forward Sensor)與下方感測器(Downward Sensor)。前方感測器用以根據前方的光流量偵測前方的阻擋物,量測間距速度(Pitch Rate)與偏航率感測器(Yaw Rate),利用的原理是通常前方的光流量會較高;下方感測器用以根據光流量偵測下方的高度,量測間距速度與滾動速度(Roll Rate),利用的原理是一般通常下方的光流量較高的部分,即為高的物品(Tall Object)。 |

| ‧ |

|

| |

感測器在汽車領域,也就是車用電子的架構。影像感測器在汽車的使用族群為頂端客戶,使用包含航道偏移警告、視覺死角偵測、夜間紅外線視覺、駕駛員監控、停車輔助、行人偵測、360度視角、車禍意外量測等。這些應用都會因為影像感測器的成熟與量產而變得可行。 |

其他應用包括智慧型手機與內視鏡的照相或攝影、仿生昆蟲眼睛的機械蒼蠅(MFI)、環境監控與安全監控,如指紋辨識,專注於此類的公司有富士通(Fujitsu)與Secure Design。此外,影像感測器還可用在文件的掃描記錄、玩具上的視覺、太空科技、機器視覺系統或美光(Micron)所發展的診斷儀器CIS,以及純科學方面的應用,如MIT利用影像感測器於雷射雷達的成像,或高能物理(HEP)中會用到的矽頂點控制器二(SVD2),即追蹤粒子衰變軌跡相當關鍵的儀器,發展廠商如德國Fermilab。除了這些應用,在科學應用上,還包括以下的應用:

| ‧ |

|

| |

例如醫學上用以偵測X光(X-ray)波段的光線,如R.A. Turchetta and A. Clark and J. Crooks等人所製作的Vanilla,此CIS可以用以偵測紫外線(UV)到紅外線(IR)的波長(1,100奈米)。若是進一步將背部薄化及使用背面照度(BSI),那麼還可以偵測到超紫外光(EUV)波長;若是結合有機閃爍偵檢器(Scintillator)還可以將X-ray轉換為可見光,使CIS可用來偵測X-ray。只是由於閃爍偵檢器特性的關係,所以CIS必須作相當大的面積,R.A. Turchetta等人製作的大區域感測器(LAS)晶片就是用來偵測X-ray。 |

| ‧ |

|

| |

目前諸多的CIS製造商都已經可以製造可偵測近紅外光(Near-infrared, NIR)的CIS。NIR原先使用於科學應用中,目前已經可以使用在汽車的夜視應用中。著名的CIS設計公司Omnivision早在2007年就已經成功的設計可以適用於汽車電子的CIS。 |

3D影像感測器漸受重視

下一代的的影像感測器不只可以檢測透過透鏡的光線強度,也可以量測物體的距離,或進一步抓取三維(3D)影像,以利自動對焦的需求,因此,未來數位相機必然會利用此特性創造另一個市場。3D影像感測器還可應用於汽車電子,如Canesta就是專門設計一種用於車用的3D影像感測器的公司。

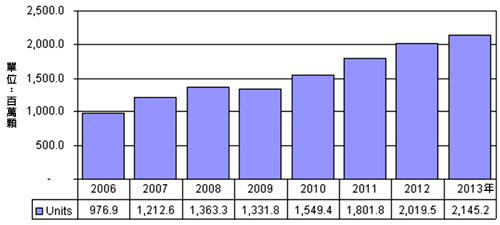

根據iSuppli對全球影像感測器市場的分析,其認為具3D功能的數位相機,市場將超過目前的兩倍,以2009年來說,全年感測器的市場超過十三億三千萬顆,較2008年的十三億六千萬顆少,但到2012年,全球的影像感測器市場就會超過二十億顆(圖1)。根據其分析,2010年超過十億顆的感測器會裝置在手機上面。但是,其另一個爆炸性成長的市場是在汽車電子上,iSuppli估計2013年的數量會高達一千四百六十萬顆,大約是2009年的三倍。

|

資料來源:iSuppli

圖 1 iSuppli對於全球影像感測器市場的預估 |

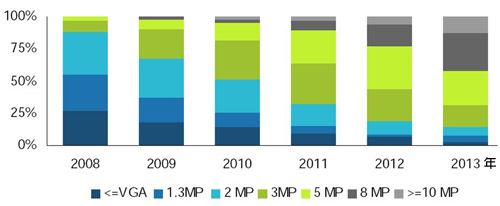

由圖2研究機構iSuppli在2009年第四季對於手機用不同畫素大小的CIS市場預估,可以看到三百萬畫素是市場占有率最大的一個規格,但五百萬畫素畫素卻都是目前成長最大的一個產品,其最慢會在2012年超越三百萬畫素,但五百萬畫素並不會存在太久,因為到了2013年,其主流產品將會是八百萬畫素。

|

| 圖 2 2008~2009年手機用CIS產品市場預估 |

TSV技術正式切入市場

本文所謂的3D IC就是以晶元堆疊與晶元片堆疊為主,並結合矽穿孔(TSV)的一種半導體製程技術。從結構上來看,3D IC至少提供以下這些優勢:

縮小外觀尺寸

一個3D IC可以在1平方公分面積上提供高達四萬到十萬條連接線,速度可達1Tbit/s,這是目前以封裝技術為主IC的十倍速度。相對於傳統的封裝技術,其每一個焊球(Solder Ball),大小約為100微米(μm),間距約需200微米,但若用3D IC,則其微接點(Micro Joint)大小不大於20微米,間距也只不大於50微米。

增加頻寬與速度

若可把動態隨機存取記憶體(DRAM)堆疊到中央處理器(CPU)上方或下方,這些記憶體就可以視為CPU的快取記憶體(Cache),這些記憶體過去都是晶片外(Off-Chip)的,也都是系統頻寬的最大瓶頸之處。堆疊CPU與記憶體,也就可以大量增加快取記憶體。根據英特爾(Intel)的研究,為CPU增加32M~64M的快取記憶體,可以讓Off-Chip的記憶體頻寬需求降低三倍,且效能可提高15%,功耗可減少15%。

降低功耗

以通訊產品而言,IBM估計其一個矽鍺(SiGe)製程的無線通訊產品,使用3D技術將可提高40%的功效,並且減少20%的功率消耗。北卡州立大學教授W.R. Davis設計一個八千一百九十二點的3D IC FFT,得到的成果是其功率延遲積(Energy Delay Product, EDP)比過去的設計少36%。

降低生產費用

過去的系統單晶片(SoC)目標就是希望將各個獨立的IC整合,希望透過SoC可減少面積與封裝需求,並提高可靠度。但不幸的是,以一個汽車電子的SoC而言,可能要將邏輯電路、類比電路、快閃記憶體等全部整合在一起,其製程與設計上的整合太多,代價也太高,電路效能也不一定好。所以若可用垂直整合的方式,各個原有模組可以繼續用傳統較低階的製程,最後以3D整合的方式將其堆疊,這樣的費用將比SoC還低。

改善可靠度

對於3D IC,因可用較舊的製程設計元件,若是以CMOS製程設計,使用舊的製程(如0.35微米技術)設計數位電路,其漏電流或IDDQ與暫態電流差距會較大,所以IDDQ測試又可用來提高測試的品質。對CMOS一些較不常見的錯誤,如Gate Oxide Short、Bridge、 Parasitics、PN Leakage、Punch Through、Open Drain、Open Gate都可輕易的用IDDQ測試偵測出來。

提供異質整合

以一般的CPU而言,其需高速的邏輯運算,也需大量的記憶體,若是用DRAM當內部記憶體,必定會有製程不同的困擾。因DRAM的製程與邏輯製程不同,這是由於邏輯電路和DRAM的製程各有其需求與特性。若使用3D IC,這種須異質整合而犧牲各自效能的情形就可改善。

減少ESD需求

3D IC可減低靜電放電(ESD)需求。因要堆疊的兩個IC,若原先需要晶片到晶片(Chip-to-Chip)的相接,現在只要直接透過垂直的匯流排就可相接,雖然是兩個IC相接,如一個記憶體與一個微處理器,但是,這個記憶體卻可直接視為是這個微處理機的內嵌式記憶體,所以不用為此記憶體設計輸入/輸出(I/O)。因此,過去在I/O上努力考慮的人體接觸模式(HBM)與機器放電模式(MM)似乎也毋須考慮了,亦即只須考慮元件充電模式(CDM)。

提高散熱效果

根據EMC 3D組織的說法,3D IC比傳統的系統級封裝(SiP)散熱效果更好,這是因為TSV除可當訊號線外,也可用來散熱,這也就是所謂導熱孔(Thermal Via)的構想。在恩益禧(NEC)對一個八層堆疊DRAM的散熱分析,TSV的散熱效果比傳統用打線接合(Wire Bonding)的方式高達二至三倍。

提高良率

3D IC提供一個軸向的自由度(Degree of Freedom),這個軸向的電路可幫記憶體提供更好的修護能力(Reparability),也就是因為多了一個空間電路,可讓電路設計師或測試工程師有更多的設計與容錯空間,因此良率可提高。

提高資料安全性

過去SoC可用去氧樹酯(De-cap)的方式作返向工程(Reverse Engineering)。但若針對3D IC,其危險度將增高,因有兩層的晶圓(Wafer)或裸晶(Die)黏接在一起,若用De-cap將會破壞IC結構。另外,蝕刻動作也相對困難,因為每一層的厚度變化比原有的單一個晶圓更厚,所以蝕刻會更加有問題。最後,因有更多個訊號層堆疊,若用影像感測電壓的方式,會造成影像很模糊而無法辨認。

可延展性/可規畫性/可替換性

從上述的討論可知,3D IC可提供彈性的連線機制,因此,也提供更高的容錯空間,達到更好的可靠度與良率,這些都是需要相當高的可規畫性。3D IC因為多了一度的自由空間,因此不管是在電路的合成階段或在系統整合階段,3D IC可使電路的呈現更為彈性。

簡易的互連體

相較於SiP採用打線接合或覆晶技術達到3D堆疊,以TSV為基礎的3D IC不僅可縮短連線距離,節省插入式選樣(Interposer)或導線架的使用,大幅減少晶片厚度與材料成本,更可提升晶片效能,降低電磁干擾(EMI)與功率消耗。根據EMC 3D組織的說明,3D IC可提供更簡單的插入式選樣。

有人認為高速的影像處理系統是3D IC的第一個應用,因為在二維(2D)的環境上根本作不到如此高速。影像感測若是可以3D堆疊,焦平面(Focal Plane)上的主動式畫素(Active Pixel)就可很近的與後端電路作讀數(Readout)、放大(Amplification)與訊號整合(Signal Integration)作垂直整合。因為,光感測(Photodetection)元件基本上是一個2D元件/陣列,這些元件/陣列可形成一個智慧型陣列(Smart Array),也就是檢測到訊號後,直接透過垂直的第三度空間TSV送訊號到上/下面的訊號處理電路。

3D TSV的技術好處相當多,但不同的CIS特性影響結構甚鉅。若不是用晶圓BSI,CIS的晶粒一定向上,TSV就必須根據BGA的落角設計。在參考資料所列的文章中,就有談到CIS設計(含TSV)技術的挑戰,包含光學設計、鏡片材料、量測、晶圓級封裝以及智財權的問題。

(本文作者依序為工研院資通所專案副組長、南台科技大學科技管理研究所助理教授)