ARM、新思科技和Imagination等IP開發商近期不約而同布局物聯網IP子系統,提供包含低功耗處理器、無線通訊、傳輸介面等IP,以及軟體開發平台的完整設計解決方案,點燃新一輪技術戰火。

物聯網已成矽智財(IP)商兵家必爭之地。安謀國際(ARM)、Imagination在2015年台北國際電腦展(Computex)競推低功耗IP、安全防護方案,同時也加強與晶圓代工廠在低耗電、嵌入式記憶體製程上的合作,甚至進一步提出物聯網IP子系統的嶄新概念,目的皆是為各類物聯網設計灌注能量,以快速拱大市場。

因應對手動向,新思科技(Synopsys)近期也與台積電攜手開發40奈米超低功耗(ULP)製程,將用於整合旗下超低功耗ARC處理器、記憶體編輯器、無線通訊、類比數位轉換器(ADC)、行動產業處理器介面(MIPI)和通用序列匯流排(USB)等核心,加入這場物聯網IP平台戰局。

完備IoT生態鏈 ARM IP子系統上陣

ARM先前宣布收購藍牙智慧(Bluetooth Smart)技術協定與配置業者Wicentric和藍牙通訊IP供應商SMD(Sunrise Micro Devices),新的Cordio產品線即是整合兩家公司的IP產品所推出,與ARM現有處理器和實體IP產品緊密搭配,鎖定物聯網低功耗無線通訊的終端市場。

|

| 圖1 ARM技術營運執行副總裁Dipesh Patel強調,ARM推出無線IP有助於促進物聯網設計成熟。 |

ARM技術營運執行副總裁Dipesh Patel(圖1)表示,裝置與裝置的相互連結越來越緊密,然目前沒有單一的解決方案能滿足物聯網多元應用的特性;因此ARM推出全新的Cordio無線通訊IP和物聯網子系統,提供一個完善的系統架構,可協助客戶快速且有效開發智慧聯網裝置高度客製化晶片,在智慧家庭和汽車產業等領域上掌握先機,滿足物聯網多元需求。

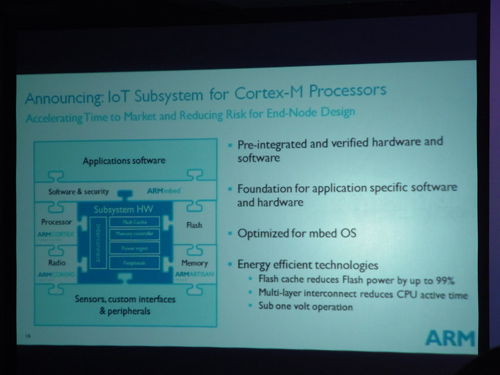

Cortex-M處理器專用物聯網子系統(IoT Subsystem)(圖2)和Cordio無線通訊矽智財,前者採用台積電55奈米(nm)超低耗電製程技術,可縮小晶片體積、降低成本和功耗,且可在1伏特以下(Sub-one Volt)的電壓運作;後者具備低功耗訊號傳送特性,並降低電力使用,兩者皆有助加速未來物聯網晶片的開發時程。

|

| 圖2 物聯網IP子系統設計概念暨架構圖 資料來源:ARM |

Patel指出,2009年技術革新主要在於消費者體驗、產品性能與設計、電池壽命等改變,2010年則是聚焦於行動運算、服務和應用程式的變遷,直到2012年,上千種手機和上百種平板電腦的高出貨量,使得整體行動產業達到上兆美元的產值,銷售量明顯超越桌上型電腦,帶動智慧聯網晶片和感測器需求湧現。

Patel進一步分析,至2030年則將有數以千億的智慧聯網感測器面市,對高度客製化晶片的需求將與日俱增。感測器未來將遍布於日常生活當中,像是在農作物生長檢測、交通監測等,這些設計將邁向更簡便、更容易,且同時要兼顧感測器效能和資訊安全,更重要的是,必須擁有更強大的續航力。

新款子系統IP模組與Cortex-M處理器、Cordio無線通訊IP組成物聯網終端(Endpoint)晶片設計基礎,客戶只要整合感測器和其他周邊元件即可完成完整的系統單晶片(SoC);另外,該設計也採用Artisan實體IP,且以台積電55ULP製程技術進行生產,兩者的結合可用低於1瓦(W)的功率運作,延長電池壽命,符合智慧物聯網裝置設計需求。

Imagination瞄準物聯網 祭IP/安全防護雙重攻勢

同樣基於物聯網IP子系統的出發點,Imagination也開始統合旗下MIPS處理器IP、Ensigma Whisper無線連結IP陣容,並進一步發表系統單晶片(SoC)安全防護軟硬體方案--OmniShield,以增加產品在物聯網設計領域的戰鬥力。

|

| 圖3 Imagination市場行銷執行副總裁Tony King-Smith指出,物聯網So C功耗控管必須從半導體晶圓製程就開始做起。 |

Imagination市場行銷執行副總裁Tony King-Smith(圖3)表示,對物聯網IP子系統而言,改搭低功耗製程,確保處理器核心與無線通訊IP緊密互通將是箇中關鍵,因此該公司近期不僅加碼研發超低功耗嵌入式記憶體製程,亦大舉拓展Wi-Fi、藍牙Smart和6LoWPAN無線連結IP產品線,以加速落實物聯網IP子系統。

另一方面,閘道器、路由器、行動裝置和聯網汽車等皆須在資料安全無虞的前提下,支援獨特應用程式、各種內容來源,以及服務供應商和電信業者的現場軟體更新作業。由於多種應用程式和相關資料同時存在於相同的SoC上,因此每個應用程式都必須具備更高的安全性,才能免於受到外部攻擊和彼此的影響。

對此,King-Smith強調,OmniShield是專為確保行動裝置及物聯網設備SoC安全性所開發的可擴充性解決方案,可超越傳統二元式做法,建立多個安全域(Secure Domain),讓每個安全、非安全的應用程式、作業系統能在其個別環境中獨立運作。由於其兼具硬體虛擬化IP防護與動態軟體管理能力,將有助晶片業者及OEM全面提升系統可靠度,並能因應各類聯網裝置不斷演進的使用模式與服務型態快速調整設計。

事實上,物聯網不僅牽涉複雜的軟硬體生態系統,亦須仰賴產學多方合作,才能落實應用創意。基於此一考量,新思科技即發動台灣物聯網產學合作首波攻勢,宣布攜手台灣大學、清華大學、交通大學和成功大學,在各校成立「IoT物聯網應用設計實驗室」培育人才,並將貢獻旗下低功耗CPU IP技術與設計知識,以及處理器編程、軟體開發與偵錯等工具,幫助學術界研究人員加速物聯網半導體軟硬整合和設計驗證,進而無縫接軌商業應用。

催速半導體軟硬整合 新思成立物聯網實驗室

|

| 圖4 新思科技董事長暨共同執行長Aart de Geus表示,完整的物聯網軟硬體解決方案將有助降低系統整體開發成本。 |

新思科技董事長暨共同執行長Aart de Geus(圖4)表示,物聯網是巨量資料(Big Data)、雲端應用及多元軟硬體技術的代名詞,而空間、功耗和成本則是其設計成功的關鍵要素,必須仰賴高度的半導體軟硬整合方能實現。基於此概念,新思遂不斷擴大在台投資,期借重台灣上下游半導體產業鏈及學術研究能量,完全發揮旗下低功耗ARC處理器IP、軟體開發套件(SDK)和電子設計自動化(EDA)工具的優勢,以加速實現物聯網軟硬整合設計。

台灣新思科技總經理林榮堅補充,新思近期與台灣四所頂尖大學共同成立IoT物聯網應用設計實驗室,可望搭建產學溝通橋梁並擴大物聯網商用規模。這項合作計畫,新思將捐贈ARC EM Starter Kits及MetaWare Development Toolkits兩套ARC處理器軟體開發工具,加快各式基於ARC核心的軟硬體設計與驗證,並將幫助各校建立電腦工程學習環境、提供講師訓練指導與支援,目標係每年培育三百位以上專業人才。

林榮堅強調,時下火紅的物聯網設計--穿戴裝置、機器對機器(M2M)設備已帶來許多挑戰,開發者須綜合考量低功耗、高效能、小尺寸和豐富軟體應用,並在低成本前提下實現,因此全方位的軟硬體平台非常重要,將是縮短創意實現和產品上市的最佳途徑。

Geus認為,面對未來10年的物聯網熱潮,半導體產業已出現兩個重大轉變的初期跡象。首先是軟硬體價值鏈的翻轉,軟體工具重要性將日益突顯,引發軟硬整合的新議題;其次則是晶圓先進製程的加速演進,許多業界人士認為摩爾定律(Moore's Law)步調已開始延宕,但在物聯網設計驅動下,諸如鰭式電晶體(FinFET)等顛覆性的科技將在下一個10年不斷冒出頭來,推進摩爾定律腳步。而上述趨勢皆須透過深諳半導體軟硬體科技的廠商合作,以及綿密的產學交流才能達陣。