被半導體業者奉為圭臬的摩爾定律近年屢屢遭受挑戰,其中尤以3D IC的出現最具威脅,甚至頗有可能將摩爾定律推向歷史。但儘管3D IC話題持續升溫,但究竟又有多少業者、組織已經真正開始投入?投入力道的強弱與重心為何,將成為決定3D IC盟主的關鍵。

40多年來,半導體產業依循著摩爾定律(Moore's Law),穩定地增加電晶體的數量,並藉由縮小幾何形狀,讓更多的功能設計在一個積體電路的晶片中。在摩爾定律持續地發酵下,追求縮小尺寸與功能的增加,電晶體的尺寸很快就會到達半導體技術製程的極限。以目前最先進的電晶體大小大約是30奈米,相較頭髮直徑,僅有約三千分之一。而這種極限該如何突破,也一直是半導業探討與追求的主軸。

近年來,持續引人注目的解決方案,是透過垂直堆疊積體電路晶片或垂直封裝,被稱為3D IC的應用。而讓3D IC得以實現的關鍵技術,則是利用矽穿孔(Through Silicon Via, TSV)製程,形成垂直電性互連,堆疊矽晶片、IC或已封裝的晶片等元件。

而投入3D IC的基本原因,就是因為它可帶來更佳的性能、更小的尺寸與更低的成本。很明顯地,這也就是主要的趨動要素,透過TSV互連,IC不再只能在二維中發展。

立體堆疊技術多元 TSV最具競爭優勢

3D IC的應用,在全球半導體業界都正在大展身手。這種對晶片進行立體堆疊 的技術,雖有打線(Wire Bonding)、層疊封裝(PoP)、嵌入式(Embedded)、TSV及Edge Trace等方法,但目前僅以前兩項技術較成熟,並占八成以上的市場應用。然而,如先前提到的,遵守摩爾定律而發展的半導體產業,已逐漸看到其應用的瓶頸,再加上Edge Traces的技術,只有如VCI等少數晶片堆疊技術廠商已進行研發,在市場上卻仍未有定調,因此相較於其他的技術來看,主宰3D IC產業的關鍵技術,仍將是TSV的天下。

究竟TSV對半導體業的影響有多深,許多專家都認為,不論其導入的位置是在半導體製程的何項部分,至少從設計到封裝測試的價值鏈結構,都將因而進行部分的重整。透過研發聯盟來聚集3D IC基礎架構的能量,則是目前看來最可行的方向。這類聯盟的成立背景,都具有明確的發展路程,藉由會員提供各類核心技術,將可持續左右3D IC市場的未來。

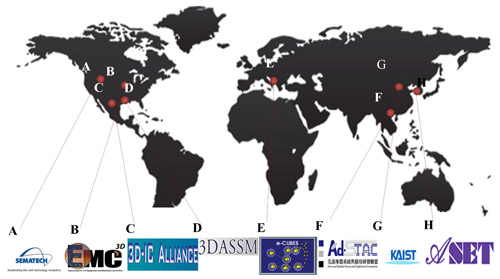

本文將針對全球幾個主要的聯盟(圖1),探討其會員組成以及規畫的策略核心,以窺見各自在未來3D IC技術應用市場中的潛能,協助業界理解出這些未來主宰應用的聯盟如何進行立體堆疊的研究。

|

| 圖1 3D IC聯盟全球分布圖 |

亞洲成明日之星

在近年亞洲地區的半導體大廠較勁下,都已在利基市場中站穩腳步,如整合元件製造商(IDM)較多的韓國、同時發展IDM與晶圓廠(Foundry)的日本,以及一向以垂直分工著稱的台灣,早已各據山頭,但卻又若即若離。近年來在3D IC應用漸露頭角的台、日、韓三國,都分別取得政府的資源,成立聯盟來整合能量,為的都是希望可以搶得先占優勢,以下便進行深入探討。

|

|

| |

簡稱為ASET的日本超先端電子技術開發機構(Association of Super Advanced Electronic Technologies),主導日本3D堆疊整合技術之國家型計畫。其成立的背景,在於研發先進技術來整合製造,以便讓3D IC達到效能與經濟的期望目標。

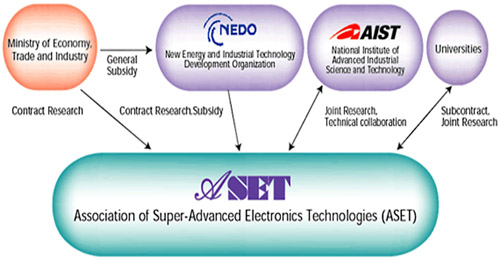

如圖2所示,ASET不只有來自於日本經濟部的計畫契約,並有國家級研究機構進階產業科學與技術學院(AIST)與其協同發展,更有來自學界的整合計畫能量。

|

| 圖2 ASET的研發能量 |

至於在業界的會員企業,則涵蓋元件製造商、系統終端商、材料與設備商達三十四家,諸如爾必達(Elpida)、IBM、英特爾(Intel)、恩益禧(NEC)、夏普(Sharp)、索尼(Sony)、東芝(Toshiba)等,研發能量十分可觀。

在3D IC開發方面,以目前由ASET所主導的3D整合技術(3D Integration Technology)為主要的執行計畫,預計從2008~2012年為止,其目的主要鎖定在發展可以提供多功能、高效能與低耗電的3D整合技術。相關內容包含設計環境、晶片測試、基礎整合技術等。而此計畫將以TSV為主軸,來進行各項條件的整合,並用來生產3D系統級封裝(SiP)的系統。

至於研發能量的產出,其實在3D整合技術的部分,自1999年起,ASET便已著手進行3D封裝技術的開發,期間共取得三百一十三份專利,出版五百三十八篇報告,但也僅限於電子系統整合封裝。

而自2008年啟動3D IC的整合計畫後,專利已取得一件,並發表相關文章共十篇。雖未能有顯著的研究產出,但擁有紮實的研究能量,想必在未來數年,將有更可觀的成績出現。 |

|

|

| |

位於新加坡的電子封裝研究聯盟(EPRC)是由新加坡微電子研究院(Institute of Microelectronics, IME)所主導,旨在提供平台供聯盟成員作資源和成本共享,以便將策略、技術與智財權累積,以滿足電子封裝的研發共通需求,並提供設計和製程指南。

EPRC聯盟的成員遍布全球,包含了電子產業及晶片之供應鏈,主要包括IC製造廠如聯電、英飛凌(Infineon)、日立電線(Hitachi Cable),封裝廠如STATS ChipPAC及UTAC等,材料與設備供應商如巴斯夫(BASF)、上海新陽半導體等。

自1996年起,EPRC持續注入許多寶貴的研發能力,不少跨國企業與當地組織均因此受惠。截至目前,EPRC持續成功突破許多關鍵技術,如無線傳輸所需新型尺寸的晶片封裝、高效能IC所需的黏合技術,以及通訊裝置所需的光學封裝等。

而此聯盟目前最大的計畫EPRC-9,則包括混合型立體堆疊與互連技術開發、應用TSV於銅/低介電常數之大型晶片封裝、嵌入式晶圓級封裝(WLP)以及高密度3D(High Density 3D)互連的低溫打線技術等四項專案。

至於下一步,新加坡微電子研究院在2009年6月時宣布啟動第十屆電子封裝研究聯盟計畫EPRC-10,其主要的研發是針對立體封裝的主要整合挑戰與嵌入式模組,其3D IC專案包含了設計使用已堆疊並包覆成形(Over Molded)的系統晶片技術來產出3D SiP、使用立體晶片對晶圓(Chip-to-wafer, C2W)混合大量接合的方式作異質晶片整合、研發於基底上作嵌入式薄型晶片,並完成可靠度等之特性分析,以及高密度立體嵌入式晶圓級構裝等。

新加坡微電子研究院目前積極在新加坡布局,研究開發12吋3D IC的完整生產線,第一期的目標是建立TSV設計和8吋、12吋TSV晶圓3D IC組裝,同時培訓一批在半導體供應鏈公司的人員,以支援3D TSV相關的技術與製程。第二階段將開發相關設備與工具,並整合到現有資源中,以延伸12吋晶圓製程生產線。 |

.台灣先進堆疊系統與應用研發聯盟

國內3D IC的推動,主要以工研院所組成的先進堆疊系統與應用研發聯盟(Ad-STAC)為主。一般認為,3D IC的出現,將會造成產業鏈的重新布局,而可以整合並提供IC產業上中下游資源的IDM,更被視為是最具潛力的要角。

有鑑於台灣垂直分工的IC價值鏈,若意欲推動立體堆疊技術,並非單一廠商所能決定。因此工研院率先成立先進堆疊系統與應用研發聯盟,結合產、官、學、研等組織,來協助廠商進入3D IC的世代,此聯盟的主要目的是為了探索3D IC技術、產品應用與市場、與全球組織協同合作、促進資源和矽智財的分享,以及建立認證測試設備和標準。

目前聯盟的會員陣容包含日月光、杜邦台灣(Dupont Taiwan)、矽品、阿托科技(Atotech)、美商亞普(Air Products)、應用材料(Applied Materials)、力鼎精密(Leading Precision)、休斯微技術(SUSS Microtech)與漢民等。

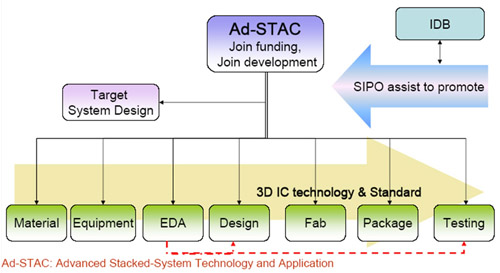

由圖3可以看到先進堆疊系統與應用研發聯盟企圖整合各種3D IC設計、技術、設備、材料、封裝與測試,以便發展出業界標準,來加速台灣3D IC的發展,並配合半導體產業推動辦公室協助推廣。

|

| 圖3 先進堆疊系統與應用研發聯盟布局 |

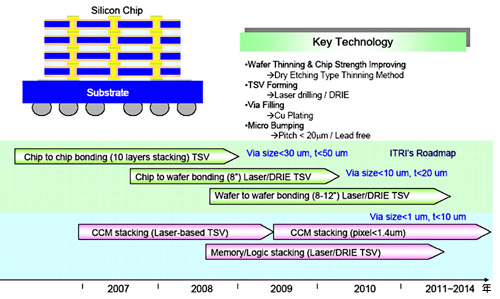

先進堆疊系統與應用研發聯盟主要對3D IC技術發展的規畫如圖4,其將於2010年後推出完整12吋晶圖的3D IC生產線。

|

| 圖4 Ad-STAC規畫的3D IC技術發展進路圖 |

其他宣稱可在2010年推出完整12吋雛型生產線的單位並不少,尚包括前文提及的新加坡的微電子研究院、位於歐洲的愛美科(IMEC)、CEALeti、IZM以及美國的Sematech聯盟等。相信在2010年之後,可以樂見全球在3D IC的應用逐漸水到渠成,並且日益邁向普及。

歐盟打造超級立體整合計畫

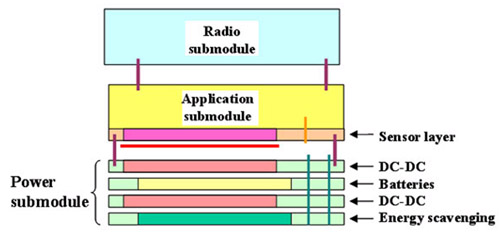

歐洲的半導體研發能量不可小覷,其中e-CUBES為歐盟資訊社會技術(Information Society Technologies, IST)組織的計畫,利用歐盟跨國成員的整合,來開發高度微型化的解決方案,以期能研發出3D整合無線感應系統。此系統將整合天線系統、被動元件、感應器、無線通訊介面及電源供應單元,以維持在通用與應用科技中的領先優勢如航太業的智慧型監控系統、汽車業的智慧型控制,和應用於醫療的無線感應器等。

e-CUBES的成員目前共十七個,其中包含有製程供應商如英飛凌、3D Plus、飛利浦(Philips)等、材料如Honeywell與設備提供者如Alcatel Alenia Space等。並結合跨國學界如波蘭、德國與瑞典之研究機構如德國IZM、法國CEA等,研發能量相當可觀。

e-CUBES為了整合各種異質系統,亦致力於高密度IC,以及多種異質晶片的堆疊,並由於其焦點在於應用科技之產品,於是在成本、可靠度及上市時間的改善上,也有相當之著墨。圖5為e-CUBES計畫中,將不同功能模組作3D堆疊的示意圖,可以看出其重點在於異質整合、微型化與元件的供電能力。

|

| 圖5 e-CUBES的3D模組堆疊架構 |

根據3D IC市場的一般看法,異質整合的應用,可能較互補式金屬氧化物半導體(CMOS)影像感應器與記憶體還要晚。其中除了技術面的考量,成本亦是一大障礙。歐盟的e-CUBES能在此時提出難度更高的3D堆疊計畫,正所謂藝高人膽大,有了實力雄厚的歐盟會員撐腰,也難怪可以譜出高難度的計畫。

美國3D IC半導體部隊陣容完備

美國的半導體業,不僅有提供整體開發解決方案的IDM廠、專司設計的無晶圓半導體(Fabless)廠,亦擁有最先提供TSV解決方案的晶圓廠商ALLVIA等。擁有各類的半導體能量,在看準了TSV可超越摩爾定律,成為未來半導體殺手級應用,也吸引了產業鏈躍躍欲試。諸如學界的喬治亞理工學院與北卡羅來納大學,亦成立了3D IC研發中心,並積極地拉攏業界來開發3D IC的應用,整合後的聯盟陣容十分可觀。

|

|

| |

2006年9月成立的半導體3D設備與材料聯盟(EMC3D),目前會員共計十八家,在設備供應商部分,有應用材料、Datacon、Alcatel Micro Machining Systems、XSiL、Semitool、EV Group及Wafer Reclaim Services等業者;在材料部分則含Rohm and Haas、Enthone、AZ Electronic Materials、Honeywell與Brewer Science等。

此聯盟致力於開發具成本效率、可進行製造與堆疊的TSV接合技術,來支援強化3D IC市場的基礎設備。因此研發的陣容,集結了德國的Fraunhofer IZM、法國的CEA-Leti、韓國的SAIT與KAIST、荷蘭的恩智浦(NXP)及美國的TAMU等,積極累積研發專利。

成立至今3年多的時間內,EMC3D致力於發展、整合與探討3D IC相關的製程,如DRIE蝕刻與雷射鑽孔、絕緣層/隔離層/晶種沉澱、高深寬比銅電鍍、載具接合/卸載、循序晶圓薄化、背面絕緣層/隔離層/晶種沉澱、背面印刷、背面金屬電鍍。另外也包括晶片到晶圓的置放與接合技術,透過互相地支援設備、材料和流程技術,會員能從完整的製程中快速累積經驗,大幅地縮短了開發時間和初始投資成本。

另外為了協助業界發展以TSV為技術基礎的3D整合應用,EMC3D將主要的應用類別聚焦在3D IC堆疊整合、微機電系統(MEMS)及感應器的封裝上,致力於開發具成本效益且可量產的TSV互連技術,協助業界開發相關3D晶片之應用。

在製程成本方面,聯盟自1998年起,訂定了3年的年度目標包括利用聯盟會員的設備與製程技術,運用TSV製程以便產出8吋晶圓,並控制成本在每晶圓400~500美元。

其次,可依技術趨勢選用先鑽孔(Via First)與後鑽孔(Via Last)製程,產出同第一年規格的晶圓,但成本下降至300美元。最後,則是針對12吋晶圓提供無縫整合與可靠度改善的TSV製程,亦可選用先鑽孔或後鑽孔,並控制成本至200美元以下。

EMC3D設定3年可以將低成本TSV製程推向市場,目前處於中期階段,原先設定低於200美元/晶圓的製程成本,目前已發展成可以低於150美元的整體成本來製作先鑽孔和後鑽孔TSV製程的加工。正如EMC3D專案主任Paul Siblerud所言,EMC3D已透過改善的設備效率、簡化的流程,以及材料費用的降低,有效地降低成本。

日前EMC3D延長其計畫至2011年,設備商會員應用材料員工指出,應用較大直徑的後鑽孔TSV在動態隨機存取記憶體(DRAM)、中介層及圖像感應器晶片(CIS)裝置上、與直徑較小但深寬比較大的先鑽孔TSV結構,都存有顯著不同的挑戰。然而,如何在成本控制的情況下,有效改善此兩種製程,更是一個未知數,但卻值得期待。 |

|

|

| |

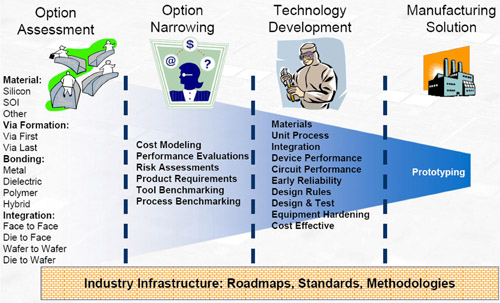

由美國官方及半導體業界合資的半導體製造技術產業聯盟(SEMATECH),現有十九個會員,包含台積電、聯電、英特爾、IBM、英飛凌、德州儀器(TI)、美光(Micron)及惠普(HP)等,占了全球晶片市場逾50%的市占率。

此聯盟公布的重點為評估現有技術,尋求改善方案、評估材料與製程的技術限制,找出具成本效益的解決方案、建立明確的成本評估模式避免高製造成本與風險。因此在3D IC市場中,SEMATECH將可協助業界會員確認材料的使用、技術的選擇、標準的建立、設計測試設備與製程的方法,以及開發突破關鍵製程,以提供技術對話平台。其發展的成本資源模式,亦可供業界確認其導入3D IC的可行性。

回顧在2008年底的IEEE/ACM國際會議中,SEMATECH展現了在3D IC發展的旺盛企圖心,其網羅了業界與學界專家,合成一股強大的研發能量,諸如由TechSearch來主導3D IC市場研究、由英特爾提供主要晶片的設計與測試解決對策、IBM主導3D IC整合應用、Gradient探討3D堆疊時的散熱處理、明尼蘇達大學研發高可靠度的3D IC電能供給、RPI發展記憶體應用3D堆疊時的電路設計、賓州大學探索3D IC成本模式、昇陽(Sun) 特別主導3D IC測試方法,以及高通(Qualcomm)針對應用TSV製程設備時的測試等,全面地來發展3D IC量產前短期預見的問題解決方案。

從SEMATECH官方所公布的3D IC進程規畫(圖6)可以看出,其透過累積經驗,以便規範出進程、標準與製造方法,而提供完整的製程解決方案。因此,為了有妥善的晶圓測試廠,SEMATECH在Albany設置並推出以研發為目標的測試建置計畫,預計在2010年第一季可以完成。

|

| 圖6 SEMATECH的3D IC進程規畫 |

|

|

|

| |

3D IC聯盟(3D IC Alliance)是由Tezzaron與Ziptronix共同發起,拉攏了晶片設計業和製程供應商,以便發展業界實現3D IC堆疊的共通標準,利用具體通訊協定(Protocols)和電子規格,讓規格互通並加速商品化量產的時間。其中例如記憶體互連標準(Intimate Memory Interface Specification, IMIS)便規範了立體記憶體晶片堆疊的官方標準規格,Tezzaron和Ziptronix已經使用IMIS標準來製造記憶體晶片,並於2008年末發布第一線的產品。

根據Tezzaron執行長Robert Patti的說法,在發展高速處理器核心的應用上,已導入3D互連技術,在現有和規畫中的DDR記憶體技術將逐漸無法滿足訊號頻寬的未來需求,採行IMIS標準,預期可以讓處理器製造商滿足數十億組記憶體訊號的頻寬問題,於是可讓DRAM的訊號密度直逼靜態隨機存取記憶體(SRAM),但卻能比傳統DRAM的成本更低。

此外,為了發展邏輯晶片元件的應用,Tezzaron網羅了十家廠商先作兩層的晶片,並透過旗下的多元件共用晶圓發展計畫來共用晶圓結構,並可選擇性搭配整合到Tezzaron的3D DRAM中。而在晶片設計的部分,則提供R3Logic作立體配置。因此,透過開放之標準,協助業界跨足3D IC應用、降低門檻,以促成3D IC作為技術的主流,即為3D-IC聯盟的主軸。 |

|

|

| |

成立將近兩年的立體全矽系統聯盟(3DASSM)聯盟,是由美國Georgia Institute of Technology、德國IZM-Fraunhofer和韓國KAIST三地的研究機構所共同成立的合作聯盟。

這是一個由學界發起的產學聯盟,源自於喬治亞理工學院的3D IC系統封裝研究中心(3D Systems Packaging Research Center),其3D IC發展的重點如圖7。

|

| 圖7 3DASSM的3D IC整合計畫 |

從其聯盟之名稱即可得知,此乃朝向全矽系統的方式來開發IC封裝與載板(Substrate),以取代傳統的陶瓷與有機載板,進而改善接線密度等物理性能之極限。其主軸將在於使用全矽系統設計、降低TSV成本、在矽載板上使用多層接線與具屏蔽的TSV、薄膜主動與被動元件的開發、開發將IC與矽基板互連的技術與可靠度評估以及各項技術整合等。

目前該聯盟正積極拉攏具有3D IC潛力的業界,其尋求的技術標的包括電介質材料與製程、微影(Lithography)工具、材料和製程、金屬化工具和化學製程、穿孔燒蝕和生成工具、矽和非矽核心材料與基底製造和晶圓級構裝技術等。 |

3D IC問世 半導體進入新階段

正如覆晶(Flip Chip)技術歷經10年才成為半導體封裝的主流,以TSV為核心技術的3D IC堆疊應用,其未來性如何仍未有定論。然而,儘管市場研究機構Yole預測,2015年使用TSV作3D IC堆疊的應用仍不到10%,可是從各國聯盟的動作頻頻,不只針對製程架構作調整,支援的設備、材料與工具,亦在積極規畫配合,從IC研發的投入資源,到產品的最終測試,TSV的晶片立體堆疊技術,將迫使半導體價值鏈,不論是要延續摩爾定律,亦或者是脫離摩爾定律,都將由3D IC的應用帶向下一個新半導體潮流。

(本文作者張嘉華為南台科技大學科技管理研究所助理教授、唐經洲為工研院資通所專案副組長)

| 參考資料 |

3D IC & TSV Interconnects, Yole Developpement, Nov/2008

.ASET, http://www.aset.or.jp/english/e-kenkyu/research_schedule.html

. IME-Singapore launches 3-D packaging consortium, http://www.ime.a-star.edu.sg/img/pdf/News%20Releases

/IME%20EPRC-10%20press%20release_20090630.pdf

.IME launch New Consortium to focus on 300mm 3D IC R&D in Singapore, http://www.ime.a-star.edu.sg/

html/highlights_200909_01.html

.3D IC at ITRI, http://www.semiconductor.net/blog/Perspectives_From_the_Leading_Edge/23392-3D_IC_at_ITRI.php

.3D Equipment and Materials Vendors Consortium, http://www.semiconductor.net/blog/

Perspectives_From_the_Leading_Edge/12529-3D_Equipment_and_Materials_Vendors_Consortium.php

.EMC3D Consortium Extends Goals and Program to July 2011, http://www.nanowerk.com/news/newsid=11673.php

.SEMATECH Announces Speaker Line-Up for 3D IC Design and Test Workshop, http://www.sematech.org/corporate/news/releases/20081022.htm

.Sematech積極推動3D晶片基礎設備之研發, http://www.eettaiwan.com/ART_8800407062_480102_NT_5df16e4a.HTM

.Sematech to set up 'test bed' for TSV production, http://www.eetimes.com/showArticle.jhtml;jsessionid=

OF2ZFEHSLHKSQQSNDLPSKHSCJUNN2JVN?articleID=218101581

.Tezzaron announces 3D IC Multi Project Wafer Program, http://www.semiconductor.net/blog/200000420/post/940040094.html |