由於目前AI晶片尚未標準化,仍有許多軟體有待分析處理,無形中墊高AI晶片設計門檻,此時亟需一種結合應用、演算法與晶片軟體架構三者並行的技術,從各個設計層面逐一擊破,方能打造更貼近自身所用的AI晶片。

人工智慧(AI)晶片需求熱度破表。無論是物聯網、語音助理、自駕車與智慧監控等應用,對於即時處理與高運算能力的要求與日俱增,進而對於加速上述功能的關鍵技術AI晶片寄予厚望,吸引傳統晶片業者或新創業者相繼投入其中,促成AI晶片發展呈現百花齊放的樣貌。

不過,AI晶片設計其實非常複雜。工研院資訊與通訊研究所嵌入式系統與晶片技術組組長盧俊銘(圖1)表示,雖然開發商著眼於將晶片設計出來,但經常碰到的問題卻都發生於系統問題。這也意味著,AI晶片是解決AI系統運作中的關鍵元件,開發商要設計AI晶片就不得不考慮其應用於何種應用、對應甚麼演算法。換句話說,AI晶片設計必須同時考量「系統應用」、「深度學習演算法」與「晶片硬體架構」,三者進行協同設計優化,也就是所謂的AAA(Application, Algorithm, Architecture) Co-Design概念。

圖1 工研院資訊與通訊研究所嵌入式系統與晶片技術組組長盧俊銘表示,AI晶片設計尚未標準化,AAA Co-Design設計概念是必須的存在。

圖1 工研院資訊與通訊研究所嵌入式系統與晶片技術組組長盧俊銘表示,AI晶片設計尚未標準化,AAA Co-Design設計概念是必須的存在。

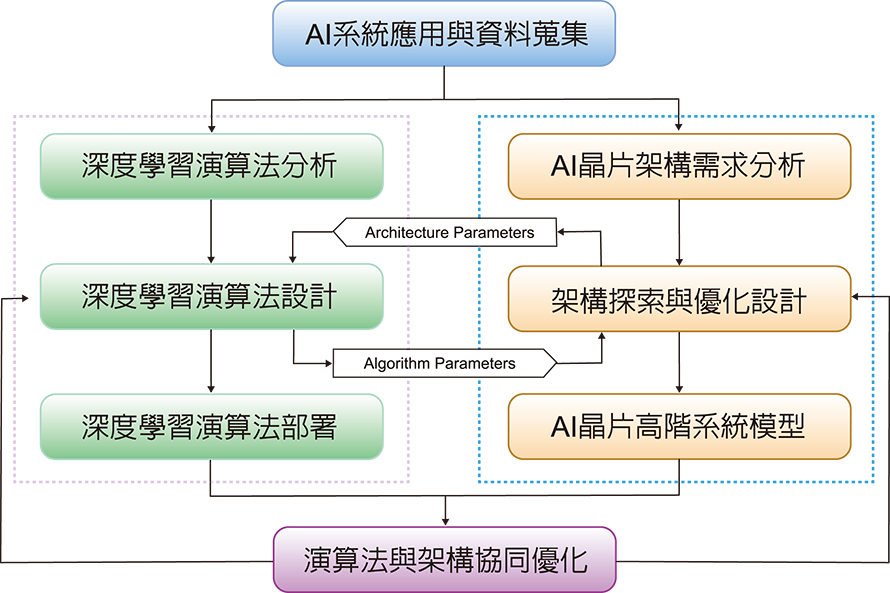

整體而言,AI晶片規格制定需從系統應用進行分析並蒐集資料,同時還必須有更快速、更全面、更自動的深度學習演算法模型訓練與優化設計方案;在AI晶片架構設計上,須更快速分析深度神經網路(Deep Neural Network, DNN)算法每一層的運算複雜度與係數資料儲存量,進而整體設計運算元、匯流排及資料流;最後一步實現AI晶片的階段,則是需要整合系統應用、軟體編譯、晶片架構分析到硬體模擬的平台設計,實現軟硬體協同優化的能力。

事實上,AAA Co-Design的概念並不是新的發明,只不過從以往到現在的IC設計落實得並不全面,還是憑各廠商的投入策略而定。但是進入AI晶片設計時代,盧俊銘強調,AI晶片設計必需要用上AAA Co-Design概念不可,因為AI晶片硬體沒有標準規格,會隨著應用與執行的演算法而有所差異,基於此晶片制定規格或分析晶片系統應用能力也就特別重要,若未掌握這些能力,很可能做出來的晶片不是最佳組態。

盧俊銘談到,過去兩三年間,工研院就開始投入AI晶片設計輔助工具,其為近似於EDA工具的方案,也就是AI晶片設計軟體平台,建立從AI系統應用分析到晶片架構設計實現的整體能力。舉例來說,AI晶片架構分析技術,是基於解析模型(Analytical Model)的創新晶片架構分析技術,模擬分析速度超越現有技術100倍以上,同時支援各種資料流(Data Flow)架構;全系統模擬與軟體工具鏈,則是支援端到端AI全系統快速模擬,軟體開發大幅提前已不是問題,不僅如此還提供完整AI晶片工具鏈參考設計,包括程式碼生成與運行時期函式庫(圖2)。

圖2 AAA Co-Design設計流程圖

圖2 AAA Co-Design設計流程圖

資料來源:工研院

盧俊銘指出,目前已經有許多廠商導入AI晶片設計軟體方案,包含IC設計廠商與半導體廠商。該單位與這些廠商接觸的結論是,目前台灣IC產業界的確很欠缺AAA Co Design平台與對應的架構設計團隊。整體來說,若遵循一個標準大概就要專注於將規格作到最好,不過AI晶片尚未有標準可以依循,因此分析規格、制定晶片的能力也就相當重要,故半導體業者直接與工研院合作軟體與分析部分。

捕捉AI晶片新商機 台廠兵分二路

在自駕車與監控攝影機應用的推動下,台灣IC設計廠商近兩年投入AI加速器的意識愈趨高漲。盧俊銘認為,台廠投入AI晶片布局可能會分成兩個方向進行,一種是向IP供應商授權具備AI功能的IP,意味著有些架構區塊(Building Blocks)自己不開發,用第三方的技術來導入;另一種則是自有設計AI加速器,獨立做出自有的自主架構。

以現階段而言,開發商對於AI晶片的需求非常明確,IC設計廠商為了要搶時效,最快方式有可能是先取得別人IP做出產品,滿足開發商需求為目標,而後若該產品線需求越來越多,甚至是其他類型的產品同樣有AI應用需求,最終才會考慮是否生產屬於自己的AI加速器。

鎖定AI晶片 MCU大廠磨刀霍霍

以IC設計產品類型來看,MCU廠商幾乎都想在下一代晶片加入AI功能。盧俊銘談到,MCU可謂是一種中央處理器或微算器的角色,主要執行一些軟體指令,這些軟體指令雖然不一定能完美體現AI的威力,但至少能帶出AI的功能,故MCU可先用軟體方式導入部分AI能力,進而量產提供給開發商。這類型的開發形式對MCU廠商而言,硬體成本幾乎沒甚麼變化,只是增加一些軟體成本。而後下一代產品可能是從數位訊號處理的引擎著手加入一些AI功能。直到某個時間點再開始生產專屬AI加速器提升運算性能,如同上述而言,這種方式導入時間比較長,或許是使用IC設計商已開發好的方案,亦或是透過授權方式導入。

整體看來,在選擇AI晶片加速的硬體功能時,則是會採用CPU、數位訊號處理器(DSP)、特定應用積體電路(ASIC)等類型方案,而受產品面世時程壓力影響,可分為向外部取得授權或自主開發這兩種方式。

依據上述趨勢發展看來,目前使用IP授權加速AI晶片設計可謂是一項關鍵模式。從外部取得IP方式可分為採用RISC-V的開源方案,或是採用產品系列及生態鏈完整的Arm Base IP技術。前者需投入較多的RD資源,後者則是需要增加授權成本,而這些都是影響晶片業者的選用考量要素。

RISC-V異軍突起 Arm改變授權方案應戰

晶心科技總經理林志明表示,RISC-V可被快速採用並創造高需求,尤其是MCU級別的應用。工程師需要小型、低功耗又高效能的商業等級RISC-V核心來打造多元的SoC。不像一般開源RISC-V CPU不僅功能有限、缺乏說明文件,還須先經SoC工程師驗證;而採用商業等級的晶心科技N22 CPU便能跳過這些耗時又無法增加最終SoC價值的步驟,並將寶貴研發資源集中於提升產品價值。

面對RISC-V急起直追的發展,Arm一改過去授權方式,推出Arm Flexible Access全新的合約模式,讓SoC設計團隊在取得IP授權前就能展開計畫,屆時只要針對生產時使用到的部份進行付費。透過Arm Flexible Access,企業將能賦予他們的設計團隊擁有更多的實驗、評估與創新的自由度。

Arm IP產品事業群總裁Rene Haas表示,Arm Flexible Access的誕生,主要是因應一兆台安全聯網裝置的世界所帶來的機會。藉由無限的設計存取與免預付授權費(Up-front Licensing)方式的結合,讓既有的合作夥伴與新進入這個市場的參與者,得以應對物聯網、機器學習、自駕車與5G帶來的全新成長機會。

通常合作夥伴從Arm獲得個別元件的授權,並在存取此一技術之前預付授權費。藉由Arm Flexible Access,只要支付少許的費用,就可以立即存取廣泛產品系列的技術,隨後只需在確認製造生產時,再支付一筆授權費,以及之後隨每個單元的出貨支付權利金(Royalties)。產品系列包括所有SoC設計所需的必要IP與工具,讓合作夥伴在承諾授權前,便於針對多IP模組進行評估與原型設計。

可以透過Arm Flexible Access計畫存取的IP,包括Arm Cortex-A、Cortex-R與Cortex-M產品系列等大多數Arm架構處理器,這些CPU占過去兩年內所有Cortex CPU簽約授權數的75%。它同時包括Arm TrustZone與CryptoCell安全IP、部份Mali GPU、系統IP,以及SoC設計與早期軟體開發的工具與模型。此計畫同時包括Arm全球支援與訓練服務的存取。

實際比較Arm與RISC-V的差異,盧俊銘分析,除了在成本上略有不同之外,Arm的產品線非常完整,目前RISC-V可以與之抗衡的領域,大多還是聚焦於中/低等級的處理器,至於高階技術或許未來也會有機會比拼,但就現階段而言,Arm還是占有一定的優勢。

另一方面,RISC-V可作為MCU或處理器的IP,成為實現AI運算系統的關鍵元素,未來很有可能是RISC-V與深度學習加速器(Deep Learning Accelerator, DLA)整合在一起成為一顆晶片,意味著未來的AI會有類似像RISC-V這樣的控制器,以及一個叫做Building Block的AI加速DLA IP。

盧俊銘指出,傳統MCU僅能執行控制功能,但現在越來越多應用牽涉到AI,即需執行一些資料前處理的動作,而這就需要根據演算法做硬體加速。這意味著用於各個產品的MCU,都會因為資料需要進行前處理的關係,而支援AI演算法所需的硬體支援能力,否則單單仰賴軟體的方式會非常沒有效率。

基於此,台灣MCU廠商陸續投入AI晶片研發技術。除了MCU廠商以外,台灣尚有許多顯示晶片、指紋辨識晶片或語音晶片等廠商,亦陸續投入AI晶片的研發,其能在AI應用風潮中,找到了一個乘浪而起的機會。