雖然全球半導體產業皆看好3D IC的未來發展,進而展開布局,然而廠商須考量設備、材料與製程技術是否完全齊備,才能真正開發3D IC產品,享受TSV技術帶來的種種好處,以進一步突破摩爾定律的瓶頸。

三維晶片(3D IC)的魅力風靡全球,身為半導體業領先族群的台灣,也逐漸看見3D IC市場能量。諸如日月光,早已在3D封裝的研發下,有不少的著墨,台積電也於2009年投入3D IC的行列,而聯華電子則宣布與日本爾必達(Elpida)合作,預計於2011年推出堆疊邏輯晶片與記憶體的商品。從大廠將3D IC安排到自家的未來發展計畫上,想必是春江水暖鴨先知,嗅到市場未來的重大趨勢。

3D IC的概念早已存在,若非摩爾定律(Moore's Law)即將走入死巷,才逼出超越摩爾(More than Moore)的概念,以及加速3D IC立體堆疊的實現,並指出矽穿孔(TSV)走向主流技術,需設備、材料與製程齊頭並進,才可加速量產,雖然目前主要的3D IC已在互補式金屬氧化物半導體影像感測器(CIS),以及同質記憶體堆疊實現,但更多樣的商品應用,端看設備材料與製程供應是否可提供更整合的解決方案,因此本文將從設備、材料未來需求的預測資料,以及製程供應商現況,分析是否已足夠解套。

通盤考量3D IC關鍵設備/材料

3D TSV被認為是立體堆疊的關鍵技術,許多專家在定義3D IC時,也認為只有使用TSV,才是正宗的3D IC,因此,能支援應用TSV於立體堆疊上,協助提供解決方案的供應商,便成3D IC的促進者(Enabler),以目前3D IC在全球僅十五條300毫米(mm)晶圓試產線的規模來看,未來勢必有更大的需求出現。

而在需求相關設備材料作立體堆疊時,業界通常會有包括可支援3D立體多層晶片設計的電子設計自動化(EDA)工具、散熱問題的解決與相關材料的發展、矽中介層的使用問題、具有足夠良率的量產設備、可供量測的方法與相關工具,以及可提供控制合理的整體製程成本等考量因素,若能依此考量發展,將會更具有說服力。

部分應用於平面晶片的設備工具,是可延用於3D堆疊的應用上,畢竟TSV在半導體整體製程中,只是為讓晶片利用單位面積的概念,轉而變為充分利用立體空間所帶來的優勢,若未能調整或增加既有的設備與材料,仍無法落實此技術。目前市場應用於立體堆疊的設備,可分成標準設備如Litho顯影工具、化學機械研磨(CMP)工具等,以及特殊的TSV製程設備,一般較易取得標準的設備,但後者則需要進一步的調整,才得以應用,也就成為進入量產的關鍵設備,此類的設備包含晶圓對晶圓(W2W)與晶片到晶圓(C2W)的接合設備、深度離子反應蝕刻、電射鑽孔、填孔設備、光罩對準器、電鍍設備與噴灑塗層(Spray Coating)工具等,目前12吋晶圓應用3D TSV的相關設備,早於2008年進入測試階段,其相關的工具設備之取得也只是時間上的問題,至於材料的選擇上則包括較低熱膨脹係數的材料、中介層與基底的矽材、填孔材料、接合/膠合材料與低介電係數的材料等特殊需求。

從上述材料的特殊需求來看,可知都是為在應用TSV接合堆疊晶圓/晶片時,輔助解決製程上將會產生的相關議題,電子元件過熱容易產生不正常運作甚而損壞,因此散熱材質的應用也將會是一大焦點。若以材料市場的展望來看如杜邦(Dupont)與日本NKC的合作,將致力於共同發展晶圓級封裝(WLP)、3D IC與TSV製程的支援材料,以兩家公司對3D IC材料市場的個別估計,將從2013年大約6億美元的規模,成長至2015年近幾一倍的產值,達12億美元。材料的需求被動於製程與設備,然而這個金三角也必須緊密維持協同並行。

3D IC材料需求將追上設備

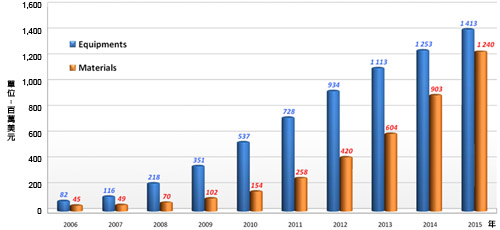

從圖1中,可看到2006~2015年共10年的時間,Yole Developpement分別預測3D IC TSV設備與材料市場總值,無論是設備或材料,都將逐年成長,並且於2015年時,兩部分的市值即將相同。這肇因於2013年時,材料的成長將急起直追設備的市場產值。以設備的需求來說,早在2008年開始,設備商便已開始布局,無論TSV的加工設定在製程中那個位置,為顧及可製造性、可靠度、良率與彈性,額外的設備需求勢在必行,起碼如產生通孔高深寬比結構所需的蝕刻設備(Etcher)、堆疊時基準線的對準器等,都並非標準的半導體製程設備,也因此在3D IC的市場上,設備產量成長較早;至於在材料部分,如前節所列,在3D IC的市場上,亦有特殊規格材料的需求,如可主動散熱的材質,便會在堆疊晶片時使用到;又如低熱膨脹係數的基底材料也較不易破壞堆疊的結構,容易接合(Bonding)與剝離(Debonding)的材質,也是在暫時接合載具(Carrier)時一個重要的材料,沒有適當的材料配合,TSV製程的可行性將會大打折扣,這也是為何材料需求會急起直追的原因。

|

| 圖1 3D TSV技術設備與材料市值預測 |

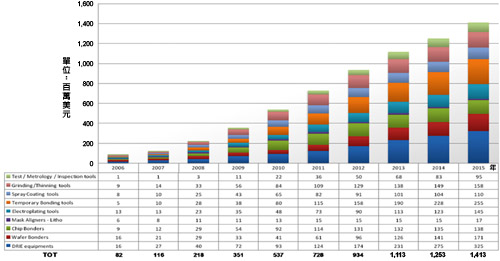

圖2、3說明設備與材料的產值中,究竟涵蓋那些項目,以設備的成長來看,以DRIE蝕刻工具、暫時接合工具(Temporary Bonding Tool)、晶圓接合(Wafer Bonder)、研磨與薄化(Grinding /Thinning)、電鍍工具(Electroplating)及晶片接合(Chip Bonder)等,有較顯著的成長,而以單項成長率看,則以DRIE工具最快,利用DRIE產出通孔的結構,本應為TSV的關鍵設備,因為深寬比的大小將直接影響堆疊的能力,如在微積電系統(MEMS)元件晶圓尺寸變大時,DRIE設備須設計在兼顧高蝕刻速率與降低製造成本下,維持高蝕刻均勻性,以及可應用於深寬比較大的結構上,亦即無論在任何尺寸下的晶圓,DRIE在晶圓的蝕刻率/深度均勻度須穩定,以便保證在晶圓上任意位置所形成的TSV結構都要一致。

|

| 圖2 3D TSV技術各類設備預測圖 |

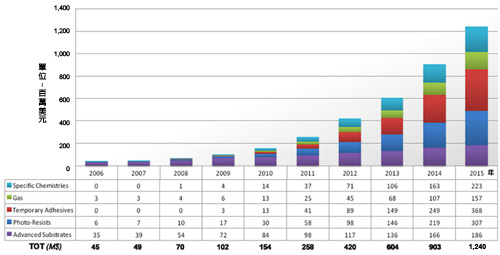

|

| 圖3 3D TSV技術各類材料預測圖 |

在材料方面,如圖3所示,則很明顯的在暫時膠合(Temporary Adhesives)與顯影光阻劑(Photo-resists)成長最為明顯,由於晶片間接合方法,膠合的方式大約占46%以上,也因此,可解釋為何此類的需求如此顯著,如Ziptronix的Direct Bond Interconnect(DBI)技術,使用氧化物接合技術,於常溫下進行W2W或D2W時,有效產生金屬間的互連,DBI技術可將鎳金屬接合到如銅、鎢或鋁等的金屬材質的TSV孔上,透過DBI,可讓氧化物和金屬間形成完整的平面,以便產生可靠度高且強度夠的接合,亦是另一種接合材質需求。另外,較佳的顯影光阻劑可在堆疊時,進行良率更高的CMOS前段製程,並改善TSV進行加工製作時的定位能力,因此,由於TSV的應用預測將逐年增加,此類必要的材料也將相對增加供應量。

針對目前設備與材料市場所作的觀察,廠商決定進入3D IC市場時,除成本、EDA及量產設備可稱具有些微規模外,其他的平行必備條件,卻是較缺少著墨之處,也將會是未來TSV市場必須進一步努力與發展的方向。以應用材料的部分來說,目前以散熱性佳的材料、是否須使用載體,以及應用的材質部分,仍未有定論;而設備工具部分,接合工具已到位,其中仍須改善的則以3D設計工具、EDA和檢測工具的開發,有待進一步強化。另外,由於在TSV製程方面,以晶圓薄化最為成熟,而成本、可堆疊層數和薄化後晶圓卸載部分仍須加強,且在堆疊可靠度的監控上仍是最弱的部分,適當的工具與材料也須適時發展。

製程選擇左右設備/材料需求

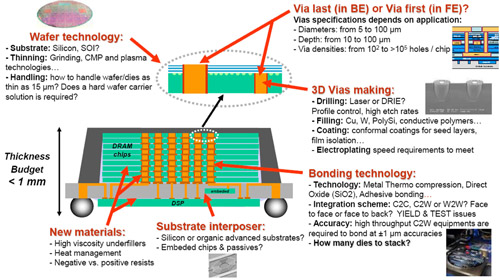

設備與材料的需求,通常會反映製程執行時所遭遇的困難,在圖4指出在進行TSV技術於堆疊晶片時,須配合協調的技術內容,主要的關鍵要素包含TSV通孔的作業時間、鑽孔的方式、晶片或晶圓間接合的技術、中介層的應用與相關材料的選擇等,不同的選擇須有對應的配套,首先參考圖4分析主要的製程考量點為何。

|

| 圖4 3D TSV相關促成技術 |

| ‧ |

|

| |

TSV加工的執行時機,目前仍未有一定的標準作規範,而無論是選在前段製程(FEOL),又或是應在後段製程(BEOL),將會影響配合執行加工製造供應商的選擇,並影響製程的內容與加工的困難度,更甚而影響到成本。 |

| ‧ |

|

| |

鑽孔的方法可選擇雷射或DRIE蝕刻,根據選擇的方法,不僅會影響所需的設備機台、填孔材料的選擇、電鍍與塗層的材料,更會影響精密度與執行加工的產出率。 |

| ‧ |

|

| |

接合的方式可選擇金屬壓縮接合、氧化物直接接合與膠合等技術,選擇接合技術之後,還必須考量選擇晶片到晶片(C2C)、C2W、W2W的接合,再加上選擇面對面,或背對背的處理方法,都會影響到良率、可靠度與可堆疊的層數等。 |

| ‧ |

|

| |

晶圓的材質是全矽或矽絕緣體(SOI),薄化方法是磨削(Grinding)、CMP或電漿(Plasma),都會影響最終的厚度,以及是否使用載具,另外,中介層也可考量使用矽材質或有機基板;而材料部分,則期望可妥善散熱、具黏性,並可任意選擇 產生正或負光阻(Negative vs. Positive Resists)等。 |

鑽孔在先或在後影響半導體產業鏈

上述幾類TSV執行製程時的決策,都是廠商導入TSV於半導體製程應考量的方向,其中以TSV執行的時機最具有關鍵影響性,選擇不同的鑽孔在先(Via First)或鑽孔在後(Via Last)製程,其最大的影響將讓價值鏈架構有重大的結構變化,無論是晶圓代工廠(Foundry)或封裝廠(Packaging House)都對此非常有興趣,以下來看看市場上有那些供應商選擇於前段執行TSV,又有那些選擇後段執行,並說明已達到的TSV規格。

何謂鑽孔在先與鑽孔在後,根據艾克爾(Amkor)的操作定義,若採用鑽孔先於TSV,則鑽孔與填孔都將在整塊的矽土上執行,並以晶圓級的方式接合,再將背面的金屬薄化;反之,若使用鑽孔後於TSV,則晶圓會被先薄化,在背面金屬化之後,再於背面進行鑽孔和填洞。

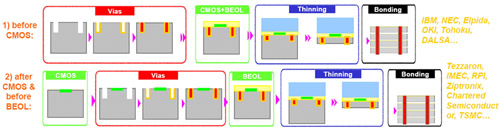

如圖5所示,進行鑽孔在先的TSV製程,可分成在CMOS之前或在CMOS與後段製程間執行,採行CMOS在前方法的廠商,有IBM、NEC電子、爾必達、日本沖電氣(Oki Electric)、Tohoku與Dalsa等,而採用後者的,則有Tezzaron、比利時微電子研發中心(IMEC)、RPI、Ziptronix、Chartered及台積電,台積電亦於2009年6月正式宣布投入產能於TSV的代工,可見在晶圓代工業者,以採用鑽孔在前,且於CMOS與後段製程之間,進行加工為較可行的方式。

|

| 圖5 鑽孔在先的TSV製程 |

而在鑽孔後於TSV的製程中,亦可區分成在後段製程之後,進行TSV前先作接合或作完接合再進行TSV兩種,如圖6所示,前者的代表廠商為英飛凌(Infineon)、IZM、ZyCube與ASET,後者則為RPI、RTI、IBM、MIT與三星(Samsung)等廠,由於鑽孔在後較不會影響到前段製程,可能在封裝廠或封測代工廠(OSAT)等,會有較有力的利基點,在單一封裝中進行系統封裝(System in Package, SiP),初期可能只能在同質性較高的晶片應用上發展。

|

| 圖6 鑽孔在後的TSV製程 |

選擇不同的TSV策略,在材料設備上將會有不同的對應選擇。以鑽孔在先在前段製程前的整合方式而言,其主要的設備需求為可提供在複晶矽(Poly-Si)上,進行高深寬比的填孔製程,而需求的材質則是可具有高電阻且無加工溫度限制的複晶矽;若以在後段製程中導入TSV的選擇來說,設備需求為可在各晶片層頂端進行 鑽孔的工具,製程的特點則須可對鎢或 銅進行化學氣相沈積(CVD),且銅TSV須作除污製程,並且操作溫度不得超過400℃。另外若是在後段製程後再作TSV,但須在前段製程中先進行鑽孔者,其需求條件與後段製程中進行TSV者相同;若是要在後端進行鑽孔,其設備須能支援小孔徑的製程,並且要能避免金屬襯墊毀損,材料則需要銅、漿泥(Paste)等,操作溫度則不能高於200℃。

若是進一步比較鑽孔在先與鑽孔在後主要的差異點,由於前者不會受到CMOS阻斷層(Barrier)溫度的限制,且因填孔材質須與CMOS製程相容,所以鎢與銅都不能作為填孔材料,也因此只能選擇多晶矽(PolySilicon)來填孔,另外,只有已進行過TSV的良好晶圓,才會進行前段製程,所以不會影響最終的產出良率;若是鑽孔在後的TSV,則需在前段製程前便保留區域,方便之後進行TSV製程,這樣的作法不會導致熱壓(Thermal Stress)問題的出現,由於是在後段製程之後才作TSV,因此,將會降低最終的產出良率,而針對較微小的洞,則可配合使用電鍍金屬補強。

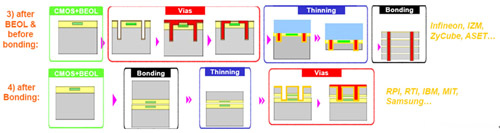

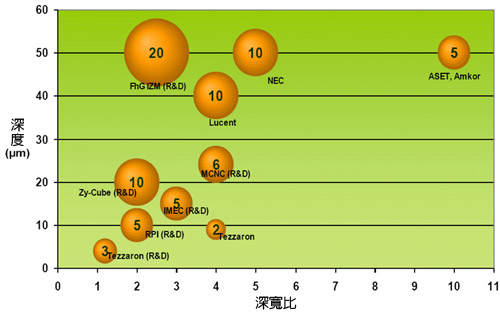

TSV孔徑大小支配成本/可靠度

微小孔徑的TSV(μVias)的市場分成兩個部分,一個是孔直徑在1~15微米(μm)間,但深度在30~50μm間,為密度較高的市場;另一個則是孔直徑小於50μm,但深度在75~200μm間,孔的形狀被尖銳化(Tapered)而密度較低的市場,這是因為被尖銳化的孔,讓沉澱技術有困難的廠商,可比較容易進行鑽孔的填充,目前,這種被尖銳化後的TSV規格,大多應用在CIS影像感應器上,孔的深寬比確實會影響製程的可製造性、成本與可靠度,並會影響互連堆疊的能力,以圖7與8來看,在鑽孔在先進的TSV製程上,其鑽孔的深度大概都在60μm以內,而孔的寬度則多在6μm以內,因此,其深寬比都落在約10,僅有德國的IZM,可達20的深寬比;反觀在鑽孔在後的TSV製程上,其鑽孔的深度大概都可達到200μm以上,而鑽孔的寬度卻平均多在60μm以內,因此,其深寬比則下降到10以下,深度較深的TSV孔,如東芝(Toshiba)、Leti、三菱(Mitsubishi)、Silex與Thales等,孔的寬度都接近100μm,使得深寬比無法增加。

|

| 圖7 鑽孔在先深寬比與供應廠商圖 |

|

| 圖8 鑽孔在後深寬比與供應廠商圖 |

統計所有進行3D TSV廠商的技術規格,能達孔直徑小於1μm的,在市場上僅占8%,如Tezzaron,然而大部分的TSV孔尺寸,都大於10μm,並且有將近三成的比例,鑽孔直徑仍大於50μm。在之前有提過,鑽孔的深寬比將會影響應用TSV堆疊圓的數目,目前最多的堆疊數目,大約仍介於四到八之間,大量或多異質晶片的立體堆疊,則僅有不到8%的比例應用。

一般在決定採用鑽孔在先或鑽孔在後TSV製程時,可能須考量兩個主要因素,包括廠商自己的商業模式(Business Model),與鎖定的最終市場應用如MEMS、CIS、記憶體、射頻(RF)SiP與邏輯(Logic)採用新技術時,廠商本須考量是否得投入過大的資本,迎合市場的需求,如原先提供打線接合製程作晶片互連的晶圓代工廠,可能會考量的是,若導入TSV後,會有些額外的投入,機台、材料、設計的EDA或是支援的設備等,都須算入到整體擁有成本(TCO)中,除了在CMOS之前的鑽孔在先TSV製程,不會有堆疊接合後再薄化的需求外,其他的製程選擇都面臨應在接合後或前作晶圓薄化,另外,薄化時機的選擇,也會影響是否須用載具,若選擇在接合前便須薄化,則暫時性地使用載具處理薄化後晶圓,便成必要條件;再則,不同的選擇在接合方法上也有影響。以下整理部分在市場上,不同策略選擇時應配合的可能作法。

例如選擇在CMOS前進行鑽孔在前製程,如IBM、Dalsa、NEC電子、Tohoku、OKI與爾必達等,鑽孔後乃以Poly-Si材質填孔,利用載具暫時接合,而薄化後,將使用金屬融合的方式作晶圓接合。

選擇介於CMOS與後段製程間,但於薄化後再行接合,如IMEC、美光(Micron)與RPI,亦需求載具,且使用金屬融合的方式接合。另外,選擇介於CMOS與後段製程間的廠商還有台積電、Chartered、Ziptronix與Tracit(Soitec)等,其選擇於接合後再行薄化,接合方式則採行氧化物直接接合(Direct Oxide)。而選擇採氧化物直接接合方式,包括MIT、IBM、Tracit(Soitec)與Ziptronix等,但其選擇在接合後再進行TSV加工,因此無需載具。

此外,IZM與英飛凌則選擇在後段製程與打線間進行TSV,由於在接合前亦須薄化,因此便須利用載具,接合方式則選擇金屬融合。

RTI與ZyCube則採用膠合的方式,其執行TSV的位置在晶圓接合後再進行鑽孔,由於先接合再薄化,亦須利用載具。

關鍵切入點多 3D IC需求看俏

基於以上的資料觀察,3D TSV進行整合製程時,若要能作到量產,下列的決策都須完整規範,設備、材料與製程商扮演著供應軍火的角色,TSV能否進入主流應用,端看其供應是否可以完備。

| ‧ |

|

| |

複晶矽、銅、鎢、導電聚合物(Conductive Polymer)等。 |

| ‧ |

|

| |

電鍍(Electroplating)、CVD、聚合物塗裝法(Polymer Coating)。 |

| ‧ |

|

| |

鑽孔在先、早鑽孔(Via-early)與鑽孔在後。 |

| ‧ |

|

| |

正面(Front-side)與背面( Back-side)。 |

| ‧ |

|

| |

直接銅-銅(Direct Cu-Cu)、黏著劑(Adhesive)、Direct Fusion、金屬間化合物(Intermetallic)及混合式接合。 |

除上述條件外,製程成本是否可以合理降低、3D EDA是否可支援製程設計、熱處理材料的問題、具有足以量產的工具設備以滿足經濟效益及測試工具的提供,皆為TSV能否普及的因素。最後在應用材料的供應部分,目前散熱性佳的材料、是否須使用載體,以及應用的材質部分,仍未有定論;而設備工具部分,接合工具已到位,不過3D設計工具、EDA和檢測工具的開發有待進一步強化;在TSV製程方面,以晶圓薄化最為成熟,而成本、可堆疊層數和薄化後晶圓卸載部分須加強,並且在堆疊可靠度的監控上依然是最弱的部分。

另外,針對市場的應用狀況所作的評估,TSV應用的彈性上有非常大的期待,然而標準化的界定與應用的成本,尚須提升,且現階段市場應用的比例仍不足,若是以3D IC的價值鏈類別來看,整合元件製造商(IDM)、無晶圓(Fabless)/輕晶圓廠(Fab-lite)、OSAT廠、晶圓代工廠及封裝廠,都相繼規畫能量與策定未來的定位。由於IDM可整合應用TSV的所有製程,預料將是3D IC產品最先進入者,而到目前為止,只有少數代工廠與封裝廠已策畫在自家的發展藍圖中,但正如OSAT廠一般,未來可能主宰TSV應用的主要市場,能夠提前布局,才能搶得先機。

(本文作者依序為南台科技大學科技管理研究所助理教授、工研院資通所專案副組長)