電子產品傳輸架構已從過往的平行匯流排(Parallel Bus)轉換成序列傳輸(Serial Communication)的連結介面。使用序列傳輸介面的優點包含更少的元件接腳、減少印刷電路板(PCB)布局(Layout)所需空間、更小型的連接器和更高速的傳輸速率。

然而,高速序列傳輸的設計也遇到過往數位系統設計者所沒遇過的挑戰,這些問題以往只會出現在微波或高頻電路。如今電子產品所使用的高速傳輸介面速度已達到Gbit/s,並且在短期的未來新標準的規畫也都不斷提升傳輸速率,例如PCIExpress(Gen1)操作在2.5Gbit/s,而PCIExpress(Gen2)和PCIExpress(Gen3)則操作在5.0Gbit/s和8.0Gbit/s。

同時,高速序列IC設計最複雜的挑戰在於特殊的資料處理,例如串列器-解串列器(Serializer-Deserializer, SERDES)、等化器(Equalization),和數位編碼(8B10B或64B66B)。而系統工程師在設計高速序列印刷電路板時也同樣會面對訊號的衰減、電源完整性與電磁干擾等等相關的技術困難。因此,一個好的序列傳輸設計必須有好的模擬流程來確定設計的品質,並且避免花費高昂的重複設計費用。

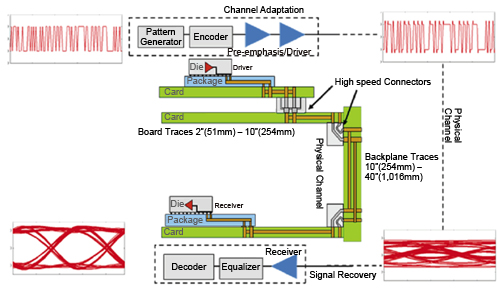

圖1是典型的序列訊號傳輸過程,包含傳送與接收IC,封裝印刷電路板走線與連接器,而IC以外的被動元件連結起來的部分,本文統稱為通道(Channel),本文會解說高速序列的通道在訊號完整性與電源完整性的模擬,並且會以實際的例子來做說明。

|

| 圖1 典型高速數位序列傳輸流程 |

訊號完整性模擬

要模擬出準確的訊號完整性分析,重建通道中每一個被動元件的模型(通常以S參數為主)並選用一個準確且有效率的模擬器是相當重要的。以安捷倫(Agilent)的Advanced Design System(ADS)為例,在ADS 2009與之後的版本,提供一種全新且容易使用的模擬引擎Channel Simulator。Channel Simulator與傳統暫態(Transient)Spice相關的模擬器比較,Channel Simulator的模擬速度大幅提升,直覺且容易地和S參數模型結合,同時結合儀器的演算法,還可以快速後處理大量的數據。

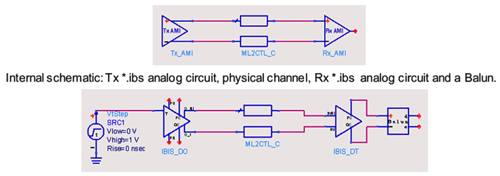

速度的提升,並沒有降低準確度,因為訊號通道都是被動且線性的,所以可以假設成一個LTI(Linear, Time-Invariant)系統,並且使用脈衝響應(Impulse Response)萃取出通道的數學模型。在萃取模型的過程,軟體的暫態引擎自動會以1V的階梯(Step)訊號輸入於Tx,訊號會激發Tx端的IBIS模型傳送出一個上升波進入到通道,階梯波的響應會在Balun差分的輸出端被截取,當整個響應訊號穩定後,暫態分析就會自動停止(圖2)。透過此數學模型做後續的計算,模擬速度就可以大幅度提升,而不像傳統的暫態分析每一個位元(Bit)都須要做一次暫態的計算。

|

| 圖2 Channel Simulator計算示意圖 |

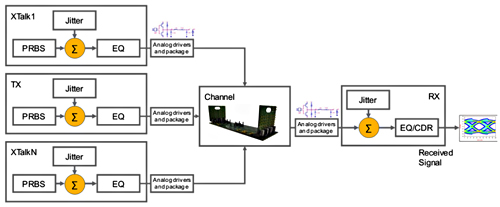

圖3是典型Channel Simulator可以快速分析的系統,有一個Tx的主訊號和任意數目的Cross-talk訊號源、任意數目的通道模型以及一個接收端Rx模型。所以軟體使用者可以很方便地匯入不同模型,這對於訊號完整性模擬的工程師來說相當重要,因為他們會從公司內部或廠商端拿到許多不同形式的模型。

|

| 圖3 適用於Channel Simulator模擬的系統架構 |

以連接器為例,廠商可能會提供S參數模型、Spice等效電路模型,甚至提供三維(3D)圖檔用3D電磁模擬來萃取連接器參數。串接這些模型,就可以用來表示整個通道的特性,在ADS中支援S參數、無線連結控制(RLC)元件、W-elements、ADS內建傳輸線模型、內建多層板模型、Hspice/Spectre電路。而這些模型內部的資料有些是頻域的資料,如S參數或某些傳輸線模型,而ADS會自動運用Convolution演算引擎去轉換成符合被動律(Passive)和因果律(Casual)的時域資料,這樣就可以讓使用者任意混合頻域和時域的模型。

圖4是一個ADS軟體內建的PCIe Gen2通道模擬例子,由圖中可知整個通道包含封裝、Via、附加介面卡(Add-in Card)、連接器、印刷電路板傳輸線模型和接收端的眼圖探針(Eye Probe)。Via和連接器都是Touchstone的S參數,4吋的附加介面卡走線和12吋的系統板(System Board)走線都是使用ADS內建的多層板模型。內建模型有許多可設定的參數可用於調整和優化這些參數,用在Layout之前的what-if模擬可以快速決定走線和Via的相關參數值。以這個系統板的走線為例,就可設定走線的長度、寬度和間距為變數。

|

| 圖4 Differential via在16層印刷電路板 |

一些輸出端可設定參數(圖5),一個5Gbit/s的隨機(PRBS)序列訊號會透過這個Tx模型產生,電壓準位和上升下降時間也標示於圖中。8B10B的編碼方式也有啟動。在第一個模擬的簡單例子中,並沒有把輸出端的預強化(De-emphasis),抖動干擾和其他線路的干擾源(Crosstalk)效應考慮進來。

|

| 圖5 Tx模型的參數圖形 |

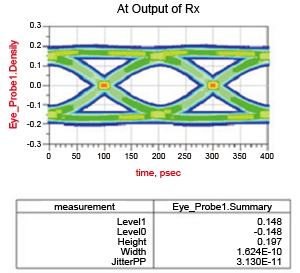

而眼圖與相關的輸出結果,可以透過差分眼圖探針(Differential Eye Probe)點在要觀察的位置(圖6)。這裡選擇觀察眼圖的Level1/0、寬度、高度和密度。同時為了方便觀察結果,圖形化的顯示可讓使用者很快得知結果。ADS Channel Simulator可以快速做上萬筆位元的後處理,就是因為引進儀器演算法的Eye Probe讓電腦只計算和儲存必要的資料,並且讓使用者透過圖形介面快速得到所預知的各種結果。

|

| 圖6 差分眼圖探針可選內容與上列PCIe例子模擬出的結果 |

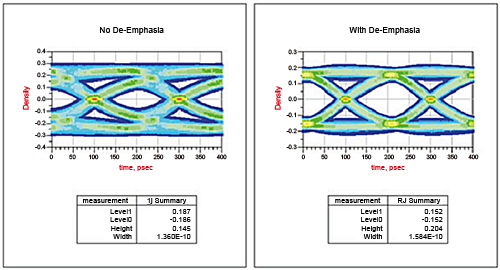

文章一開始提到,使用軟體內建的模型可以把相關的參數效能調校(Tuning)或優化(Optimization)。而在高速數位通道的IC內部使用預強化的方式可以讓眼圖有更好的表現。預強化的tap值的選擇就相當重要,可以透過ADS的Batch Simulation和眼圖探針做結合,以眼圖的寬度和高度當成評量標準,同時把tap和預強化的數學公式列出,Batch Simulation當中預強化的調整範圍從37dB,在此範圍裡面找出最佳眼圖的tap1和tap2的值。

|

| 圖7 透過Batch Mode模擬找到最佳化的Tx預強化值 |

從圖7可以知道最佳化的tap值是兩條線的交叉點,也就是在這個PCIe的通道中最佳預強化準位是在3.7dB,同時要提供此預強化的tap參數是0.826565和-0.173435。以此設定加在Tx訊號源中重新模擬一次眼圖,可以看到眼圖的改善(圖8),並且高度與寬度如同在Batch Mode模擬中所得到的結果。

以上通道中的附加介面卡、系統板和Package都是使用內建的多層傳輸走線模型,(在繪製Layout之前)這些模型可以快速分析到一定程度的最佳解決方案。但為了考慮更接近實際狀況的干擾與寄生效應,應用電磁模擬來萃取實際Layout的模型是必要的。Layout是從Cadence Allegro軟體透過ADS Layout轉換軟體可以非常容易地把差分對的走線、Via、Power/Ground平面和板材材料特性一起匯入到ADS,透過ADS Momentum萃取出S參數,同時軟體提供Layout Look Alike功能讓使用者即使在電路環境也可以看到Layout的俯視圖,很直覺地連接到正確的相對位置。

|

| 圖8 3.7dB預強化對眼圖的改善 |

除了加入Layout的模型讓模擬可以更接近實際狀況外,這裡在圖9中也加入同頻段的干擾訊號源,這個干擾訊號源的相位、上升/下降時間還有抖動雜訊(Jitter)值都是使用者可以自定義的。最後的眼圖模擬結果可參考圖10。

|

| 圖9 加入實際Layout模型,干擾源和接收端(Rx)的PCIe通道 |

電源完整性模擬

|

| 圖10 最後Rx輸出的眼圖和相關模擬值 |

電源分布網路(Power Distribution Network, PDN)的作用是把電源傳輸到系統當中所有的IC,每顆IC都有自己所需的功率,同時在電源網路的不同位置所能承受的電壓擾動也都不同。

以賽靈思(Xilinx)Kintex-7現場可編程閘陣列(FPGA)為例,其類比電源線的輸入電壓擾動在10K80MHz之間不能超過10Mv。而電源線自體產生的電壓擾動是頻率的函數,可以用公式1的歐姆定律(Ohm's Law)來簡單表示:

Voltage(Frequency)=Current(Frequency) X TargetImpedance(Frequency) ...............................公式1

因此得知某顆IC電源網路的電流和擾動電壓的限制,就可以決定目標阻抗(Target Impedance)的限制。而整個電源網路設計的目標就是要控制Target Impedance小於一定值來使電壓穩定。

|

| 圖11 IC內部的Target Impedance |

通常用來降低Target Impedance的方式是,在適當的電路位置加上電容來改變整體的電阻值,IC內部所使用的電容可以降低較高頻的Target Impedance(圖11),而印刷電路板和封裝內的電容是用於降低一到幾百MHz的阻值。

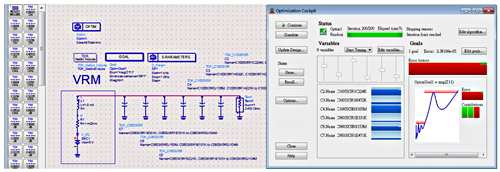

以印刷電路板上的電容優化為例,通常要同時加上許多顆電容,但在這麼多的電容型號中,設計者要如何決定哪一顆型號的電容能讓阻值降到最低。透過ADS Optimization與元件資料庫(Component Library)的搭配,設定好阻抗(Impedance)在不同頻段的目標,軟體可以快速選出那一個組合可以達到最佳的效果。

圖12就是一個簡單的示意範例,搭配製程設計套件(PDK)實際的電容資料庫,穩壓模組(VRM)和IC端點之間以六顆電容的優化成功使阻抗降到要求的範圍之內。而實際的電源網路模型可透過適當的電磁模擬來萃取出印刷電路板的S參數,指定適當的電容模型於適當的埠(Port)透過ADS Optimization同樣能快速地選取到最佳電容組合。

|

| 圖12 使用軟體優化功能讓Target Impedance調整到要求的範圍內 |

在整體系統當中會有一些IC對於雜訊特別敏感,由於所有IC共用同一個電源網路,不同IC的雜訊會藉由電源網路流串進而影響到其他IC。像是鎖相迴路(PLL)對於雜訊就非常敏感,因此對於雜訊抑制要求特別高。

圖13是一個IC因為抽取1安培(A)的電流並且透過Vcc電源網路讓雜訊影響到PLL的輸入電壓,而觀察此影響大小的參數稱為轉換阻抗(Transfer Impedance)。同樣地,Transfer Impedance越小,代表IC雜訊抵抗能力越高,電壓也就更為穩定。

|

| 圖13 Transfer Impedance示意圖 |

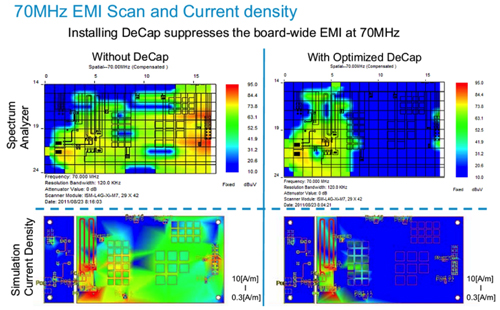

電源網路的設計優劣甚至會影響到系統的輻射強度,而在量測方法常使用的近場輻射可以分析局部磁場的大小以找出可能產生輻射的IC。此外,電流密度的差異是造成磁場強度不同的主要原因,所以透過分析某一頻段的電流密度,相對地就可以得到與近場輻射掃描接近的結果(圖14)。

|

| 圖14 近場掃描量測值與電流密度的模擬值比較 |

以ADS軟體為例子,當印刷電路板Layout的S參數模型透過動量(Momentum)電磁模擬萃取後,回到電路環境(Schematic)給予適當的供電模組和抽電流的IC,並且設定使用者關心的頻率,就可以觀察在此頻率底下的電流密度。因為是使用全波演算法的Momentum來做模型萃取,因此可以把印刷電路板走線當成天線來模擬特定頻率的輻射電場強度和輻射的放大增益值。所以,在設計階段可透過模擬軟體來確定最佳化的解除耦合(Decoupling)電容,不只改善電源網路的穩定,同時也可確定哪一種設計會有較少的輻射干擾問題。

選對軟體/演算法 設計效率倍增

現今高速數位系統不斷發展出更快速的標準,印刷電路板系統對於訊號完整性與電源完整性分析的需求也更顯的重要。訊號、電源和輻射干擾的問題已經不是單一的設計問題,通常須要共同設計來避免後續更多的延伸狀況。選擇適合自己系統的軟體與演算法可大幅提升設計效率,並且降低研發成本。

(本文作者任職於安捷倫)