現今大多數的超寬頻(Ultra Wideband, UWB)晶片都選擇以3G~5GHz間的頻組一(Band Group 1)做為通訊頻段。但因為全球法規環境偏好6GHz以上的頻段,因此只能在頻組一運作的UWB方案的應用市場區域便受到限制,此外,使用UWB技術的高速藍牙(High Speed Bluetooth)將只使用6GHz以上的頻段,所以通訊頻段能夠橫跨整個3.1G~10.6GHz範圍的UWB晶片設計便是眾望所歸,產品設計人員也因此能享有最大的彈性。

然而這樣的寬頻設計卻對射頻晶片的設計人員帶來莫大的挑戰,因為現今大多數的互補式金屬氧化物半導體(CMOS)製程對於運作頻率在6G~10GHz這個區間的射頻電路模型並沒有清楚的定義。矽鍺設計的風險最低、效能最高、產品上市速度也最快,而全部採用CMOS的單晶片解決方案則有極小封裝尺寸,而且在良率到達一定水準之後也具備成本上的優勢,所以也為一項相當誘人的選擇。但是,要將原本採用矽鍺製程的電路設計轉換到CMOS製程,必須在事前做好審慎的規畫,因為原本採用矽鍺製程的電路設計常常不適合以先進CMOS製程(例如65奈米製程)來實現,所以設計人員在設計時,如果抱著將來要從矽鍺製程轉換到CMOS製程的想法,許多架構便須要重新設計。將矽鍺轉為CMOS的過程牽涉許多風險,除非設計人員很清楚未來要重新設計的電路有哪些,同時在初期僅使用少量矽鍺架構,以減少轉換至CMOS時的更改幅度。另外,因為在轉換到CMOS製程的過程中,設計人員必須進行多次試產才能釐清CMOS所應採用的射頻模型為何,因此過渡期中的設計週期便需要額外的花費與時間。

本文將分析實作全球通用UWB解決方案時,該如何在矽鍺和CMOS兩者之間做取捨,也會說明可涵蓋3.1G~10.6GHz範圍的設計選擇及其作法。此作法在CMOS製程中採用極少量的矽鍺,所以之後可以輕鬆轉成全CMOS製程。此設計策略將加速獲利時間並將風險最小化,在良率改善時可快速轉為全CMOS解決方案,同時避免造成效能衰減。

WiMedia實體層概觀

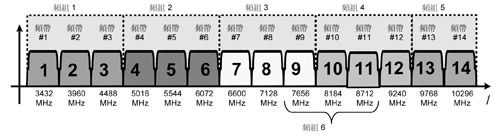

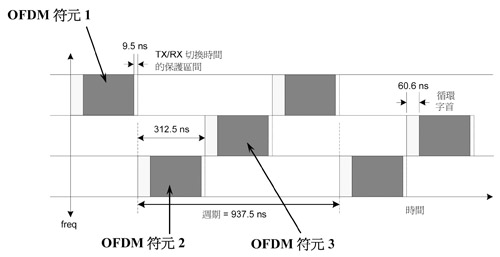

多頻帶正交分頻多工(Multiband OFDM, MB-OFDM)無線電由WiMedia聯盟(WiMedia Alliance)開發,採用了如802.11a、802.11g、802.16e、數位用戶迴路(DSL)等OFDM系統上已經過驗證的概念,並將這些概念應用於高頻寬與高傳輸率上。WiMedia實體(PHY)層規格詳細說明了MB-OFDM的架構,其中定義WiMedia系統有一個528MHz的瞬時頻寬(Instantaneous Bandwidth),可以3.2MHz(312.5ns)的速率於3.1G~10.6GHz範圍中三個不同的頻段間切換(圖1、圖2)。反之,傳統的OFDM系統將一百二十八點快速傅利葉轉換(FFT)用在整個528MHz頻段,讓每一子載波有基本的4.125MHz解析度。

|

| 圖1 WiMedia PHY頻帶配置 |

|

| 圖2 運作於時頻交錯(TFI)模式下MB-OFDM系統的時頻安排 |

美國聯邦通訊委員會(FCC)要求UWB系統最低頻寬要達到500MHz,並規定其必須在3.1G~10.6GHz間運作。除此之外,根據FCC之前的解禁令中對UWB輸出功率的規範,UWB在1毫秒(ms)區隔間的平均功率輸出不得超過-41.3dBm/MHz,且其瞬間最高功率不可超過0dBm。所以,如果WiMedia無線電未進行被稱為混頻交錯(Fixed Frequency Interleaved Mode, FFI)模式的頻帶切換時,可以大約P

T-FFI=-41.3+10Log

10(528x10

6)=-14.1dBm運作。但由於WiMedia系統可在三個頻段上的平均分散其輸出功率,因此在切換模式時,無線電輸出功率可增至P

T-TFI=-14.1+ 10Log

10(3)=-9.3dBm(注1)。

由於UWB技術本質的緣故,接收到的訊號毋須高訊號雜訊比(SNR)。WiMedia PHY規格只要求最高4.9dB的訊號雜訊比(於480Mbit/s的最高傳輸率時)。假設雜訊指數為輕微的6.6dB而阻抗損耗為3dB時,對應的敏感度要求為-72.7dBm。動態範圍可以基頻中的訊號量化雜訊比(Signal to Quantization Noise, SQNR)來表示,當資料傳輸率為53.3~200Mbit/s時,其動態範圍最低為24dB(4位元),資料傳輸率為200~480Mbit/s時則是30dB(5位元)。干擾保護、類比數位轉換器(ADC)限制和其他損耗可能會使ADC的實際位元數稍高於這個數字。

頻譜主管單位傾向採用高頻

現今開發的多數WiMedia UWB系統皆於3G~5 GHz頻帶間運作。這樣的設計明顯為UWB產業帶來最低的風險、快速上市時間,但美國以外的法規架構在第一代系統誕生後已有所改變。法規之所以有影響是因為UWB是一種「底層」(Underlay)技術,它是一種信號強度極低的無線技術,因此與其餘無線電就算在近距離內也可共存,也能重複使用可用的頻譜而不造成有害干擾。雖然FCC接受這樣的概念,但其他國家的主管單位卻未必能接受這種說法,因為目前在量化「有害干擾」(Harmful Interference)這個抽象概念方面並無被普遍接受的共同作法。

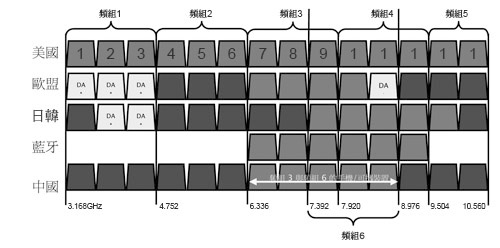

由圖1可看到WiMedia PHY定義的頻道共有十四個,但可用的頻道卻隨各地法規而有所不同(圖3)。至2008年年中,頻組一中只有一個頻道於全球各地皆為合法頻道(頻道三),這便限制了頻組一(注2)的使用。6GHz以上頻段受到的限制較小,可用頻道數量也較多,且這些頻帶中既存的系統數目也較少,所以法規單位擬定規範時受到的反對聲浪便較少。最後,藍牙技術聯盟(Bluetooth SIG)也表示將用於藍牙服務的UWB系統只運行在6GHz以上的頻段。

|

| 圖3 目前世界各國開放UWB通訊之頻段概況 |

所以,基於各種原因,所有未來的UWB都將必須支援6GHz以上的頻帶。這對UWB晶片設計人員來說將是一大負擔,因為無線USB與UWB應用的目標都放在需要大量、低成本解決方案的消費性裝置上。為了滿足消費市場的特性,開發高度整合的解決方案勢在必行,但也因而必須做出一些取捨。

打破CMOS才能帶來最低成本的迷思

CMOS製程或許無法實現效能最佳或最省電的射頻電路,但由於摩爾定律的緣故,半導體產業傳統上認為單晶片CMOS無線解決方案就是成本最低的解決方案。在全數位電路中,傳統CMOS單晶片固然幾乎是各種製造技術中成本最低的,但在無線系統中卻不盡然如此。舉例而言,Zheng等人的論文表示單晶片解決方案用於藍牙等簡單的射頻解決方案時,的確成本最低,但對更為複雜的射頻系統如UWB而言,由於複雜的良率問題,系統級封裝(SiP)或結合多種IC技術的模組可能更為適合。在傳統CMOS、RF CMOS、CMOS加上矽鍺BiCMOS、GaAs或其它製程技術之間作選擇時,有幾個彼此截然不同的根本因素必須考慮,如運作頻率與頻寬這兩項要素由產品的規格來決定;產品的絕對生產成本、功耗則是由市場要求來決定的。設計人員必須在上述各項要素間做出平衡取捨,例如為了將生產成本壓到最低,一次設計就成功,並維持高生產良率便極為關鍵。而為了達成此一目標,採用成本較高的製程技術來進行設計量產,便成為一個可以更深入討論的議題。

另一方面,架構彈性也是不可忽略的要素。由於WiMedia定義了媒體存取控制(MAC)層與PHY之間的標準介面,因此系統整合製造商擁有可以選擇來自不同供應商的MAC與PHY元件來組成系統產品的彈性。

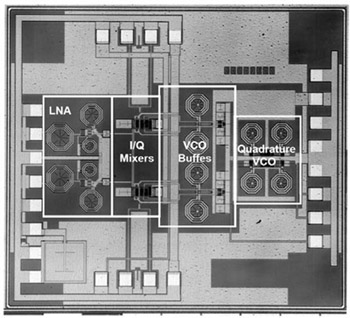

在無線的世界裡,以CMOS製程生產的半導體解決方案並不保證能勝出,因為摩爾定律並不完全適用於混合訊號與射頻電路。如果要了解其中原因,可參考圖4的5GHz無線區域網路(WLAN)收發器。如圖4所示,在這個收發器晶片裡,電容與電感占據了一大片面積,且還有很大一部分是完全閒置的。此狀況幾乎出現在所有無線晶片的收發器區域上,UWB系統更是如此。另外,電感與電容的區域大小並不會依摩爾定律呈線性縮減,所以這塊空間在90奈米與更先進的製程技術中就變成一種浪費。還有其他因素讓問題更加嚴重:由於收發器是射頻/類比訊號元件,且其所接收的訊號功率可能很低,例如輸入低雜訊放大器(Low Noise Amplifier, LNA)的訊號功率可能僅有10-11瓦。以先進製程來生產這類電路會製造大量的雜訊與交叉耦合問題,並直接影響良率、設計一次成功機率、和電路效能。因此,若有另一個解決方案可以符合上述條件,且成本相同甚至更低,選擇單矽片解決方案就不再具備固有優勢。事實上,如果良率與效能不佳,單矽片解決方案可能會產生一些重大的缺點。

|

資料來源:www.bell-labs.com/org/physicalsciences/pubs/liu.pdf

圖4 5 GHz無線區域網路RF LNA/混頻級 |

相較之下,另一種策略的成本會比全CMOS解決方案的成本低,且效能更佳。這種策略即是採用CMOS製程,但在射頻區植入矽鍺,再加上以深次微米CMOS製程生產的基頻處理器(Baseband Processor, BBP)和MAC。就晶片運作頻率、頻寬、絕對成本、功耗與接收敏感度等關鍵要素進行分析,這種生產策略有以下優勢:

|

|

| |

以傳統CMOS製程來實作運作頻率在6GHz以上的射頻收發器在良率方面一向較差,若要透過改善射頻模型來提高電路良率,將須測量眾多測試結構,特別對90奈米及以下細小的電晶體時更是如此。就算測試結構的測量很好,對CMOS系統中的多矽電容等裝置而言,製程、電壓、溫度等的變化都可能大幅降低射頻電路的良率。RF CMOS製程中的金屬-絕緣體-金屬(Metal-Insulator-Metal, MIM)電容可有較好的公差。 |

|

|

| |

528MHz頻寬需要的ADC必須能在4、5或6位元解析度以最小每秒取樣率528MS/s的速度對複雜訊號取樣。傳統CMOS可達成此要求。 |

|

|

| |

此因素很重要。假設以90奈米CMOS製程來實作的BBP+MAC面積為10mm2,而以0.13微米矽鍺製程來實現的射頻區面積為3mm2。若改以90奈米製程CMOS製程來實作這個射頻收發器,並將之與BBP和MAC整合成單晶片,其面積可能只能縮小到2.5mm2。在這個情況下,CMOS加矽鍺解決方案可能會比單晶片CMOS要便宜1.27美元。混合解決方案在這個案例中之所以具備高成本效益的原因在於它只須多加幾個步驟就可在傳統CMOS製程中植入矽鍺,且良率很高。 |

|

|

| |

如果CMOS射頻電路設計採用比矽鍺製程更先進一代的技術來實作,矽鍺電路可在維持原效能的狀況下節省30%的電力。 |

|

|

| |

如果將LNA與其他對雜訊敏感的結構置於和數位電路同一個基底上,基底雜訊極可能會導致敏感度衰減。有一分調查顯示CMOS無線區域網路系統單晶片需有51dB的抗雜性,但這點非常難達到。 |

|

|

| |

若將射頻收發器從BBP+MAC上獨立出來,設計人員可以分別選擇符合功耗、敏感性與成本要求的元件,達成一適當的平衡。 |

|

|

| |

Jazz Semiconductor表示矽鍺晶片與同樣尺寸的CMOS射頻晶片相比時,良率一定較高。稍後本文將討論這點。 |

慎選正確的整合策略

過去的歷史顯示傳統CMOS射頻電路設計所遇的挑戰會隨著時間以及更聰明的設計方式出現而被克服。目前在螺旋型電感、各種多矽電容補償與其限制頻率回應、抑制CMOS製程雜訊指數等方面,已有多方研究。CMOS UWB晶片的效能與良率應該會隨時間而有更大的接受度,但即便如此,晶片設計人員仍須多次重製(Re-spins)其設計,以修正出一個可被接受的解決方案。深次微米尺寸的光罩組很昂貴,測試結構的評估又費時,所以採用直接傳統CMOS解決方案的半導體公司面對的風險很高。為了反覆琢磨出效能與良率皆可被接受的CMOS解決方案,可能要費時好幾年,且成本可能高達幾千萬美元。

此外,要以高頻射頻測試晶圓非常困難,所以大部分廠商被迫要將其產品切割與封裝,才能讓射頻電路受測試。如此一來不良率的影響將倍增,因為連瑕疵品都須負擔封裝成本。

現在假設有一個晶片結合了射頻和數位功能,如果此晶片在測試前必須被封裝,其良率表示方式如下:

成本=[(晶圓成本/每晶圓矽片)+測試成本+封裝成本]/良率

如果假設製程為CMOS與矽鍺的混合製程,那麼估計晶圓與一般CMOS晶圓相比的成本溢價約為20%,但CMOS加上矽鍺的封裝部分良率卻會大幅提升。如果又進一步假設這些部分的測試與封裝成本大略相同,便可比較兩個策略,如表1所示。

表1可說明如果CMOS混合矽鍺的良率為70%,傳統CMOS晶片的良率必須超過63.6%才可將成本降得較低。此分析意味著最快獲利的方式就是在初期使用CMOS混合矽鍺的解決方案,然後隨著時間過去,當傳統CMOS的良率改善到與混合製程相當時,傳統CMOS才會更具成本效益。但必須注意的是,標準CMOS製程或許永遠都無法在雜訊、線性等特性上達到可與混合製程一較高下的程度。

| 表1 單晶片解決方案採用傳統CMOS與CMOS+矽鍺的成本比較 |

| |

CMOS |

CMOS w/SiGe |

| Wafer Cost |

$ 2,000.00 |

$ 2,400.00 |

| Raw die/wafer |

$ 1,000 |

$ 1,000 |

| Die cost (unyielded) |

$ 2.00 |

$ 2.40 |

| Yield (%) |

60% |

70% |

| Test cost |

$ 1.00 |

$ 1.00 |

| Package cost |

$ 1.00 |

$ 1.00 |

| Die cost (yielded) |

$ 3.33 |

$ 3.43 |

| Finished goods cost |

$ 6.67 |

$ 6.29 |

根據以上分析,對資金與設計資源有限的公司來說,最好的策略是採用CMOS+矽鍺解決方案打入市場,可快速獲利又可同時盡量利用矽鍺發展傳統CMOS解決方案。一旦CMOS架構成熟至良率與CMOS+矽鍺解決方案相等的程度,晶片開發商即可轉向傳統CMOS設計。

以Alereon的AL5000晶片組為例,其類比前端(Analog Front End, AFE)使用IBM 8WL製程生產。此製程為一標準傳統CMOS製程,但在射頻區植入矽鍺,再結合0.13微米台積電(TSMC)標準CMOS製程生產的BBP+MAC。這樣的組合讓AL5000晶片組在整個3.1G~10.6GHz的UWB頻譜上有卓越的效能,且良率遠較標準CMOS製程為高。此UWB/無線USB解決方案過去只試產兩次便進入量產,如果射頻區也以傳統CMOS生產的話,這點便不可能達到。

Alereon正積極將此解決方案轉換成單晶片CMOS解決方案。而Alereon在AL5000這代晶片的獲利與累積經驗對Alereon的製程轉換也有正面助益。系統整合廠商也將從中獲益,因為未來的解決方案成本低、尺寸小、功率低,但與先前的晶片具備同樣的軟體基礎。消費者也因而能享受到更價廉物美的系統產品。

超寬頻技術就像其他已經在消費市場上成功站穩腳跟的無線通訊技術,如藍牙、無線區域網路一樣,須要經過一段合理的製程演進過程。因此正確的設計策略是在產品生產初期採用CMOS與矽鍺混合製程,先行取得市占與系統設計經驗,等到CMOS製程技術的成熟度跟上混合製程的腳步之後再進行製程技術的轉換工作,以實現真正的低成本單晶片解決方案。

(本文作者為Alereon技術長)

| 注 釋 |

注釋1:因為UWB系統不一定會在每一個OFDM符碼(Symbol)所占據的時間內持續傳輸訊號,所以實際數字跟規格中的數字略有出入。此外,在圖2中有一段顯示為循環前綴(Cyclic Prefix),長度為66.2ns的交錯區間,但在最終的規格標準中,UWB是零前綴的技術。這段「沉默時間」將UWB系統的輸出功率降低了1dB,也移除了循環前綴所造成的譜線(Spectral Line)。

注釋2:至2008年5月為止,中國尚未宣布定稿法規,但預期年底會宣布。圖3所示的頻帶是根據2006年底所公布的草案。 |