數位訊號處理(DSP)是由一個數位或符號的序列來表示訊號,並將這些訊號轉化為人們利用數位設備便可以看到和聽到的格式。在真實生活中,訊號無處不在:吾人的所見所聞(所有的聲音、動作和物理現象)都是類比形式的。在經過適當的類比數位轉換動作後,就能夠利用DSP來進行運算處理。透過DSP所引進的多種數位功能,無論是數位格式音訊流資料的壓縮、視頻流的解壓、特定個體的識別、或者無線訊號的調變/解調,DSP都能夠一一處理,換言之,DSP是許多功能實現的關鍵。

以手機或電腦為例,就能很明顯看出DSP所帶來的特性和功能,以及其之所以在數位生活中成為不可或缺的關鍵。在手機通訊的過程中,語音壓縮、回聲消除和數位基頻功能,都是由DSP來執行。又例如電腦必須先透過程式來處理照片資料,才能將照片的內容轉化成人類可以檢視的形式。如果要向朋友發送照片,影像還要再經過處理才能進行傳輸,無論是視訊片段或靜態的照片都是如此;如要播放視頻,資料還得壓縮和解壓縮。此外,MP3和AAC音訊檔也須要經過處理,才可在電腦或數位媒體播放機收聽音樂。

藉由DSP所實現的功能,在日常生活中隨處可見。例如手機系統中便至少有兩項功能必須仰賴DSP,一項用於基頻處理,另一項用於應用處理。一些先進的手機甚至有多達五個DSP。我們日常所用的設備都帶有DSP功能:包括電腦、筆記型電腦和行動聯網裝置(MID)。在數位電視、機上盒、藍光(Blu-ray)光碟機設備、音訊產品,乃至具備資訊娛樂系統和安全控制裝置的「智慧型汽車」中,影像處理與音訊及圖形處理也是由DSP完成。

除了這些應用,DSP還用於更廣泛的產品中,例如監控攝影機等保安產品、電訊基礎設施、吹風機或電冰箱等家用電器、醫療設備、雷達系統。

不同處理器各有先天優勢

事實上,DSP功能不一定只能在DSP元件中實現。中央處理單元(CPU)、微控制器單元(MCU)和原生DSP都可以被用來實現DSP功能。

Pentium和PowerPC都是性能極高的CPU,時脈速度高達2GHz以上。CPU能夠執行訊號處理工作,但其極高的運行頻率帶來的高功耗是一大問題,不適用於嵌入式應用。MCU與CPU正好相反。MCU可以被視為Pentium這類CPU的低速小尺寸版本。安謀(ARM)和美普思(MIPS)等公司,均提供專為嵌入式應用而設計的核心。這些MCU適用於任務控制,並與作業系統完全相容。一般而言,MCU沒有DSP功能,但有些MCU則可以添加DSP功能。

第三類是原生DSP,適合運算密集型處理。它們專門為嵌入式應用而設計,具有低功耗及小電路尺寸的特點,適用於系統單晶片(SoC)。

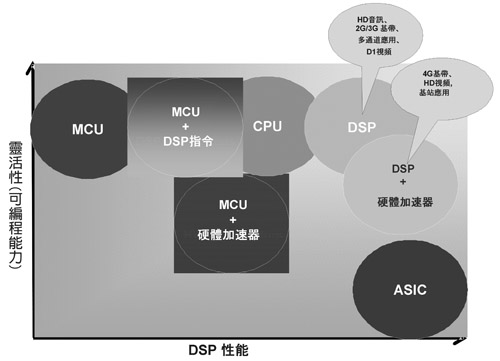

圖1是上述三類處理器的比較。X和Y軸分別代表DSP的性能與靈活性(可編程性能)。MCU是可編程的設計,能夠執行多種功能,因此MCU可以說適用於多種應用系統。

|

| 圖1 不同形態處理器特性比較 |

但MCU無法實現高性能的DSP功能,因為其設計的原意不在於此。有些MCU透過增加特殊的DSP指令來提高性能,它們既保持了靈活性,同時又提高了DSP功能的執行速度。有些MCU還帶有硬體加速器,它們雖然可提高DSP性能,但卻降低了靈活性。

與MCU相比,CPU的運行頻率如果在1G~2GHz範圍,其DSP功能執行速度就相當快。然而,功耗問題卻是其主要的應用限制,特別是在可攜式裝置中,除非採用非常大容量的電池,否則在手持式設備中採用CPU來實現DSP功能是不可能的。

原生DSP和帶硬體加速功能的DSP則可以提供最高的DSP性能。值得注意的是,由於特定應用積體電路(ASIC)以硬體邏輯來處理DSP功能,因此具有極高的DSP性能。如果系統要支援高畫質H.264圖像,可以選擇ASIC方案,但選用這類ASIC將會影響靈活性。

靈活彈性與即時處理為DSP兩大賣點

從上面的比較可知,DSP可獲得出色的計算性能。現今許多設備要求在每個時脈週期同時執行多個操作,亦即所謂的平行運算。為了滿足這個要求,處理器必須具備速度夠快的算術邏輯單位。一般而言,DSP架構具有算數邏輯單元(ALU)、乘累加器(MAC)單元和移位器(Shifter)等多種不同類型的算術單元,而它們也能夠同步操作。

精確運算也十分重要。要執行前述的運算任務,資料值的精度要求有時甚至可高達72位元。最早期的MCU為8位元,現在有8、16及32位元;而CPU則有32和64位元。不過,這兩者目前都無法滿足72位元精度,只有DSP的動態範圍能夠達到72位元。DSP具有靈活性,能夠支援多種資料類型,例如某些運算任務的資料精度需求為12、20或40位元,而且DSP所處理的資料類型,可因所選擇的類比數位轉換器(A/D Converter)而變化。

由於DSP能夠支援廣泛的記憶體頻寬,所以可同時執行多個演算法單元,這是非常重要的,因為許多採用DSP元件的系統必須隨時準備好接收和處理資料,故DSP同時執行眾多算術單元是必需的。即時處理是另一個關鍵因素,而大多數CPU和MCU都缺少即時執行功能。有時候,一項任務必須在某個時段完成。例如在視訊處理中,每33微秒就要開始一個新的影格,這意味著當前影格的資訊處理必須在下一個影格開始的時間之前完成。對於具有諸如33微秒這類明確預先處理時間要求的應用,DSP是理想的處理器。

另一個CPU/MCU和DSP最主要的不同,則是資料存放的架構。和CPU/MCU工程師大相逕庭的是,DSP工程師通常都不喜歡使用快取架構,因為它會給應用帶來某種程度上的不確定性。基於這個原因,設計人員通常選擇直接記憶體存取(DMA),因為DMA規定了運算和/或存取記憶體的確定時間,而快取架構可能無法滿足即時要求。但在某些情況下,DSP還是可以利用快取記憶體來進一步降低晶片的整體尺寸。另外,DSP還具備預測資料存取模式和降低功耗等優勢,這些都是吸引工程師選擇使用DSP的重要原因。

由於上述處理器類型各有優劣,故工程師可能會為選擇DSP還是MCU而猶豫。如同本文先前所提到的,目前市場上有一些具備DSP功能的MCU方案,允許工程師利用MCU來執行訊號處理,但這類方案可能無法滿足效率需求,因為MCU不一定能夠提供完整的基本DSP功能。

另一個工程師經常提到的問題是:DSP能夠用於控制應用嗎?答案是肯定的。DSP也許無法在控制應用中提供最高的效率,但當系統須徹底省下MCU的成本已達到降低成本的目標時,採用DSP是一種合適的方案。

有些IP供應商提供結合MCU概念與外加DSP功能的產品,這看來似乎是合理的選擇,特別是在考慮到晶片尺寸、成本與功耗等項目時,MCU提供了良好而均衡的解答,讓工程師可以獲得很好的系統效率。不過,這個說法僅在對DSP功能需求不高時能夠成立,如只需要幾項非常基本的DSP功能時。

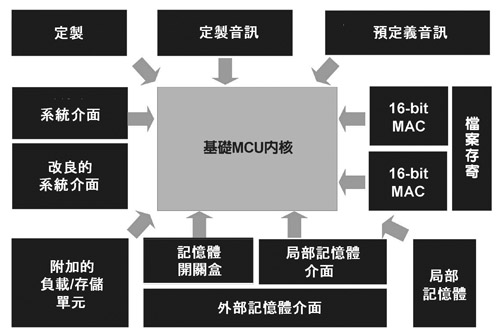

在MCU中實現DSP功能的方法是選擇預定義清單中的DSP功能,並把它們增加到MCU中。例如工程師可以從目錄中選擇MAC單元、乘法器、負載/存儲單元、算術單元、寄存器檔和記憶體介面等。工程師還可使用各種資料開關或定義自己的指令。

處理器設計牽一髮動全身 弄巧成拙機會大

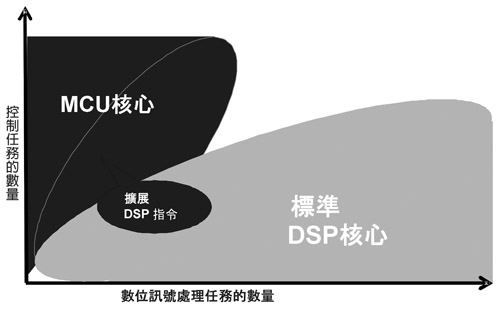

在MCU中添加DSP功能有時是個很不錯的想法(圖2),然而值得注意的是,如果工程師要在原本不支援DSP功能的MCU架構中自己動手修改,這個架構也許會變成一個充滿補丁(Patchy)的架構,且加入一個非標準處理器經常會導致問題叢生。

|

| 圖2 混合DSP與MCU的設計架構有一定的市場利基 |

且用圖3來解釋何謂一個充滿補丁的架構。假設某設計人員要在一個規模約在三~四萬門邏輯閘的MCU上增加音訊DSP功能,而該MCU原本就具備幾個支援基本程式控制功能(如單點存取資料記憶體)的寄存器。改造工作的第一步是增加積和(Sum-of-products)操作功能,因此設計人員加入了兩個16位元的MAC單元,如果這些單元是預先定義的,設計人員就可以把保存資料和結果的寄存器檔添加到這兩個MAC單元中。

|

| 圖3 在MCU中添加DSP功能導致統架構充滿補丁 |

只要經過上述改造,理論上MCU就可以扮演音訊DSP的角色,若性能不夠,設計人員必須增添更多的預先定義的音訊指令。有些供應商提可供這類能加快音訊處理速度的指令。不過,由於在MCU架構中增加客製化的指令和/或演算法來提升性能,若未來設計人員想在SoC中增加語音處理功能,就必須增加更多的自行定義的指令。而且每當設計人員想增添一項額外功能,都得重複這個步驟。

到了這一階段,設計人員可能會擔心資料記憶體的存取性(Accessibility),因為核心MCU只能單次存取資料記憶體。但在DSP中,由於至少須兩次記憶體負載存取才能有效取得資料,因此設計人員必須增加一個額外的負載/儲存單元。這時,設計人員又得在CPU架構中增加一個記憶體開關,以切換內部單元和外部單元。增加本地記憶體意味著你需要一個本地記憶體介面。如果內部記憶體不夠,還必須再增加一個介面來存取外部記憶體。但這仍然不足夠,由於音訊DSP只是這個系統的一個元件,故設計人員最終還得要再增加一個系統介面,而且還很可能必須擴展這個介面。這樣一來,設計人員就須增加多個系統介面。

由於MCU架構彼此之間的關係如此牽一髮而動全身,設計人員只要稍作修改,很快就會把原本完整的架構弄得像百衲布一樣到處充滿補丁,再也不是原本的樣子。

在這樣一個補丁的架構中,設計人員必須確保多種功能有效地運作,資料流程是其中一個關鍵要素。以使用MAC操作的資料流程為例(這也許是最基本的DSP功能),其位址透過本地記憶體介面從外部負載/存儲單元存取本地記憶體。當資料透過外部開關進入MCU中的DSP模組時,資料必須寄存在一個外置寄存器檔中,然後再被傳送到內部寄存器。由於其資料流程如此複雜,其程式設計的困難度也就可想而知。

這種補丁架構的另一個問題是這樣的DSP缺乏某些基本功能,如執行巢狀迴路(Loop-nesting)等。此外,這類架構也缺少一些基本的DSP定址模式,比如迴路緩衝器和位元倒序(Bit-reverse)模式。

此外,這種「可組態MCU」還存在一個問題,即非標準。非標準的架構將導致軟體維護變得極為困難,因為設計人員在使用這種MCU進行系統開發時,必須重複地把軟體從一個架構移植到另一個架構,而且不能重覆使用代碼。這也意味著協力軟體廠商所開發的代碼未必能在調整過後的配置上正常運作,因為有些指令和機制是不同的。

其實,設計人員可以不必如此大費周章,只須選擇為滿足特定應用的要求而設計的本地DSP,就完全可以避免可配置MCU的所有缺陷,例如針對藍光光碟機應用開發處理器時,只要選用對應的DSP矽智財方案即可。

嵌入式DSP成為SoC設計重用之關鍵

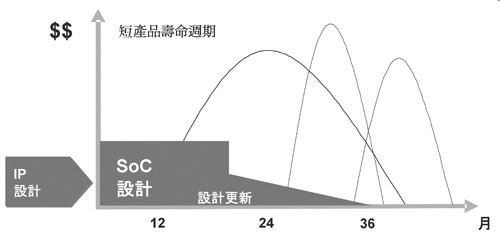

最後,從市場趨勢面來看,訊號處理技術在產品使用壽命和開發成本方面,已經出現大幅轉變。過去幾年,廠商可以持續銷售以同一產品和晶片所開發的不同應用,這可讓企業充分利用資源、時間和成本來開發處理器。

然而,新推出的65奈米和45奈米互補式金屬氧化物半導體(CMOS)製程使光罩成本大幅度增加,同時晶片設計的複雜性也因為更高的功能整合而增加,這些因素均使得處理器晶片的開發成本越來越昂貴。但晶片供應商產品開發的速度不能因此而放緩,因為終端產品的生命週期越來越短。現在已經很少有生命週期超過一年的消費性電子產品了,因此,系統客戶會期待半導體元件供應商定期推出新版解決方案,這為晶片供應商帶來了巨大的挑戰。

在這樣的情況下,如果能在產品中重覆使用SoC(圖4),即在多個產品和多款版本中使用相同的SoC,是最為理想的做法。要達到這個目標,目前的趨勢是,在SoC中把原始DSP當作可編程設計引擎來執行,產品將建立在軟體設計的基礎上。晶片廠商不必為特定功能增加處理器和進行配置,而只須透過增加/改變軟體,就可實現新的功能。

|

| 圖4 透過軟體來實現SoC設計重用才能滿足快速改版需求 |

(本文作者為CEVA企業市場拓展副總裁)