現今系統單晶片(SoC)、數位訊號處理器(DSP)、微控制器(MCU)等晶片的功耗改善已展現一定成果,但設計團隊在IC設計上仍有改善空間。尤其相關設計若能順利掌握,將有助功耗的銳減。

雖然以電池供電的系統或許是最常被探討的議題,但其實功耗問題無所不在,從千瓦額定電壓的工業馬達、行動電話,到每週啟動一次傳送遙測資料的感應器啟動裝置。單是美國地區的能源消耗量,預估至2020年便會成長32%。如此龐大的用電需求,對自然資源、供電系統、財政支出、企業成長,皆會造成沈重的負擔。

目前的節能趨勢,讓功耗效能議題顯得益發重要。10多年來,工程師致力於解決功耗問題,且已在功耗管理晶片、系統及軟體方面有重大的進展。

目前,製程工程師已能於製程技術中降低供電電壓,並縮減電晶體尺寸。而DSP、應用處理器及MCU的設計人員也皆針對功耗問題發揮其創造力,包括持續增加節能模式的種類、時脈閘控、配合低功耗製程的低功耗元件庫(Cell Library)等。此外,系統設計人員與軟體工程師也開發出許多低功耗選項。

雖然產品功能不斷增加,消費者對產品的預期也持續提升,但唯一不變的是以低功耗滿足更多需求的法則。半導體技術結合效率及相關知識,可提升晶片與系統設計的效能,並將其運用於日常使用的產品中,進而協助消費者達到有效節能,因此成為節能的重要關鍵。

接下來應如何朝下一個階段邁進?業界可檢視目前的趨勢,觀察未來的發展方向,並加以規畫。技術與科技的整合可提供部分的解決方案,正如生活中許多事物,整體通常會優於各部分的總和。

高階製程有助降低功耗

隨著製程節點由90奈米演進為65、45奈米,晶圓業者所生產的晶片功耗也更低,因為當晶片密度較高時,其所需電壓也較低,而功耗會與電壓平方呈正比。不過在過程中仍須有所取捨,因為先進製程的絕緣層較薄,在特定電路靜止時,漏電量會較大。

為能在DSP、應用處理器或SoC未增加功能價值的期間,控制主動電流電力流失的情形,IC設計人員便發明時脈閘控等各項技術,可關閉晶片未使用的部分。

若能於系統未使用晶片時將其關閉,便能達到更顯著的成果。這種技術雖然有效,但有時須同時配合運用超低功耗的MCU,此外,當系統要求較大的晶片啟動時,啟動過程必須能立即執行,且SoC也須快速啟動,因此便需要MCU與SoC緊密連結。

雖然這些技術十分重要,但仍可從更細微的方面達到節能目標。例如,近期問世的技術便運用製程邊界的差異,監控裝置的活動、操作模式、矽接面的溫度等。

系統設計人員便可運用此資料,動態調節電壓與頻率,使功耗效能最佳化。該技術也可於多核心晶片中調節功耗,以降低晶片等級的功耗。

適度調配晶片具優勢

DSP與SoC可實現多項降低功耗發展,但根據定義,這些裝置皆屬於高閘數裝置。因此,有時依據負載週期的狀況,將部分功能移出晶片外可更加省電,例如以低功耗MCU做為系統監測器。但這項做法須符合兩項需求,一是晶片間通訊須快速、穩定、有效率,二則是MCU須以極低功耗運作,且能快速啟動與關閉。

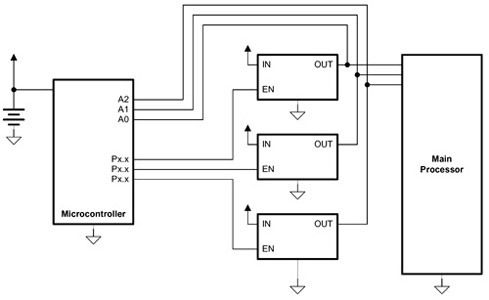

圖1以小型MCU對主處理器進行功耗排序與管理。MCU的軟體例行程序,可使主處理器的調整器正確排序,並在電源軌達到適當電壓時,以內部類比數位轉換器(ADC)進行驗證。因此,當毋須使用主處理器時,便可透過調整器的關機功能關閉主處理器,並將主處理器耗電量節省約70微安培,至數毫安培。

|

| 圖1 MCU 對主處理器進行功耗排序與管理 |

對於需要簡單並具備持續啟動功能的系統而言,採用附加的MCU執行這些工作,可以較高閘數SoC或DSP節省更多電力。其他類似的系統或監測功能包括電源監控與重設、電源排序、保持即時時脈、人機介面管理、電池管理與顯示器管理等。

DSP通常具有多重電源軌,必須在電源恢復時加以排序以正常運作。就系統層級而言,電源監控、重設監控、電源排序皆為基本監控功能,通常由固定功能的裝置所控管。系統設計人員在為低功耗設計選擇DSP時,應考量四大功能,包括大容量晶片內建記憶體、選擇可高度控制周邊裝置的DSP,以節省更多電力、選擇具多重待機狀態的DSP,以及選擇具開發軟體的DSP,該軟體專用於將電力使用最佳化,並將功耗降至最低。

這些固定功能裝置雖能有效管理處理器的功耗,但除此之外,對系統毫無用處,尤其無法關閉不須使用的主處理器。因此,以低功率的小型MCU取代上述裝置,不僅可管理主處理器的功耗,還可執行排序、監控、系統級監測功能。

然而,針對第二項需求,系統設計人員在選擇MCU作為監測處理器時,必須將MCU本身為一節能裝置列入考量。製程技術與操作電壓固然是關鍵要素,但MCU架構也同樣重要。在許多情況下,功耗最佳化規則可同時適用於MCU、SoC及DSP。

例如,MCU應具備足夠的單晶片記憶容量,大幅減少或完全避免晶片外的資料存取,具備整合式類比區塊,但不會衝擊類比效能,應可啟動及關閉本身周邊裝置,或在資料僅前後移動時,具直接記憶體存取(DMA)功能。

DMA功能尤其重要,原因在於若MCU只收集ADC樣本或移動資料,則會浪費大量電力。ADC可運用DMA功能,直接將資料樣本存入記憶體,並使MCU進入待機狀態,在樣本達到所需數量後,再啟動MCU以便處理樣本,並快速回到待機狀態。

目前針對MCU低功耗所做的創新設計,可依據處理負載量,動態調整核心電壓與時脈速度。如前文所述,MCU功耗與電壓的平方呈正比,而MCU的時脈速度則與核心電壓呈正比。使用者可於高或低處理負載量期間,即時調整時脈速度與核心電壓,使MCU功耗達到最佳狀態。

就功耗與系統效能而言,SoC及DSP與其電源間的交互作用,是主要的系統級問題。供電量過大會浪費能源,但若供電量不足,效能便會降低。

若要將供電量調整為適合較大IC需要的電量,就須充分了解DSP在最大電壓下的最大負載量,但此項資訊通常要到DSP設計週期快結束時才能取得。

電源恢復與關閉的順序也必須精確調節。由於SoC與DSP通常具有多重電源軌,必須以特定順序供電,因此電源須於較大型晶片所需時間內,因應狀態變化。多次嘗試反應,不但浪費電力,也會降低效能。

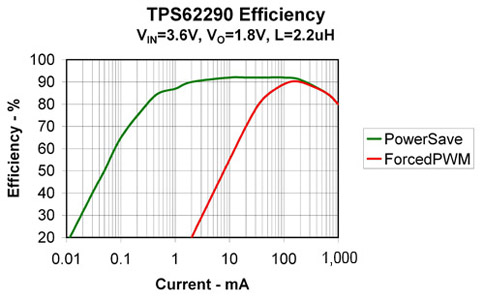

電源管理IC與相關元件透過製程技術改善及操作模式功耗降低,減少電源管理IC本身的電力損耗,以達到提升效能的目的。例如,製程技術改善可降低電力開關阻抗,減少閘電容與漏電量,進而減少I2R的損耗、切換損耗、偏壓/靜態電流。這類的先進技術改善可用於低功耗DSP與應用處理器,功耗將達原本裝置的三分之一。此外,大部分的新電源IC都具備節能模式,只會在輸出電壓下降時啟動脈衝寬度調變器(PWM),進而降低切換損耗,而非持續切換。圖2為高性能降壓轉換器效能曲線圖。

|

| 圖2 有效節能模式及強制PMW模式與輸出電流比較 |

節能須多方技術配合

既然節能技術已進一步發展,且日漸成熟,也越來越依賴IC間的交互作用。這種趨勢產生兩個問題:支援晶片是否能與DSP或SoC有效通訊?晶片間通訊是否會降低系統效能?

根據對各項趨勢的觀察結果,新一代節能技術須整合大量相關專業知識。除晶片技術持續發展外,隨著整體系統層面的功耗管理越來越重要,DSP、SoC、MCU及類比功耗管理設計人員間的開放對話與配合,也成為重要關鍵。

此外,半導體公司也須讓系統設計人員能有效運用晶片內建的精密技術,否則便無法使系統達到可能的節能效果。

開發新一代節能技術的重要步驟,在於提供系統設計人員工具,讓其能調整IC內建的電源管理功能,使系統達到最佳狀態。

就系統設計角度而言,這也需各項元件在高度精密狀態下相互配合運作,且須在SoC或DSP仍在設計階段便開始進行。類比、MCU及電源設計人員可為SoC或DSP設計團隊提供十分重要的資訊與資源。

(本文作者任職於德州儀器)