高頻寬記憶體(HBM)為世界上頻寬最高的動態隨機存取記憶體(DRAM),為需要在記憶體之間與處理程序之間最大頻寬的應用而設計。

將直通矽晶穿孔(TSV)堆疊記憶體晶粒與主機特殊用途IC(Host ASIC),無論是中央處理器(CPU)、繪圖處理器(GPU)、張量處理器(TPU)等等緊密整合至同一個晶片封裝中,以帶來最佳的頻寬。例如,美光(Micron)的HBM2E裝置提供高能效,在較小的體積提供高容量(圖1)。

圖1 美光HBM2E DRAM

圖1 美光HBM2E DRAM

HBM2E超高頻寬滿足運算密集應用

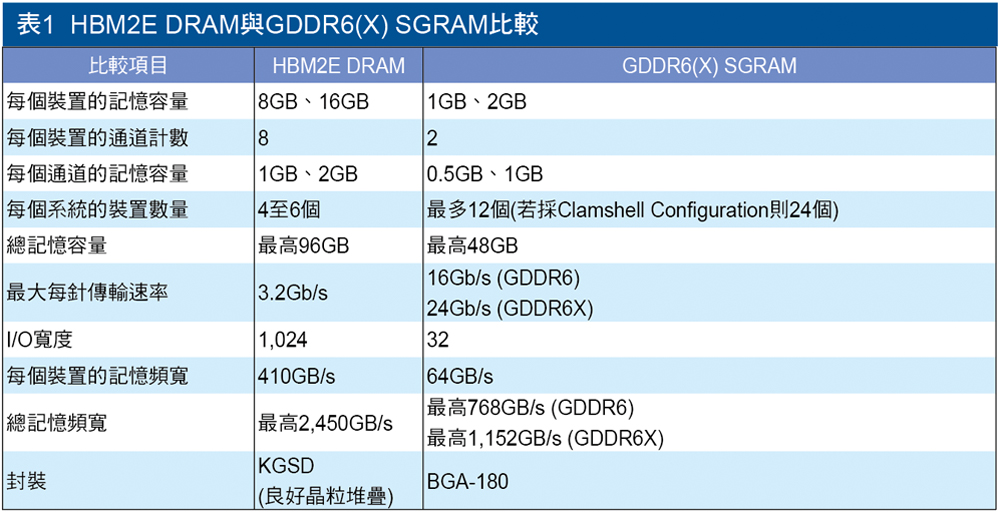

HBM2E是高頻寬方案產品,適合滿足高效能運算(HPC)、人工智慧(AI)等運算密集應用的極高記憶頻寬需求。HBM2E常用來替代GDDR6與GDDR6X SGRAM等廣為應用、同樣也提供高頻寬的記憶體。表1比較兩種技術的關鍵特性。

HBM2E DRAM的堆疊架構

HBM2E DRAM將四個或八個DRAM記憶體層,立體整合為單一堆疊裝置(未來規畫十二個DRAM層)。堆疊介面底部有額外的邏輯層或基底層,連接特殊應用積體電路(ASIC)並為HBM2E DRAM增加其他功能。

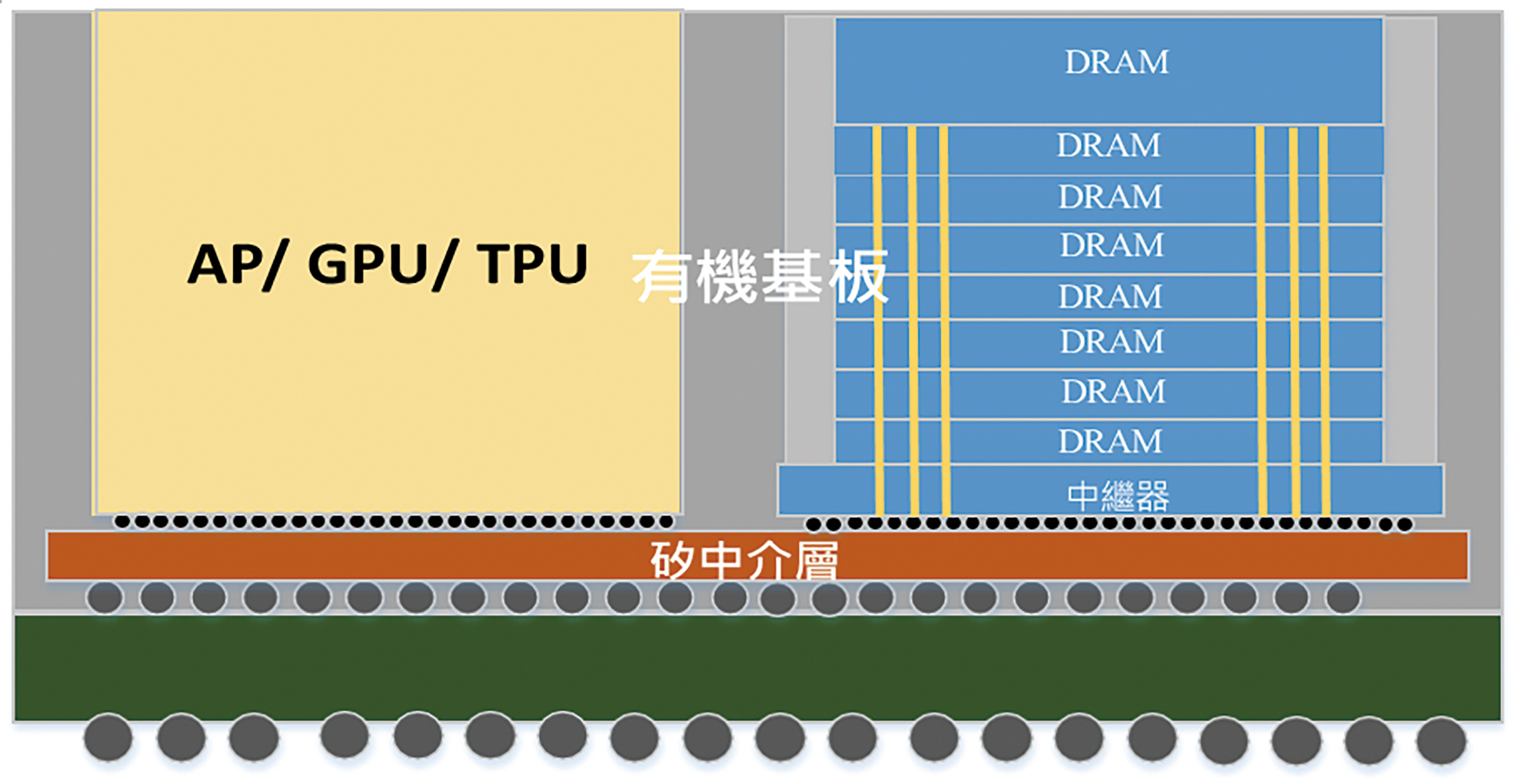

HBM2E以已知良好晶粒堆疊(KGSD)封裝。客戶需要請半導體外包封裝和測試夥伴廠商(OSAT),將他們的ASIC(系統單晶片SoC)與HBM2E予以整合(圖2),系統通常包含四至六個HBM2E DRAM。

圖2 HBM2E DRAMs系統級封裝(SiP)的範例

圖2 HBM2E DRAMs系統級封裝(SiP)的範例

如此緊密地整合,就是要讓整體記憶子系統(SoC與DRAM)的能效,比傳統DRAM加印刷電路板(PCB)的組合更高。當前技術PCB的訊號路徑把每個SoC的資料行限制在384或接腳(DQ)。訊號行如此受限,表1所列舉的GDDR6與GDDR6X若要達到更高的頻寬,唯一方法是增加每針傳輸速率。然而,這麼高的傳輸速率,缺點是SoC與DRAM之間傳輸資料時需要很多電力,因此需要晶粒內終端電阻(ODT)、高速輸入緩衝與時脈訊號(Clocking)、鎖延遲迴路(DLL)或相位閉鎖迴路(PLL)、時脈資料回復電路(CDR)等技術,並不停進行介面訓練與追蹤。

HBM2E高度整合的系統,優點是所有記憶體的流量都位於系統級封裝(SiP)當中。如矽中介層這類先進式封裝技術,能在非常低的每針傳輸速率(例如每針3.2Gbps)之下,使資料匯流排比分離式DRAM還寬(例如每個HBM2E裝置1,024個I/O行)。在相對較低的傳輸速率下,完全不需前段描述之複雜又耗電的技術。

除了能效明顯提升,HBM2E也帶來每SiP更高的容量,能源消耗卻十分地小。圖3為一般HBM2E DRAM SiP的切面,包含四個或八個記憶體晶粒。這四個或八個記憶體晶粒都相同,唯頂端晶粒的高度不同,因此兩種構造有相同的立方高度。事實上,立方高度與主機ASIC相符合,讓SiP能夠使用平面散熱裝置。

HBM2E當中的記憶體晶粒,與基底晶粒透過直通矽晶穿孔(TSV)垂直通訊。由每個HBM2E DRAM層總共約有5,000個TSV,用以連接訊號、供電、接地。

HBM2E DRAM焊接在矽中介層上,矽中介層以微小訊號線,將所有介面訊號匯流至主機ASIC。電源線與接地線通過矽中介層與封裝基板,匯流至SiP的封裝錫球(圖3)。

圖3 HBM2E組成之SiP的切面圖

圖3 HBM2E組成之SiP的切面圖

HBM2E獨立通道架構

接下來,分成三部分來說明HBM2E的獨立通道架構。

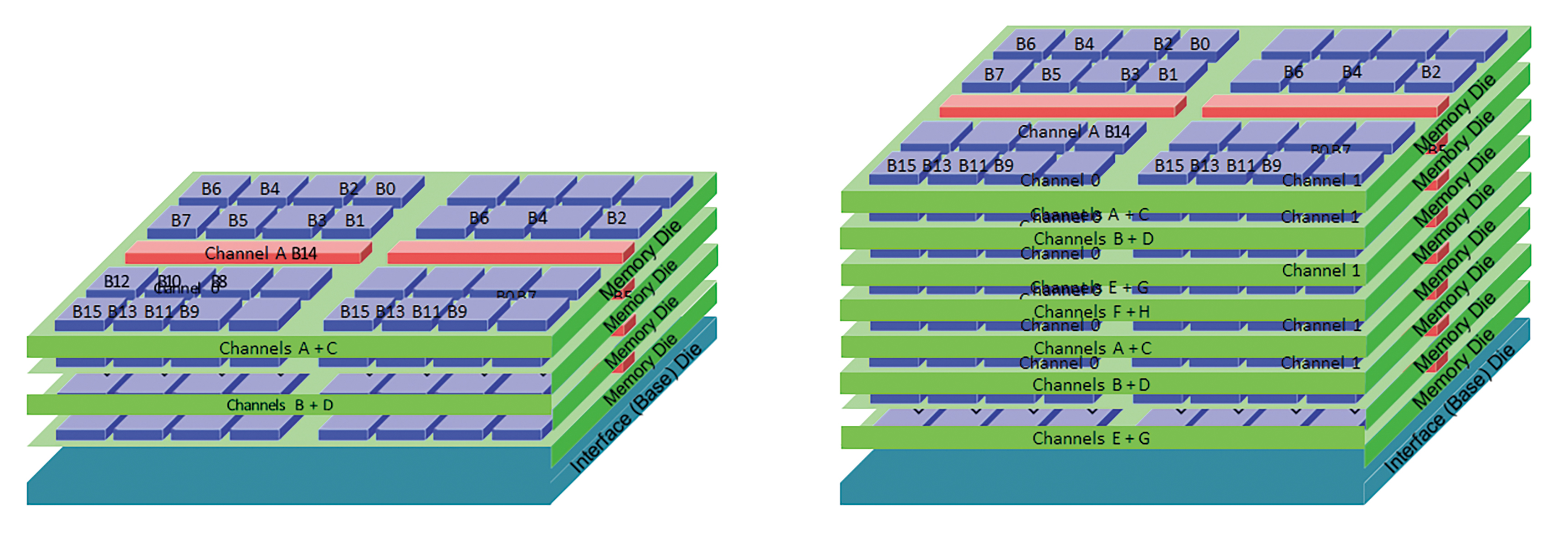

.通道架構

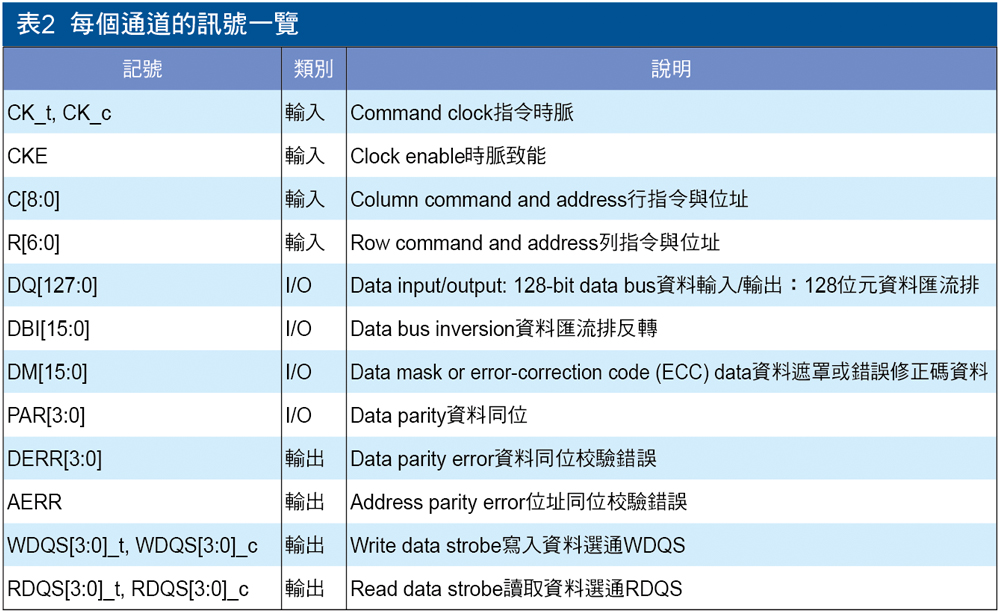

無論是Four-high還是Eight-high的DRAM配置,都是HBM2E DRAM內部由八個獨立通道A至H組成(圖4)。各通道都有自身的時脈(Clock)、指令/位址與資料介面,且可完全獨立於其他通道之外運作。每個通道的204個訊號統整於表2。請注意,Four-high與Eight-high兩種配置的通道數以及記憶頻寬相同,唯Eight-high配置每個通道的記憶容量加倍。這項通道概念可促進總記憶頻寬的有效使用。在諸多案例中,DRAM存取只有32或64位元組寬;分切內部記憶,可讓數個(例如8個)細粒度且獨立的記憶存取得以同步執行,進而大幅提升存取效率。

圖4 HBM2E通道組成範例

圖4 HBM2E通道組成範例

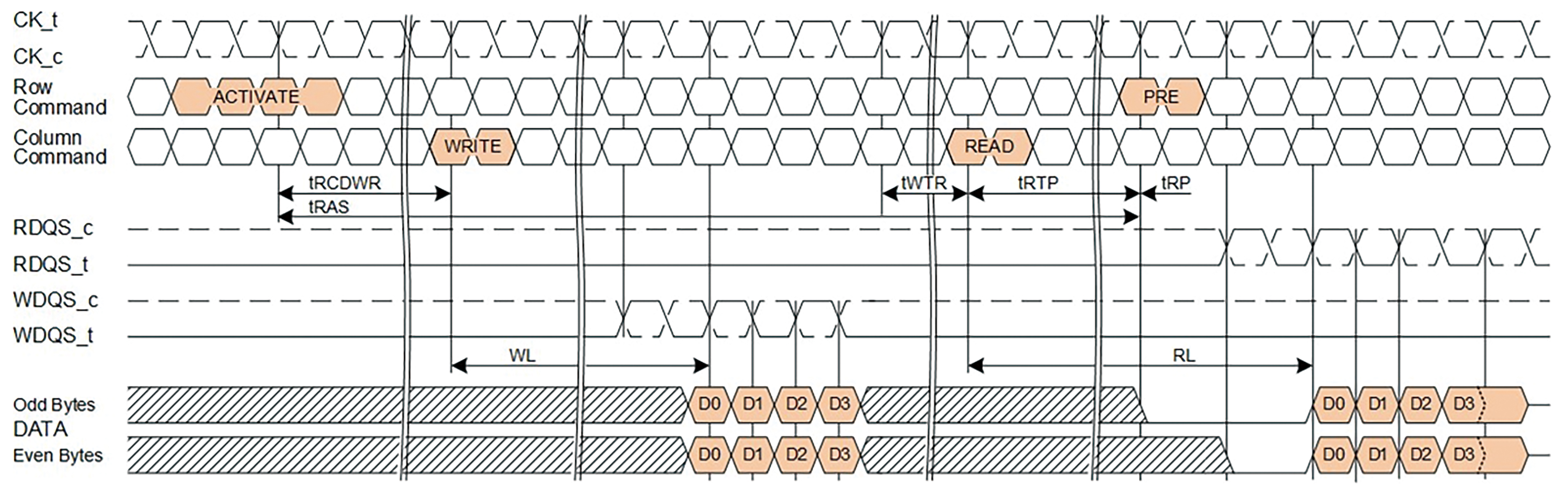

.假通道模式

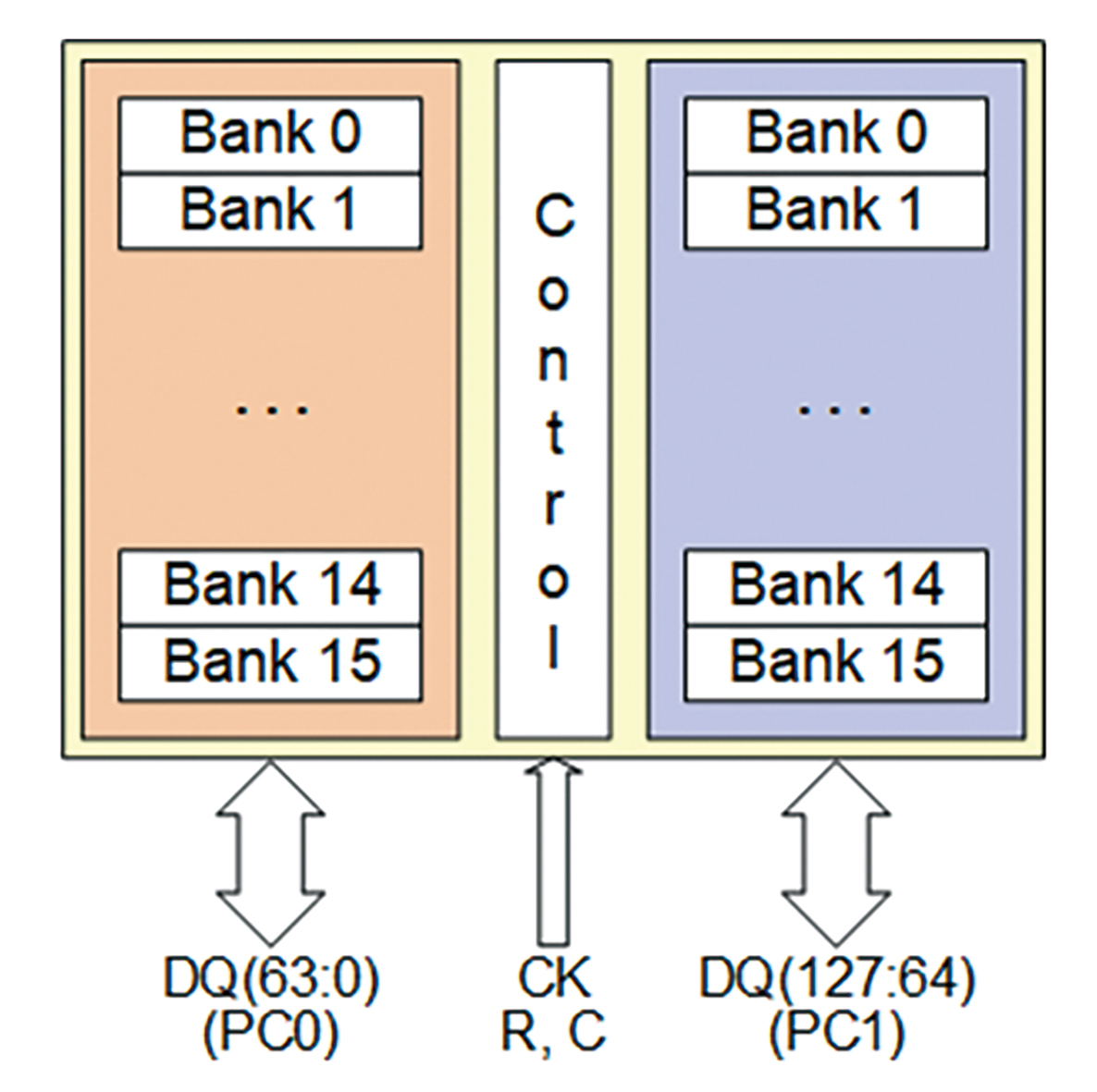

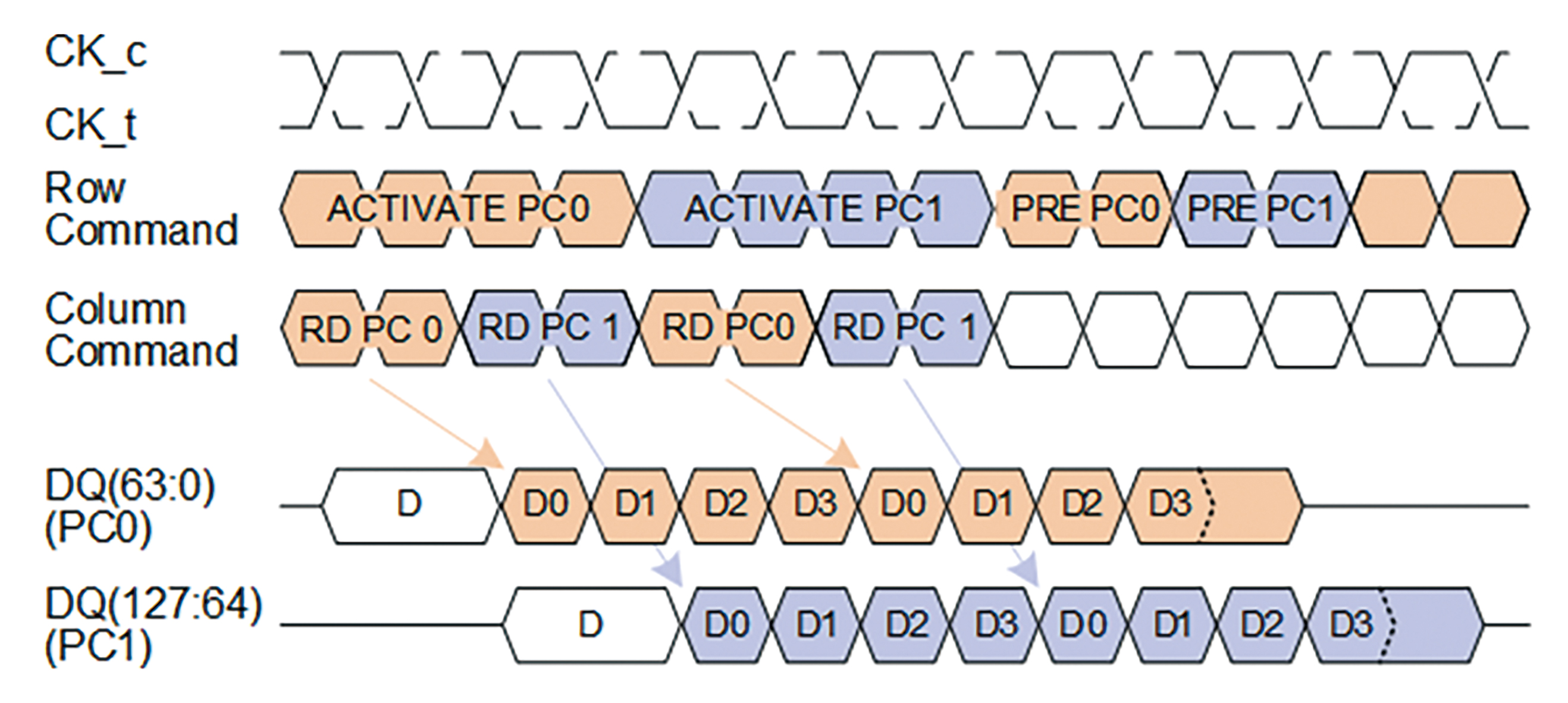

HB2ME DRAM八個通道各自細分為兩個半獨立運作的假通道(PC)。兩個假通道共用指令時脈(CK)、列(R)、行(C)的指令/位址輸入(圖5)。實際上,每個裝置因此等同有16個通道。指令編碼包括指定由哪個假通道(假通道0或假通道1)執行指令的1位元。各個寫入或讀取作業時間為兩個時脈週期,以突發傳輸(突發長度為4,即BL4)64個DQ的模式(假通道0為DQ[63.0]、假通道1為DQ[127:64]),傳輸共256位元的資料。BL4突發的四單位間隔以D0至D3表示。對應之寫入與讀取指令的長度為一個時脈週期。在假通道0與1之間由行指令匯流排交替發送讀取或寫入指令(圖6),能讓兩個假通道的運用率達100%。列啟動(Row Activation)與預充電(Precharge)作業可於列指令匯流排同步開始,不會影響讀取或寫入。

圖5 假通道模式架構(單一通道)

圖5 假通道模式架構(單一通道)

圖6 假通道模式的運作(單一通道)

圖6 假通道模式的運作(單一通道)

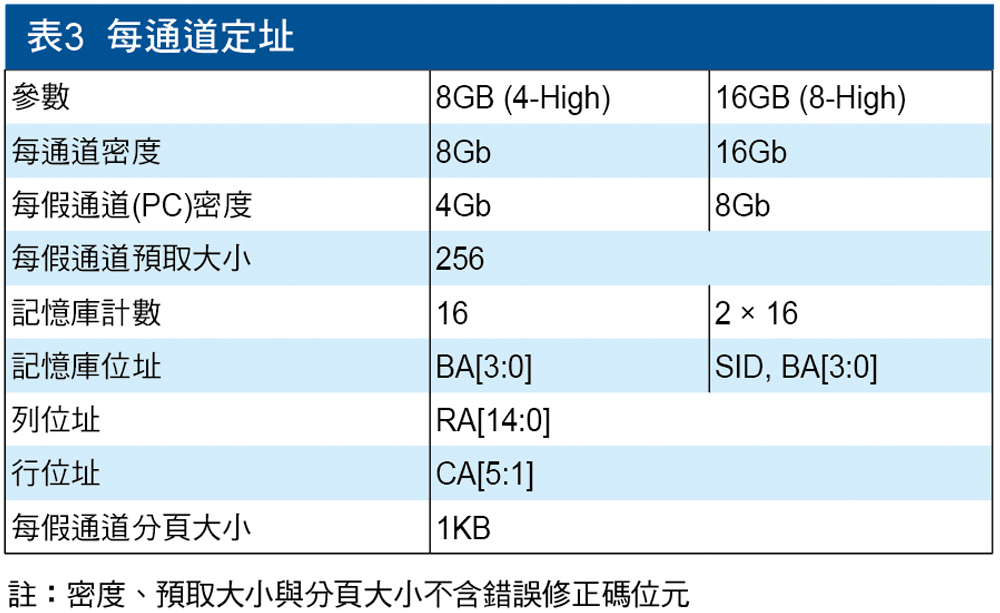

.定址

每通道定址參數列於表3。如圖4所示,Eight-high配置在每個通道都增加第二個記憶體晶粒,容量是Four-high配置的兩倍,定址方面反映在額外的Stack ID (SID)位元,作為第五個記憶庫(Bank)位址位元,並在上下記憶體晶粒之間選擇,因此也在上下16個記憶庫之間選擇。

HBM2E DRAM運作

緊接著,說明HBM2E DRAM如何運作。

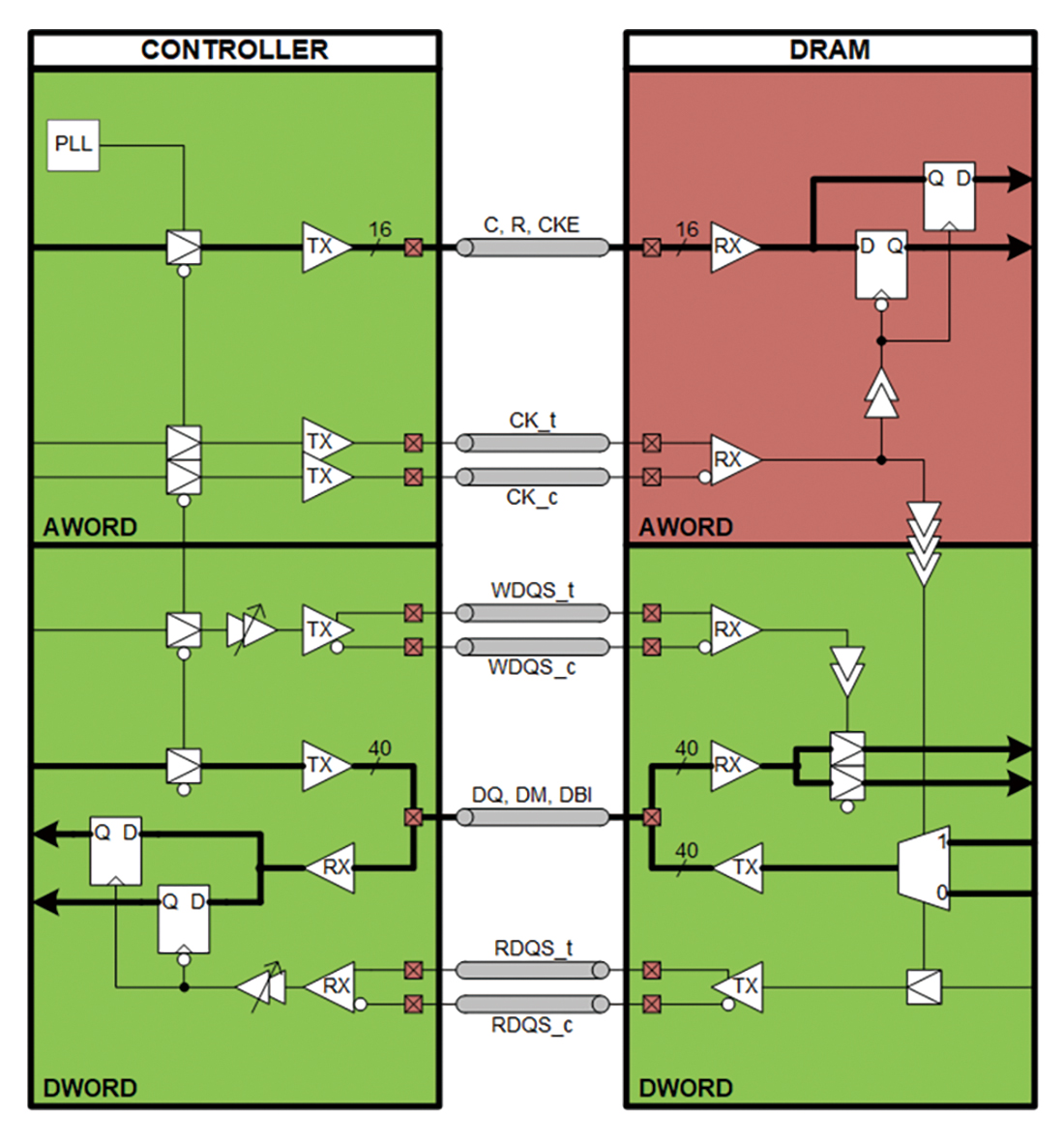

.時脈訊號

圖7顯示HBM2E DRAM系統的時脈系統,而表4則補充一般頻率與資料率,包括:1. 一個差動式時脈(CK_t、CK_c)鎖上指令與位址輸入(R, C, CKE);2. 寫入資料在對齊差動寫入資料選通的中心接收(WDQS_t, WDQS_c),一對WDQS選通搭配四位元組的資料;3. 讀取資料在對齊差動讀取資料選通的邊緣傳出(RDQS_t, RDQS_c),一對RDQS選通搭配四位元組的資料。這項時脈系統與DDR DRAM十分相似,唯此系統提供單向WDQS與RDQS,而DDR DRAM是雙向的資料選通(DQS)。此外,單向選通提供讀寫之間更快的匯流排周轉。像其他DRAM一樣,為降低運作能耗,沒有PLL或DLL與記憶介面關聯。HBM2E DRAM支援廣大的運作頻率範圍,從50MHz至最大額定時脈頻率,因此主機能夠有很大的範圍,可以調整時脈頻率,進而調整通道功率,以配合當前負載。

圖7 HBM2E DRAM的時脈訊號

圖7 HBM2E DRAM的時脈訊號

.發訊號

發訊號方面,HBM2E的介面使用一般Pull/Push驅動器,搭配可程式化驅動強度。通道訊號衰減明顯較大,收訊號端因此不需要終結器(Termination)。終結器的免除,是HBM2E DRAM能效良好的原因之一。

.寫入資料遮罩

HBM2E DRAM資料介面的資料遮罩(DM)引腳可配置為位元組寬粒度的寫入DM,或者配置為系統錯誤修正碼(ECC)額外的資料位元(詳見下文ECC介紹)。配置為DM支援的時候,若DM取樣為高(Sampled High),DQ輸入上收取的寫入資料則被忽略(遮蔽);若DM取樣為低(Sampled Low),寫入資料則寫進記憶陣列中。寫入資料遮罩,在多數DRAM裝置很常見。

.系統錯誤修正碼(ECC)

當ECC模式開啟,DM引腳則視為額外的資料I/O,形同每個資料位元組增加第九個位元。資料匯流排總寬度則為每通道144(128加上16)或者總寬1,152(1,024加上128)。此陣列為第九位元提供額外的記憶單元,有效總容量則為9GB(Four-high記憶體)以及18GB(Eight-high記憶體)。此外,這些ECC位元用途為系統校驗位元。在內部,它們被視為一般資料位元,可以在單一寫入或讀取指令中,有效地連同相關資料傳輸這些校驗位元。這裡強調一個重點:HBM2E DRAM並不會對ECC位元進行錯誤校驗,ECC位元不應與其他DRAM支援的On-die ECC功能混為一談。

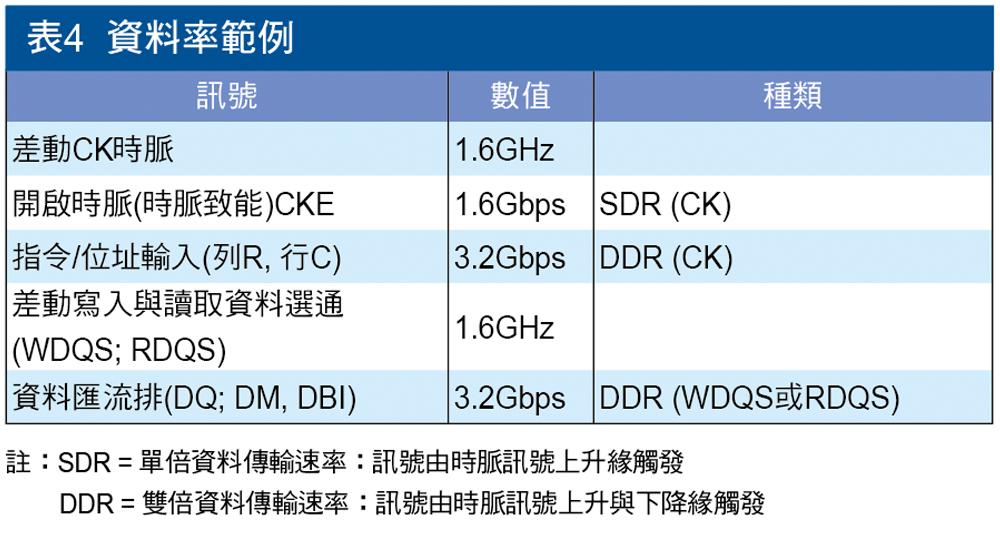

.資料匯流排反轉

HBM2E DRAM在讀寫作業中,支援一個位元組粒度的資料匯流排反轉編碼(DBIac)(圖8)。讀取與寫入的此功能,能夠單獨開啟或關閉。DBI功能的目的是減少主機ASIC與HBM2E之間外部資料線的資料切換率,進而減少整體能耗以及電源感應抖動(PSIJ)。資料匯流排反轉編碼DBIac為主機ASIC與DRAM對稱的功能,其運作方式為:傳輸器(例如讀取的HBM2E DRAM)計算從前一狀態轉換的DQ計數。當位元組內轉換的資料位元多於四個,或者位元組內轉換的資料位元數等於四個且DBI為高,傳輸器便反轉讀取資料並設DBI為高。否則,傳輸器不反轉讀取資料,並設DBI為低;若DBI取樣為高,接收器(例如寫入的HBM2E DRAM)便會將DQ收到的資料反轉,否則若DBI取樣為低,資料便不予反轉。

圖8 資料匯流排反轉編碼運算法

圖8 資料匯流排反轉編碼運算法

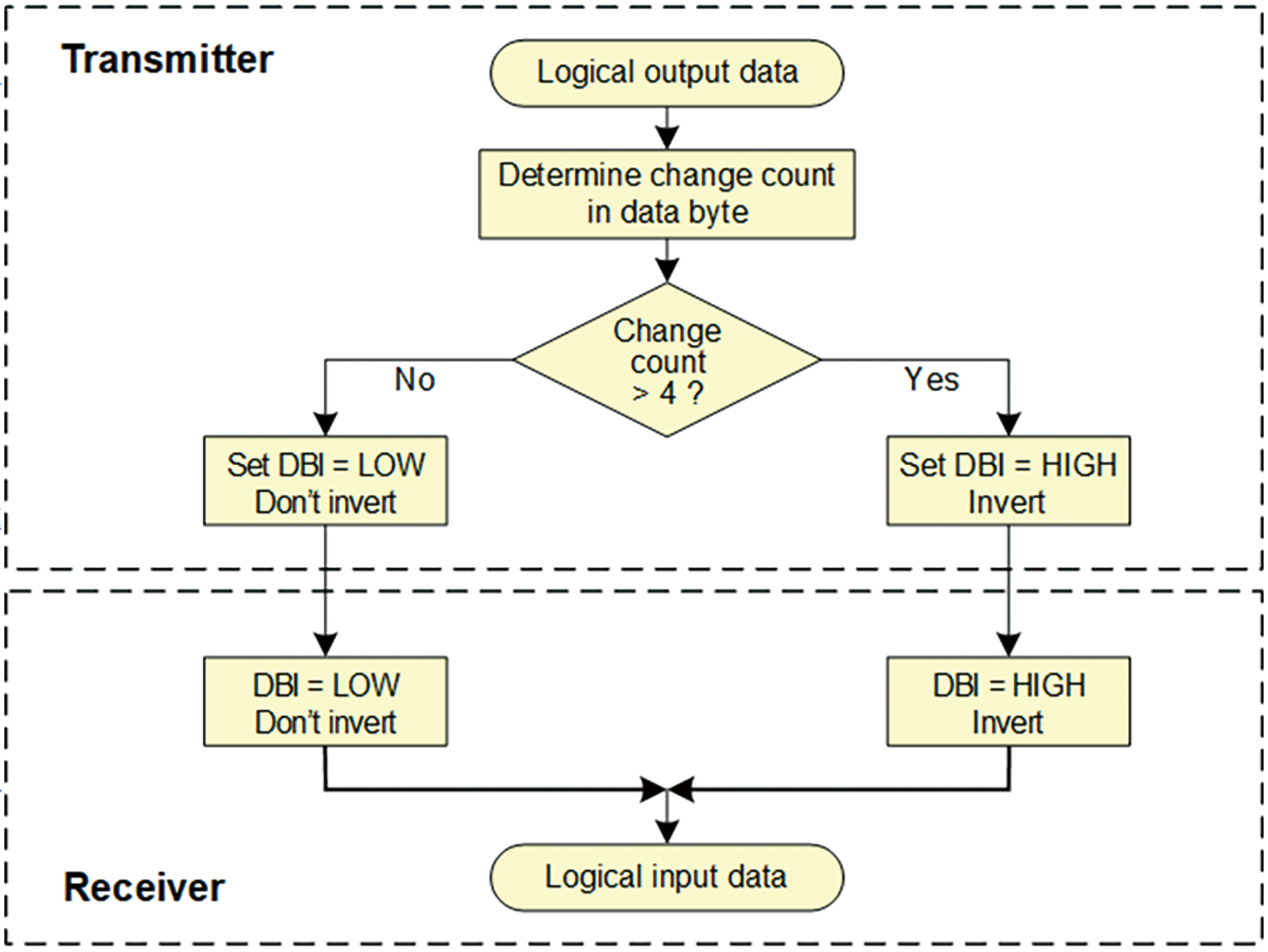

.基礎讀取與寫入作業

基礎讀寫作業如圖9所示,包含六個步驟:1.啟動(ACTIVATE)指令為後續讀取或寫入的存取開啟記憶庫中的一列,而記憶庫與列的位址連同ACTIVATE指令一併提供。須注意的是,ACTIVATE為雙循環指令,且在所需的位址位元都全部收到時,與寫入資料相關的列對行延遲(tRCDWR)會參照到第二個循環;2.在列對行延遲時序過後,即會發送寫入(WRITE)指令,而記憶庫與行的位址連同指令一併提供;3.在寫入延遲(Write Latency, WL)之後,寫入(WRITE)資料以突發模式(BL4,四個收取單位為D0至D3)收取。寫入資料鎖於寫入資料選通訊號(WDQS)的兩緣,且所提供之WDQS須對齊寫入資料的中心。寫入資料之前的額外前導WDQS脈衝確保WDQS訊號的波形符合實際鎖上的寫入資料;4.在寫入對讀取時序(tWTR)之後,會發送讀取(READ)指令,而記憶庫與行的位址連同指令一併提供;5.在讀取延遲(Read Latency, RL)後,讀取資料以突發模式(BL4,四個傳輸單位為D0至D3)傳輸。所傳輸的讀取資料選通訊號(RDQS)脈衝的兩緣對齊讀取資料的兩緣。讀取資料之前的額外前導RDQS脈衝,確保RDQS訊號的波形符合主機ASIC實際的寫入資料鎖閂;6.預充電(PRECHARGE)指令將開放的列予以關閉,且記憶庫位址與指令一同提供。一旦啟動對預充電延遲(tRAS)與讀取對預充電時序(tRTP)兩條件皆滿足,即發送預充電指令。在列預充電時間(tRP)過後,記憶庫可供下次列啟動使用。

圖9 基本的讀寫操作

圖9 基本的讀寫操作

.低功耗模式

HBM2E與許多其他DRAM一樣提供低功耗模式,可在應用程序暫時不需要存取DRAM時降低功耗:1.省電模式關閉指令解碼器和內部時脈。適合短時間無活動的情況。DRAM可瞬間恢復滿載運作,省電期間記憶體陣列不會充電更新(Not Refreshed);2.自更新是功耗最低的狀態,DRAM內部自行管理記憶體單元的更新,毋須記憶體控制器介入。

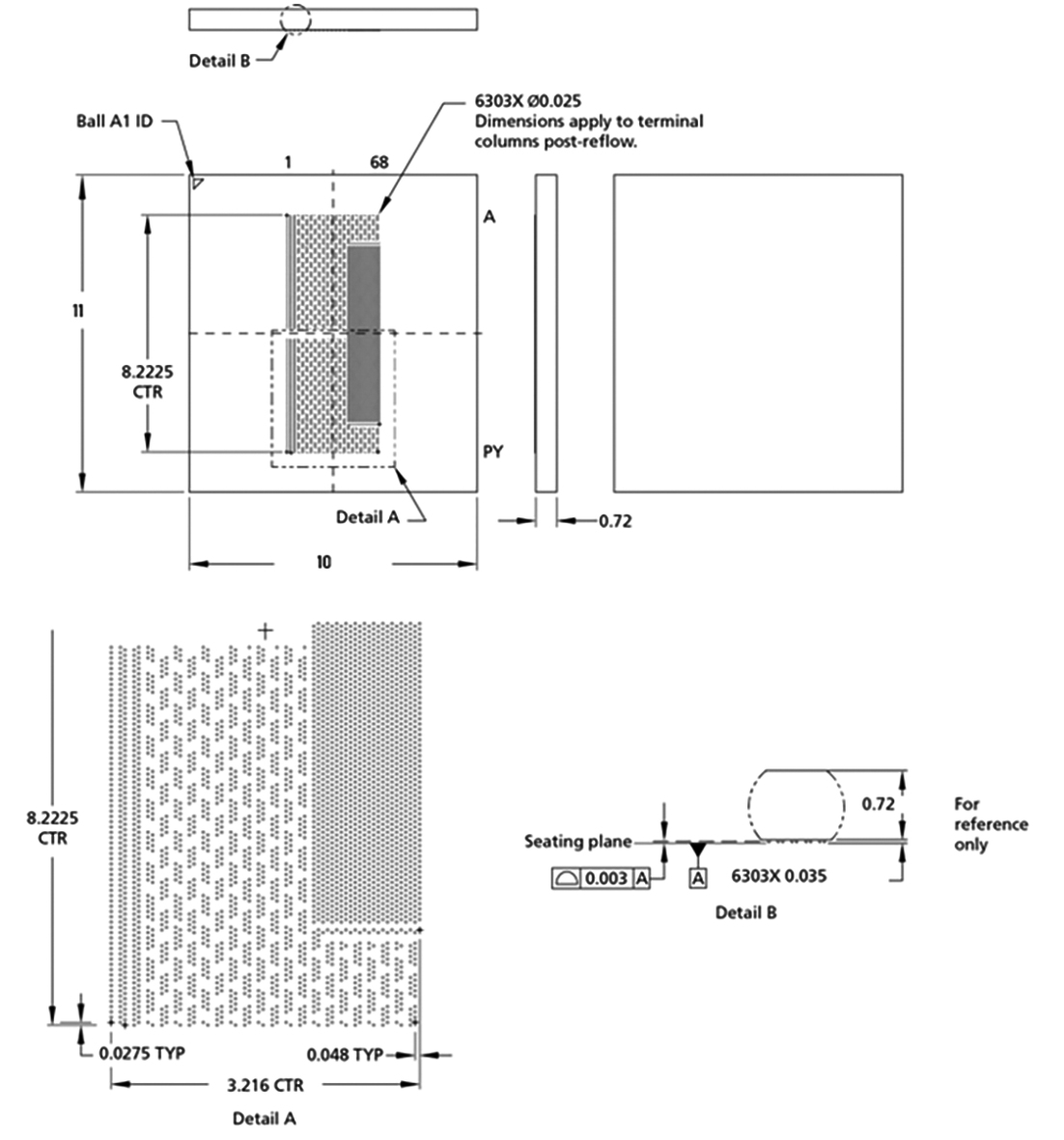

封裝尺寸和微凸塊矩陣

圖10為HBM2E DRAM的機械外觀,立方體尺寸為11毫米(mm)×10毫米(最大)。凸塊矩陣位於裝置中心,分成300行、68列,總共有6,303個微凸塊。凸塊採交錯(對角)排列,對角線間距約為55微米(μm),相較於相同凸塊間距但採正交排列的情況,對角排列的凸塊直徑可以更大。 所有I/O凸塊都放在凸塊矩陣右側高密度的實體層(PHY)區。主機端PHY區應為DRAM端PHY矩陣的副本,可允許所有訊號線以相同的走線長度平行布線在中介層上。凸塊矩陣的位置,請見圖1。

圖10 Micron HBM2E機械外觀

圖10 Micron HBM2E機械外觀

PHY區的細部圖示,如圖11所示。電源和接地電源凸塊放置在I/O訊號之間,但也分布在整個凸塊矩陣中,以便為裝置提供可靠的電源。此圖也顯示了I/O區域外的凸塊矩陣間隙。這些間隙可供DRAM供應商放置測試裝置用的探針卡(Probe Pad)。

圖11 HBM2E PHY區域

圖11 HBM2E PHY區域

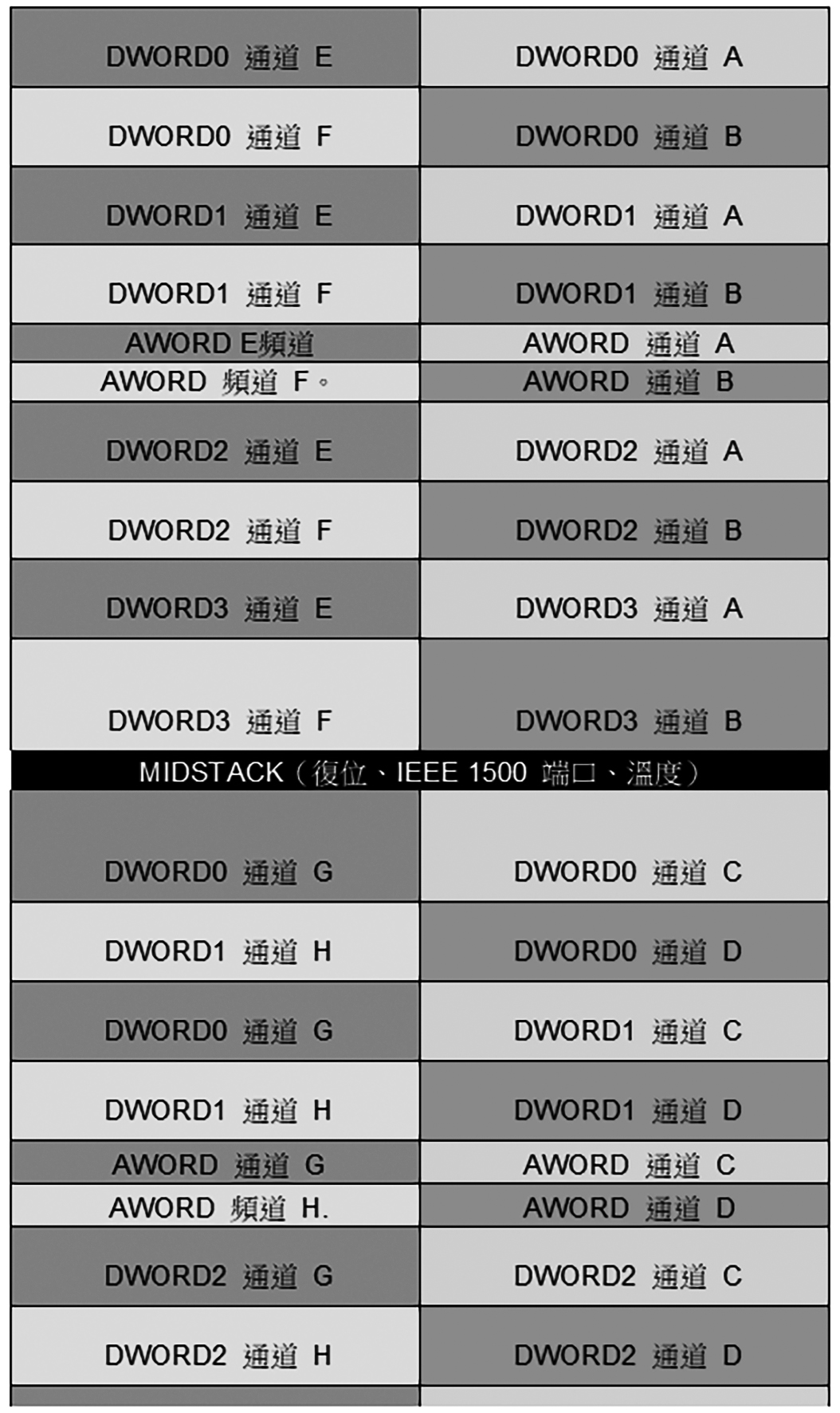

PHY區的訊號凸塊分為AWORD和DWORD兩組。其中,通道的所有指令和地址輸入以及CK時脈都位於AWORD內。而所有數據I/O,包括WDQS和RDQS,都位於DWORD中。一個通道包含四個DWORD,每個DWORD包含32個DQ,外加一對WDQS和RDQS。另外,MIDSTACK區中的訊號對所有通道都是通用的。其中包括晶片重設、溫度報告訊號和IEEE 1500測試端口。

圖11的顏色代碼說明了PHY區域內八個通道的位置。通道A、B、E和F位於中央所謂的MIDSTACK區域上方,而通道C、D、G和H位於其下方;四個通道都放置在一個2×2矩陣中,AWORD位於中心,兩個DWORD位於上方,其他2個DWORD位於AWORD下方;對稱和交錯的配置,可對應至如圖4中HBM2E堆疊中通道的垂直分布。

測試和除錯功能

HBM2E DRAM配備強大的測試、修復和除錯功能。HBM2E組裝於SiP後,這些功能有助於驗證HBM2E DRAM的內部運作以及與主機ASIC的連接。組裝後若檢測到故障,亦能提供修復裝置的方法。

這些測試和修復功能之部署,是提升組裝良率的重要因素。為說明其重要性,試比較SiP中的HBM2E總成與PCB或雙行記憶體模組(DIMM)上,傳統的離散DRAM組件(或任何其他組件)總成。回焊後若發現焊點有問題,「重做」程序就會啟動:移除有問題之元件、清潔PCB表面、焊接替代組件。

HBM2E的矽中介層上,無法進行此「重做」程序。既然沒有片上修復功能,主機ASIC或DRAM端只要有一個焊點發生故障,不僅得丟棄有缺陷的HBM2E DRAM,還須報廢整個含有主機ASIC和若干HBM2E DRAM之SiP。

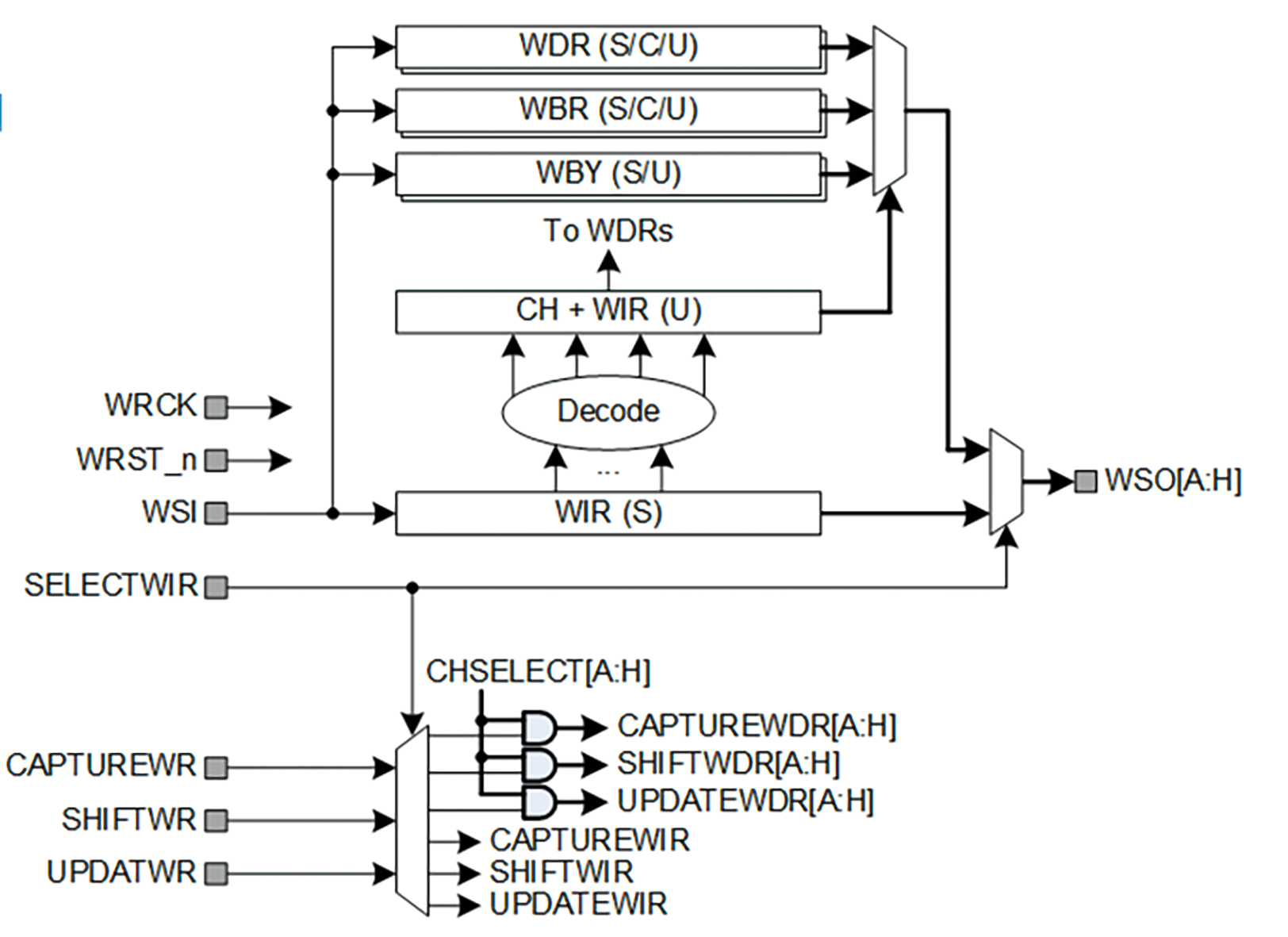

IEEE 1500測試端口

HBM2E DRAM中所有測試和修復功能,皆由符合IEEE 1500標準之測試端口所控制。IEEE 1500測試端口的概念源自IEEE 1149.1邊界掃描標準,針對更大系統內建的巨集指令進行檢測。中央控制(測試存取端口,亦即Test Access Port,簡稱TAP)位於主機ASIC內。HBM2E DRAM接收預先解碼之控制訊號,依訊號將數據(SHIFTWR)串列移入和串列移出、獲取內部狀態(CAPTUREWR),並使用新數據更新內部狀態(UPDATEWR)

如圖12所示,相關的訊號凸塊位於凸塊矩陣的MIDSTACK區中,且對所有通道皆通用。測試亦能提供以下功能:1.指令暫存器(WIR)可串列加載特定測試指令。指令代碼內含若干位元,決定該指令應由所有通道執行,抑或是僅由單一通道執行。圖中下半部分的AND閘,決定未獲選通道內,獲取、移位和更新訊號之開關;2.旁路暫存器(WBY)由一個單步移位暫存器組成;3.邊界掃描暫存器(WBR)執行邊界掃描測試(如下所述);4.若干數據暫存器(WDR)支援內部測試和修復(如下所述)。

圖12 IEEE 1500測試端口

圖12 IEEE 1500測試端口

HBM2E DRAM的測試端口為IEEE 1500標準的特殊實踐,為各通道提供專用的串列輸出(WSO),允許主機ASIC並列獲取各通道的測試結果,進而減少整體測試時間。

邊界掃描

數十年來,邊界掃描是業界廣用的測試功能,藉由標準化的測試介面驗證組件之間的連結。邊界掃描之細節列於IEEE標準1149.1。 HBM2E DRAM的邊界掃描指令允許在不運行DRAM核心的情況下,測試主機ASIC和DRAM之間的互連。0和1的邏輯數據在發送端(主機ASIC或DRAM)串列移入,接收到的數據被鎖存,而後在接收端串列移出。

回路測試模式

雖然邊界掃描測試足以偵測靜態(硬)故障,但唯有介面以目標速度運作時,才可能檢測到其他與介面相關的故障。為此,HBM2E DRAM支援回路測試模式;回路測試使用I/O電路而非記憶體陣列。

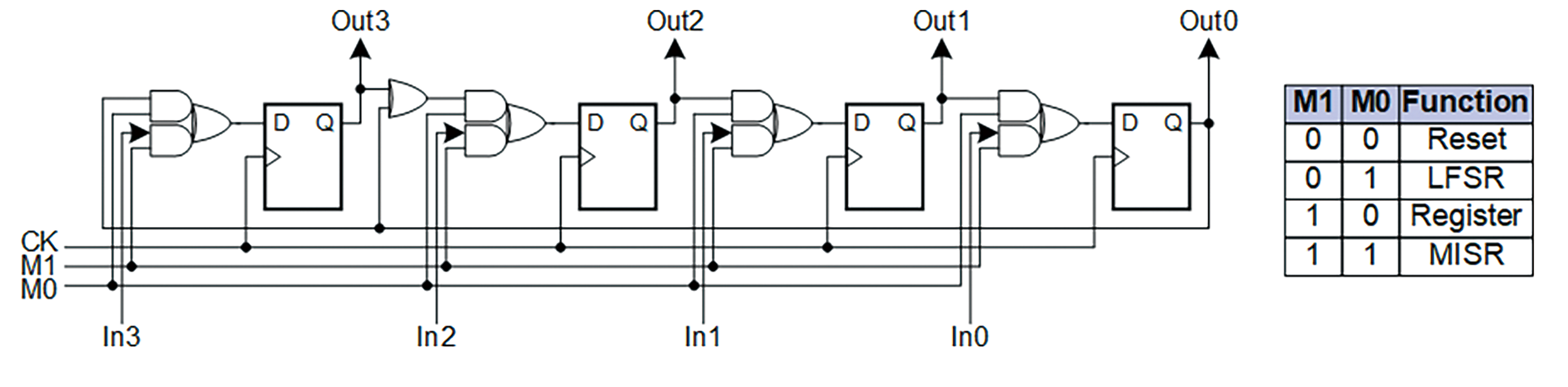

回路測試模式使用任務模式介面的主I/O數據鎖存器,但允許將鎖存器設置為線性回饋移位暫存器(LFSR)或多重輸入移位暫存器(MSIR),如圖13所示。

圖13 線性回饋移位暫存器(LFSR)和多重輸入移位暫存器(MISR)

圖13 線性回饋移位暫存器(LFSR)和多重輸入移位暫存器(MISR)

回路測試模式的運作方式,說明如下:

LFSR模式用於測試讀取方向。LFSR首先使用起始值(種子)進行初始化,接著產生一個偽隨機模式序列,並依循與正常讀取相同的協定和時序,將該序列與READ指令一起傳輸(圖9)。LFSR使用的多項式是標準化的,因此主機ASIC可計算預期讀取數據,並在每個週期與接收到的數據進行比較。

MISR模式用於測試寫入方向。MISR亦使用起始值(種子)進行初始化。然後,主機ASIC發出一個或多個WRITE指令,並依循與正常寫入相同的協定和時序,發送隨機寫入數據(再次參見圖9)。MISR將寫入數據壓縮為簽章,然後透過後續的READ指令或IEEE 1500測試端口回讀該簽章,並與預先算好的預期簽章進行比較。

MISR模式協助檢測多個寫入週期內是否有任何數據位元發生故障,但無法檢測單個DQ通道的故障。為此必須使用第三個測試功能:LFSR比較模式。在此模式下,LFSR用於計算預期寫入數據。隨著每個WRITE指令,主機透過LFSR,以相同的多項式生成寫入數據。HBM2E DRAM將接收到的數據與LFSR提供的預期寫入數據進行比較。若兩者不匹配,則設置一個與各DQ有關的內部位元(粘滯錯誤旗標,Sticky Error Flag)。測試結束後,所有錯誤位元皆可透過IEEE 1500測試端口讀取以進行檢查。

此外,指令/位址介面亦支援MISR和LFSR比較模式。

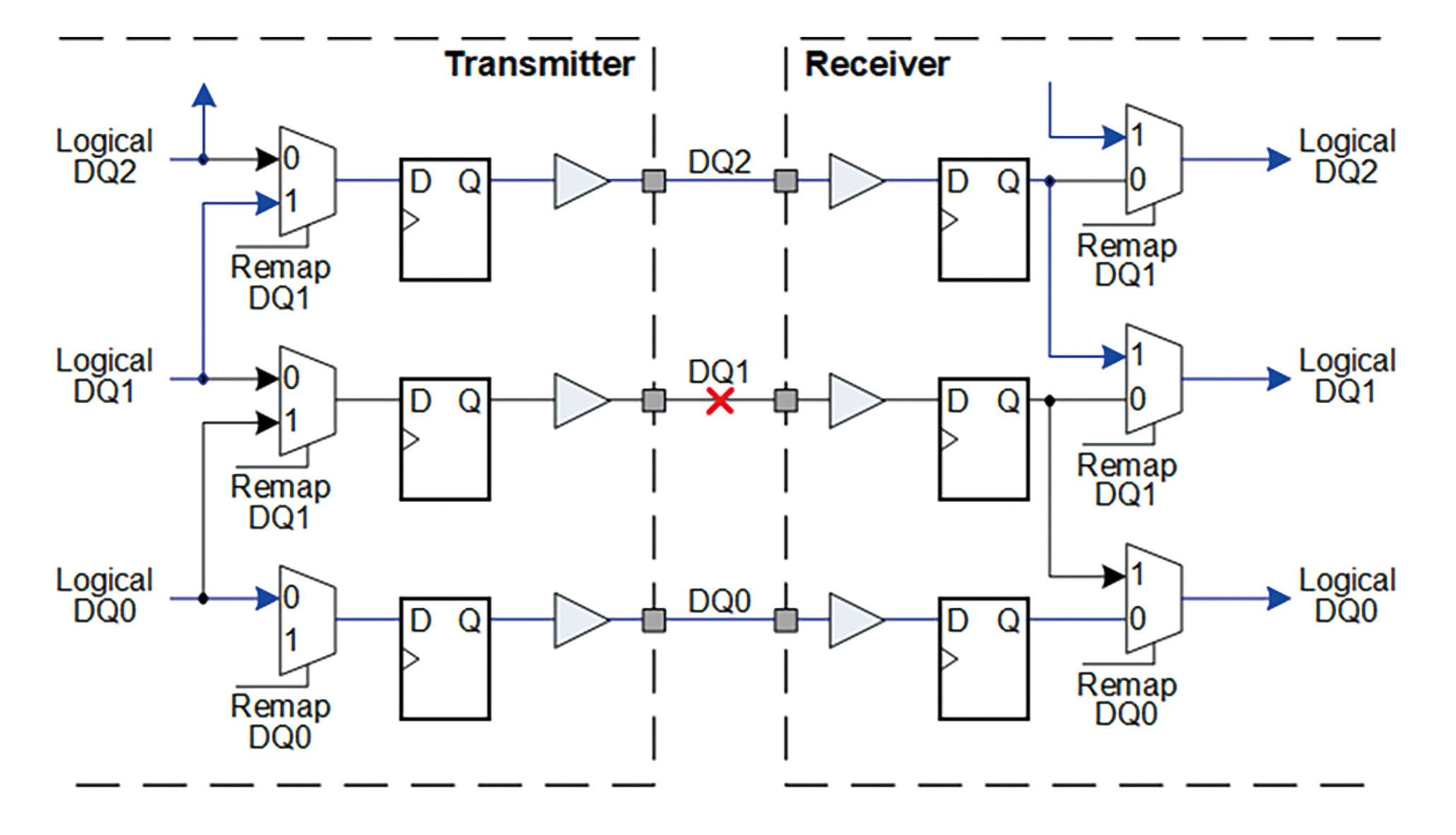

.互連冗餘重映射(通道修復)

邊界掃描或回路測試模式若檢測到與互連有關的故障,主機則可啟動修復損壞通道的程序。HBM2E DRAM支援互連通道重映射,以在主機ASIC和DRAM之間的訊號連接斷開或因故失能時恢復功能。凸塊矩陣含有少量的冗餘或備援I/O,這些I/O通常處於關閉狀態,僅在修復斷連時才啟動。每個指令/位址輸入行(R)和列(C)各有一個冗餘輸入,而每個數據位元組(如果必須保留DBI功能,則為每兩個數據位元組)皆有一個冗餘I/O。圖14為通道修復示例。請注意,任何通道修復的編程,在主機ASIC和DRAM端皆應相同。此示例中,DQ0通道完好無損,正常發送和接收DQ0邏輯數據,但DQ1通道損壞;DQ1邏輯數據在發送端重映射至DQ2輸出鎖存器和驅動器,透過DQ2通道發送和接收,並於輸入鎖存器後的接收端映射回Logical DQ1。其他DQ亦對相鄰的I/O與通道進行同樣的重映射。最後一個DQ則重映射到備援I/O和通道。此方案下,重映射僅發生在互連級別,不影響裝置的邏輯運作。除此之外,通道修復透過IEEE 1500測試端口進行編程,可執行臨時(揮發性)重映射以驗證修復成果(軟通道修復),抑或熔斷保險絲,使此重映射成為永久配置(硬通道修復)。

圖14 通道修復示例

圖14 通道修復示例

.記憶體陣列測試與修復

HBM2E DRAM內建一個精密、高度可程式的引擎,用於測試記憶體陣列(MBIST)。MBIST的測試範圍與美光在HBM2E DRAM成品出貨前所做的測試類似。客戶及客戶的生態系能運用MBIST,在成品組裝後、出貨給終端客戶之前,對記憶體陣列進行徹底測試。MBIST透過IEEE 1500測試端口進行控制,並於完成後提供測試結果。若MBIST檢測到故障,主機可針對故障單元啟動修復程序。為此,記憶體陣列配有備援行,且可透過IEEE 1500測試端口啟動。與通道修復相同,MBIST可執行臨時(揮發性)修復,以驗證修復成果(軟修復),抑或熔斷保險絲,使該修復成為永久配置(硬修復)。

.IEEE 1500測試端口的其餘功能

操作HBM2E DRAM時,IEEE 1500測試端口尚有更多功能:1.裝置ID功能向主機提供若干類型的寫死數據,例如密度、製造商代碼、元件編號和獨特序號。主機可在啟動時讀取這些數據,並根據此資訊配置HBM2E DRAM,或將這些數據用於追蹤;2.溫度功能報告DRAM的接面溫度,讓主機確定裝置是否在允許的溫度範圍內安全運作。溫度讀取使用的是IEEE 1500測試端口,故可頻繁執行而不影響頻寬;3.模式寄存器轉儲/設置功能,負責配置HBM2E DRAM的可程式特性,但更重要的是,此功能可讀回編程值(例如用於除錯)。

(本文作者為台灣美光先進封裝技術開發處副總裁)