早期全球衛星定位系統(Global Positioning System, GPS)接收機主要應用在可攜式導航裝置(Personal Navigation Device, PND)。過去這幾年來,PND平均銷售價格(Average Sale Price, ASP)降低,進一步刺激導航裝置的市場,也造就了從2004年至2007年PND市場的榮景。但從2008年開始,PND的市場已經有所改變,過往幾年倍速成長的時代已經不存在。

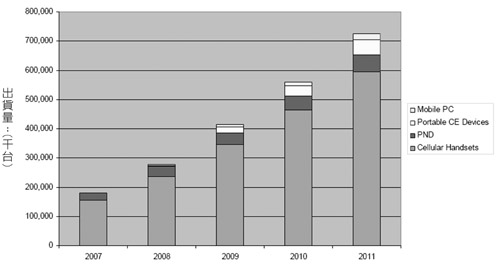

隨著GPS接收機性能的提升和耗電量逐漸降低,使得內建GPS接收機的手機越來越普及,甚至可被視為威脅低階PND的殺手產品。對低度和中度的導航用戶而言,利用手機內建的GPS接收機、導航引擎(Navigation Engine)和圖資來提供基本的導航便已經足夠;在高階和專業的導航應用方面,PND仍會是此一市場的主流,但隨著越來越多的汽車內建車載導航系統也導致PND的市場日漸萎縮。圖1為In-Stat在2007年12月針對GPS系統出貨量的預測。

|

資料來源:In-stat (12/2007)

圖1 2007~2011年全球GPS系統出貨量預估 |

從圖1可以發現2008~2011年GPS晶片在PND市場的出貨量幾乎是零成長,反觀在手機市場的出貨量卻是顯著攀升。

GPS接收機和手機單晶片整合時,有許多問題必須加以考量,例如耗電量、硬體成本和手機電路對GPS接收機的干擾等,其中耗電量是最主要的考量點之一。

三大類GPS架構各有千秋

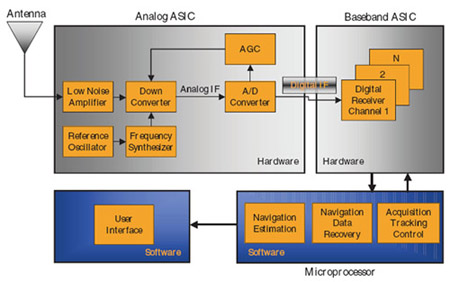

圖2為今日大多數獨立式GPS接收機的架構,是由天線、射頻前端(RF Front-end)、類比IC(包含射頻和類比基頻)、參考頻率源(Reference Clock)和基頻IC所組成。射頻前級和類比IC都屬於類比部分,目前仍無法由數位訊號處理和軟體所取代,但基頻IC卻可以完全由軟體來取代,此種架構稱為軟體GPS(Software GPS)解決方案。若將部分的數位硬體(主要是相關器和周邊介面)和控制電路從基頻IC移至類比IC,而其他基頻硬體完全由軟體來取代,此架構稱為半軟體式或主機式(Host-based)GPS。

|

| 圖2 傳統獨立式GPS接收機架構圖 |

傳統GPS接收機的基頻IC內的數位硬體主要是由大量的平行相關器(Correlator)所組成的頻道(Channel)。數位中頻或基頻的GPS訊號經過硬體所組成的頻道進行相關性的運算和積分後再將結果傳送至由軟體控制的微處理器進行位置的解算。另外,可程式化的微處理器也負責控制C/A碼的擷取和追蹤迴路。傳統GPS接收機的基頻IC主要是由數位硬體(量測引擎)、微處理器、周邊介面電路(例如UART、SPI)和記憶體所組成。其中記憶體可以是快閃(Flash)記憶體或低價位的唯獨記憶體(ROM)。記憶體是利用堆疊(Stack)的方式和基頻晶片封裝成同一顆封裝。GPS接收機和手機系統的整合以往還是以獨立式GPS接收機為主流,主要是因為獨立式GPS接收機不須要在主機中央處理器(CPU)上進行複雜的軟體整合(一般只須用到UART介面)。

硬體式GPS接收機在基頻的部分是由量測引擎(Measurement Engine)和位置引擎(Position Engine)所組成。量測引擎主要是由數位硬體和控制這些硬體的軟體所構成,而位置引擎主要是跑在微處理器上的導航軟體。量測引擎主要是負責C/A碼的擷取和追蹤,而位置引擎主要是負責導航資料位元的解碼、偽距離(Pseudorange)和位置/速度/時間(PVT)的解算。

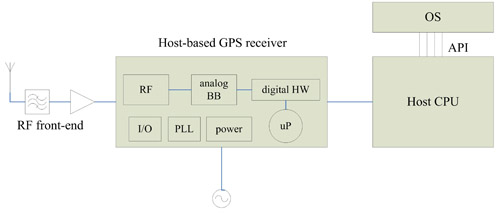

主機式GPS接收機實際上和獨立式的GPS接收機非常相似,唯一的差別在於主機式架構會將原本在基頻IC的數位硬體和量測引擎的控制區塊(軟體)搬移至類比IC。一般都是利用一個簡單的微處理器或數位訊號處理器(DSP)來執行量測引擎的控制和部分位置引擎的功能。至於哪些軟體區塊應該被搬到類比IC的微處理器上,不同的GPS晶片設計公司會有不同的作法,但只要是須做即時性(Realtime)訊號處理的區塊,都應該被放置在類比IC中,以避免因為主機CPU被其他任務中斷(Interrupt)時所產生的時間延遲(Latency)。原來在基頻IC內的微處理器(例如ARM7 TDMI)則是由主機的CPU所取代,利用此種切割方式可以省下一顆微處理器的成本。另外,用來儲存系統資訊如星曆(Ephemeris/Almanac)、頻率位移、位置資訊等的記憶體也可以省略,系統資訊將會被存放在主機的記憶體中。利用混合訊號RF CMOS技術可以將射頻電路、類比基頻電路、數位硬體和微處理器製作成單晶片,並利用先進製程(例如65奈米)進一步降低功率消耗、晶片成本和面積。圖3為主機式GPS接收機的架構圖。

|

| 圖3 主機式GPS接收機架構圖 |

數位硬體主要是由頻道所組成,頻道的數目也決定了硬體的複雜度和功耗。不同的解決方案會有不同的頻道數配置,目前主流頻道數為十六個頻道。每個頻道又由數值控制振盪器(Numerically Controlled Oscillator, NCO)、相關器、緩衝記憶體、與虛擬隨機噪聲(PRN)碼產生器等次系統所組成。

NCO主要是用來補償衛星因為都卜勒效應所導致的頻率和相位的變化,以及觸發相關性的運算和量測;相關器的功用則在於對C/A碼空間進行匹配動作。目前GPS接收機在每一個頻道都會配置大量的平行相關器,以一次匹配整個C/A碼空間;緩衝記憶體多半使用隨機存取記憶體(RAM),用來存放數位的I/Q資料和解相關運算之後的結果;PRN碼產生器則是用來填入系統所要擷取的衛星的C/A碼,基本上是由主機CPU來控制此一次系統。值得注意的是,目前大部分的GPS接收機皆支援星基增強系統(Satellite Based Augmentation System, SBAS),如美國的廣域增強系統(WAAS)、歐洲的同步衛星導航覆蓋服務(EGNOS)和日本的MTSAT衛星增加系統(MSAS)。因此PRN碼的產生器除了產生GPS的C/A碼之外,也必須能夠產生所支援的SBAS的PRN碼。表1為SBAS的PRN碼對照表。

| 表1 SBAS系統PRN碼對照表 |

| SBAS |

Geostationary |

PRN |

NMEA SVID |

| WAAS |

Anik |

138 |

51 |

| PanAm |

135 |

48 |

| EGNOS |

AOR-E |

120 |

33 |

| Artemis |

124 |

37 |

| IOR-W |

126 |

39 |

| IOR-E |

131 |

44 |

| MSAS |

MTSAT-1 |

129 |

42 |

| MTSAT-2 |

137 |

50 |

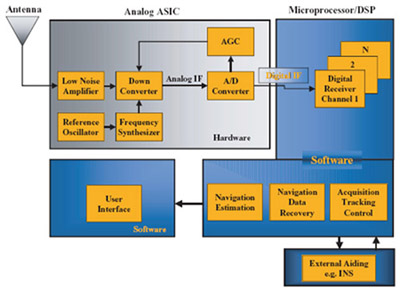

軟體式GPS接收機將所有數位訊號處理的工作利用主機的微處理器或DSP來完成,因此可以省略數位硬體和GPS專屬微處理器的費用。在軟體GPS接收機中,類比和數位的界線就是類比數位轉換器(ADC)。GPS訊號經過射頻前級和類比訊號條件處理之後利用ADC轉換成數位訊號後,再利用主機的DSP或CPU進行數位訊號處理和位置的解算。圖4為一般軟體GPS接收機的架構圖。

|

| 圖4 軟體GPS接收機架構圖 |

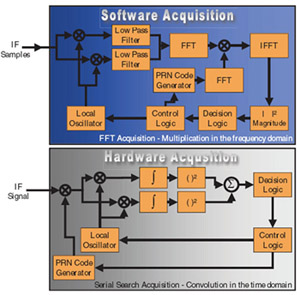

在軟體GPS接收機中,GPS衛星訊號的擷取一般都是採用快速傅立葉轉換(Fast Fourier Transform, FFT)。硬體式的GPS是在時域(Time Domain)上進行訊號處理而軟體GPS接收機利用FFT將訊號從時域轉換成頻域(Frequency Domain)。圖5為硬體GPS接收機和軟體GPS接收機擷取衛星訊號的區塊圖。

|

| 圖5 硬體式和軟體式GPS接收機衛星訊號擷取區塊圖 |

由圖5可見,硬體式GPS接收機是在時域上面利用迴旋積分(Convolution)的方式來對位(C/A碼匹配),而軟體式的GPS接收機是利用FFT將時域上的摺積(數位序列的摺積就是XOR的運算)轉換成頻域上的相乘。

軟硬體實作利弊不同

GPS的基頻訊號處理既是數位(多位元)訊號處理,當然可透過純軟體的方式在CPU上執行,以省略相關器這種特殊應用積體電路(ASIC)。由於所有的GPS訊號都隱身在相同的訊號中,因此記錄一段訊號也就記錄了所有衛星訊號。對於不同衛星的搜尋鎖碼便可以利用此段訊號。

在軟體GPS接收機中訊號的擷取經常都是採用FFT的方法,在訊號搜尋的期間內接收機必須搜尋所有可能的頻帶(頻寬由衛星的都卜勒頻率所決定)和碼空間來匹配中頻的接收訊號。利用FFT在頻域進行大量的平行相關的搜尋比起傳統的硬體法在時域上採用循序式的搜尋要來得有效率,這主要是因為利用軟體的方式進行訊號的擷取只須記錄一段時間的原始中頻資料(Raw IF Data)即可。GPS衛星訊號的擷取並不需要即時性和連續性的運算,因此立體接收機可以在訊號擷取的階段利用所謂的快照(Snap shot)的模式記錄一段原始資料並將之存放於緩衝記憶體(一般為RAM)中在利用FFT的數學運算將該原始資料轉換成頻域進行匹配。

在GPS訊號的追蹤上面,硬體法比起軟體法要來得有效率。GPS訊號的追蹤是一個持續性的過程,因此軟體接收機的CPU會有固定的每秒百萬指令集(MIPS)消耗,進而消耗比較高的功率。這意味著軟體接收機在需要持續性定位輸出的應用上面比較不利,但是在間歇性定位輸出的應用,例如定時定位(Push-to-fix)上比硬體法較有效率。另外軟體接收機特別適合於事後處理(Post-processing)的應用,利如使用在數位相機上的地理標記相片(Geotagging Photo),若使用硬體接收機,系統需要一段不算短的時間來定位(當在惡劣環境時所需的時間更久);若利用軟體接收機,則可以使用事後處理的方式將所記錄的一小段(數百毫秒)時間利用事後處理的方式計算出位置資訊。

以晶片的單價而言,獨立式GPS最貴、主機式GPS次之、軟體式GPS的成本則最為低廉。但以對主CPU的MIPS的消耗與軟體整合的複雜度而言,軟體式GPS的效能需求與複雜度最高、主機式GPS次之、獨立式GPS最低。一般而言,較高的CPU MIPS消耗也會產生較高的功率消耗。

就目前的技術來說,主機式GPS解決方案在追蹤模式時的MIPS消耗大約是在6MIPS甚至更低,相反地純軟體式GPS的MIPS消耗在追蹤模式時會高於12MIPS。從價格和性能的考量來說,GPS接收機和手機晶片的整合模式以主機式GPS較為可行。

干擾抑制為整合的技術瓶頸

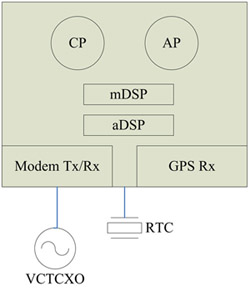

GPS接收機和手機晶片最有幾種可能的整合模式分別為單晶片、雙晶片、與三晶片架構。但隨著整合度越高,GPS接收機抗干擾的能力也越形重要。單晶片的解決方案固然是未來的趨勢,但以現在的技術要做到完全的單晶片仍有困難。其最大的挑戰在於如何克服手機對GPS接收機的干擾和共享相同的頻率源。高通(Qualcomm)在其8000系列的晶片已經能夠將CPU、手機收發機(CDMA2000系列)、GPS接收機和DSP整合成單晶片。圖6所示為系統單晶片(SoC)的架構。

|

| 圖6 單晶片方案架構圖 |

在單晶片架構下,GPS接收區塊會依照應用的不同而採用不同功能的CPU和DSP。例如智慧型手機和聯網式的PND的單晶片方案通常會內建雙CPU和雙DSP。一顆CPU是當作應用處理器(Application Processor, AP),另一顆CPU是當作通訊處理器(Communication Processor, CP)。此時GPS的位置計算是在CP上執行,AP和CP之間美國國家航海電子協會(NMEA)序列的傳輸是依靠一個虛擬的通用非同步收發傳輸器(UART)來傳輸。目前的趨勢是AP採用ARM11而CP是採用ARM9。在DSP的部分,一顆DSP是用來處理多媒體的訊號處理稱為aDSP,另一顆DSP是負責處理通訊和音頻訊號處理稱為mDSP。GPS的訊號處理原則上不會仰賴mDSP,主要是利用數位硬體來做訊號的擷取和追蹤。但純軟體的接收機須仰賴mDSP來執行訊號的擷取和追蹤。

相較之下,功能型手機(Feature Phone)的單晶片解決方案通常僅內建一顆CPU和DSP。此CPU通常為ARM9等級,主要負責手機的L1控制、通訊協定以及一些簡單的多媒體;DSP主要是負責實體層和音頻的訊號處理。因此,若要添加GPS接收功能,主機式GPS架構是最適合此種應用的架構。

雙晶片架構則以高通的gpsOne解決方案為代表。這類方案將GPS射頻和手機的收發機整合成一顆晶片並共享相同的參考頻率源,而GPS基頻和手機基頻電路製作在另一顆單晶片上(圖7)。在射頻/類比的晶片中手機的收發機和GPS接收機是分開的路徑。

|

| 圖7 雙晶片解決方案(1) |

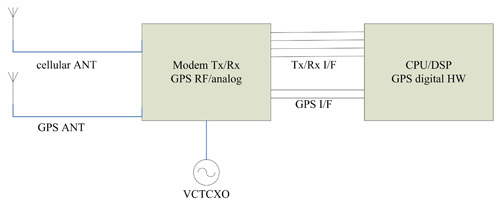

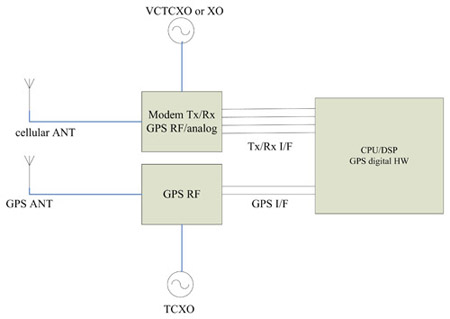

另一種雙晶片解決方案如圖8所示,將手機的收發機和所有基頻電路製作成單一晶片,只保留GPS接收機在另外一顆晶片。手機系統和GPS接收機可以選擇共享頻率源或採用不同的參考頻率源。

|

| 圖8 雙晶片解決方案(2) |

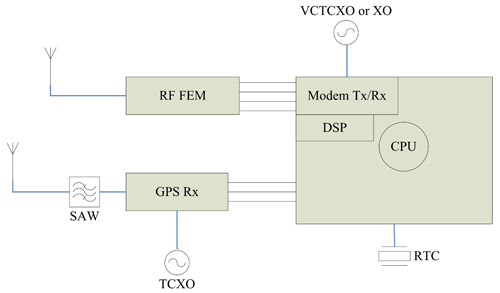

三晶片架構的GPS解決方案晶片設計的複雜度最低,抗干擾能力也最好。在三晶片架構中,GPS基頻和手機基頻電路製作成單晶片,手機的收發機和GPS射頻晶片則各自獨立。手機和GPS系統使用不同的參考頻率源以降低系統的複雜度,且GPS射頻和高功率的手機收發機分開有利於干擾防治(圖9)。

|

| 圖9 三晶片解決方案 |

基頻介面影響電路布局甚巨

在傳統的GPS接收機中,類比基頻和數位基頻之間的介面大多使用數位介面,但是高通的解決方案仍採用類比介面。採用類比介面時,在電路布局上必須格外注意,不良的布局會導致主機板上的干擾訊號耦合(Couple)至類比的基頻訊號,進而導致C/N值的降低。在此階段所產生的干擾無法透過任何的數位訊號處理技術或演算法來抑制。

在中頻部分,大多數的接收機還是採用最傳統的超低中頻(Very Low IF, VLIF)的設計,將中頻的頻率設定為C/A碼(頻率為1.023MHz)頻率的四倍(f0),也就是4.092MHz。在較新的GPS接收機的設計中已經逐漸將中頻的頻率從4.092MHz降至1.25 MHz附近(GPS L1 C/A碼是採用BPSK調變,因此主波束的零到零(Null-to-nul)l頻寬為2.046MHz),利用此種方式可以降低類比晶片和數位晶片之間資料傳送的速率。在傳統的VLIF設計中(假設ADC為2位元架構),中頻的頻率為4.092MHz且取樣頻率為16MHz(f0))時,射頻晶片和基頻晶片間的資料率為16Mbit/s。當中頻頻率降為1.25MHz時,維持四倍頻的取樣頻率只需要5MHz的取樣頻率,因此射頻IC和基頻IC間的資料率將會降低至5Mbit/s(假設ADC的位元數不變)。降低射頻晶片和基頻晶片間的資料傳輸速率可以有效的降低GPS接收機的功率消耗。

在高通的解決方案中則是採用零中頻的設計方式,直接將1,575.42MHz的GPS訊號降至基頻。必須注意的是在零中頻的架構中,類比晶片和數位晶片之間的訊號頻率不會是0,這主要是因為GPS的訊號除了有1,575.42MHz的載波之外還會有GPS衛星和接收機間因為都卜勒效應(由相對運動所產生)所造成的頻率漂移(介於-5k~5kHz之間)。